LTC4303 具阻塞总线恢复功能的可热插拔型二线式总线缓冲器

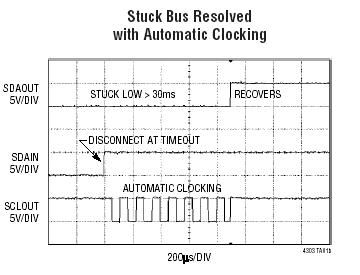

The LTC®4303 hot swappable 2-wire Bus Buffer allows I/O card insertion into a live backplane without corruption of the data and clock busses. When a connection is made, the LTC4303 provides bidirectional buffering, keeping the backplane and card capacitances isolated. If SDAOUT or SCLOUT is low for ≥ 30ms (typ), the LTC4303 automatically breaks the data and clock bus connection. At this time the LTC4303 automatically generates up to 16 clock pulses on SCLOUT in an attempt to free the bus. A connection will be enabled automatically when the bus becomes free.

Rise-time accelerator circuitry allows the use of larger pull-up resistors while still meeting rise-time requirements. During insertion, the SDA and SCL lines are precharged to 1V to minimize bus disturbances. When driven high, ENABLE allows the LTC4303 to connect after a stop bit or bus idle occurs. Driving ENABLE low breaks the connection between SDAIN and SDAOUT, SCLIN and SCLOUT. READY is an open drain output that indicates when the backplane and card sides are connected together

产品特点 Features

|

应用

典型应用图

参数 |

LTC4303 订购信息和价格参考Package Variations and Pricing

| 器件型号 | 封装 | 引脚 | 温度 | 价格 (以 1 ~ 99 片为批量) | 价格 (以 1000 片为批量) * |

| LTC4303CDD | DFN | 8 | C | $3.07 | $2.15 |

| LTC4303CDD#PBF | DFN | 8 | C | $3.07 | $2.15 |

| LTC4303CDD#TRPBF | DFN | 8 | C | $2.21 | |

| LTC4303CMS8 | MSOP | 8 | C | $3.00 | $2.10 |

| LTC4303CMS8#PBF | MSOP | 8 | C | $3.00 | $2.10 |

| LTC4303CMS8#TR | MSOP | 8 | C | $2.16 | |

| LTC4303CMS8#TRPBF | MSOP | 8 | C | $2.16 | |

| LTC4303IDD | DFN | 8 | I | $3.70 | $2.58 |

| LTC4303IDD#PBF | DFN | 8 | I | $3.70 | $2.58 |

| LTC4303IDD#TR | DFN | 8 | I | $2.64 | |

| LTC4303IDD#TRPBF | DFN | 8 | I | $2.64 | |

| LTC4303IMS8 | MSOP | 8 | I | $3.61 | $2.52 |

| LTC4303IMS8#PBF | MSOP | 8 | I | $3.61 | $2.52 |

| LTC4303IMS8#TR | MSOP | 8 | I | $2.58 | |

| LTC4303IMS8#TRPBF | MSOP | 8 | I | $2.58 |

LTC4303 数据手册及相关资料下载

- 数据手册 (英文) : LTC4303 - Hot Swappable 2-Wire Bus Buffer with Stuck Bus Recovery.PDF

- 设计要点 (中文) : DN394 - 轻而易举地通过 HDMI 符合性测试.PDF

- 可靠性数据 : R410 Reliability Data .PDF

- 产品选型卡 : I2C Muxes, Buffers & Accelerators.PDF

- 产品选型卡 : I2C Quick Guide.PDF