M48Z58 ZEROPOWER SRAM

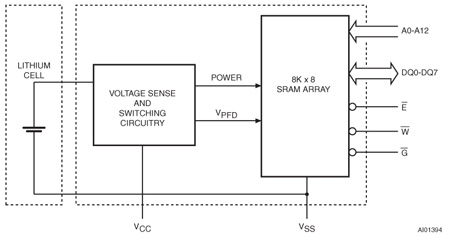

The M48Z58/Y ZEROPOWER®RAM is an 8 Kbit x 8 non-volatile static RAM that integrates power-fail deselect circuitry and battery control logic on a single die. The monolithic chip is available in two special packages to provide a highly integrated battery-backed memory solution.

The M48Z58/Y is a non-volatile pin and function equivalent to any JEDEC standard 8 K x 8 SRAM. It also easily fits into many ROM, EPROM, and EEPROM sockets, providing the non-volatility of PROMs without any requirement for special WRITE timing or limitations on the number of WRITEs that can be performed.

The 28-pin, 600 mil DIP CAPHAT™houses the M48Z58/Y silicon with a long life lithium button cell in a single package.

The 28-pin, 330 mil SOIC provides sockets with gold plated contacts at both ends for direct connection to a separate SNAPHAT®housing containing the battery. The unique design allows the SNAPHAT battery package to be mounted on top of the SOIC package after the completion of the surface mount process. Insertion of the SNAPHAT housing after reflow prevents potential battery damage due to the high temperatures required for device surface-mounting. The SNAPHAT housing is keyed to prevent reverse insertion.

The SOIC and battery packages are shipped separately in plastic anti-static tubes or in tape & reel form.

For the 28-lead SOIC, the battery package (e.g., SNAPHAT) part number is “M4Z28-BR00SH1

技术特性

|

功能框图 |

M48Z58 订购信息

| 订购型号 | 产品状态 | 美金价格 | 数量 | 封装 | 包装形式 | 温度范围 | 材料声明 |

| M48Z58-70PC1 | Active | 1000 | PDIP 28 .7 | Tube | M48Z58-70PC1 | ||

| M48Z58-100PC1 | Active | 1000 | PDIP 28 .7 | Tube | M48Z58-100PC1 |

DATASHEET

| 描述 | 版本 | 大小 |

| M48Z58 : DS0515: 5 V, 64 Kbit (8 Kbit x 8) ZEROPOWER® SRAM | 11 | 413KB |

APPLICATION NOTES

| 描述 | 版本 | 大小 |

| AN1012 : Predicting the battery life and data retention period of NVRAMs and serial RTCs | 4 | 440KB |

| AN1011 : Battery technology used in NVRAM and real-time clock (RTC) products from ST | 4 | 249KB |

| AN1009 : 'Negative undershoot' NVRAM data corruption | 1 | 34KB |