技术特性

- High performance ARM926 MCU (up to 333 MHz)

- MCU memory organization

- Cache: 16 Kbyte instruction, 16 Kbyte data

- 8 Kbyte instruction TCM (tightly coupled memory)

- 32 Kbyte embedded ROM for boot

- Two banks of 64 Kbyte embedded SRAM

- 512 Byte embedded SRAM for back-up

- 4 Gbyte total linear address space

- Memory extension through: Flexible static memory controller-FSMC (NOR/NAND Flash, CF/CF+, ROM, SRAM support) Mobile DDR/SDRAM controller: 16 bit data @166 MHz, 2 Chip Select, 512 Kbit each

- Interrupt

- 64-channel interrupt controller (VIC)

- 16-vectorized interrupts with 16 programmable priority level

- DMA

- Two 8-channel double port system DMA controllers

- 32 DMA request for each controller

- Two external DMA requests are supported

- 32-channel high performance GPS correlation embedded subsystem

- Eight 32-bit free running timers/counters

- Four 16-bit extended function timer (EFT) with input capture/output compare and PWM

- Real-time clock (RTC)

- Pulse width light modulator (PWL)

- 32-bit watchdog timer

- Four autobaud UART with 64X8 transmit and 64x12 receive FIFO with DMA and hardware flow control

- One IrDA(SIR/MIR/FIR) interface

- Three I²C multi-master/slave interfaces

- Two synchronous serial port (SSP) with 32x32 separate transmit and receive FIFO with Motorola-SPI, National-MICROWIRE and Texas- SSI support modes

- Four multichannel serial ports (MSP) with 32x8 separate transmit and receive FIFO

- Color LCD controller for STN,TFT or HR-TFT panels

- USB 2.0 OTG high speed dual role controller (ULPI interface)

- USB full speed dual role controller with integrated 1.1 physical layer transceiver

- Two secure-digital multimedia memory card interface (SD/SDIO/MMC) up to 8 bit data

- SPDIF input interface

- C3 hardware Reed-Solomon decoder

- Hardware sample rate converter (SaRaC)

- Two controller area network (CAN)

- Four 32-bit GPIO ports

- JTAG based in-circuit emulator (ICE) with embedded medium trace module

- Typical working condition: Vdd: 1.2 V ±10%, VIO: 1.8 V

- Overdrive: Vdd: 1.4 V ±5%, VIO: 1.8 V ±10%, 2.5 V ±10%

- Bus frequency: 166 MHz (overdrive)

- Bus/DDR frequency: 166 MHz

- HCMOS 0.90 μm process

- Package:

- LFBGA16x16x1.4 mm (19x19 balls)

- 0.8 mm ball pitch, (0.4 mm ball)

- Ambient temperature range: -40 / +85 °C

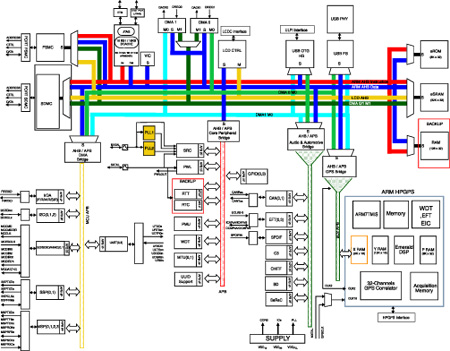

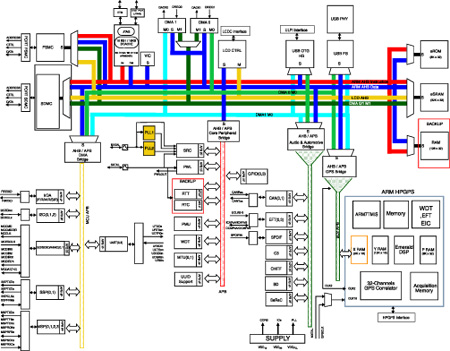

| 功能框图

|