LTC3718 - Low Input Voltage, DC/DC Controller for DDR/QDR Memory Termination

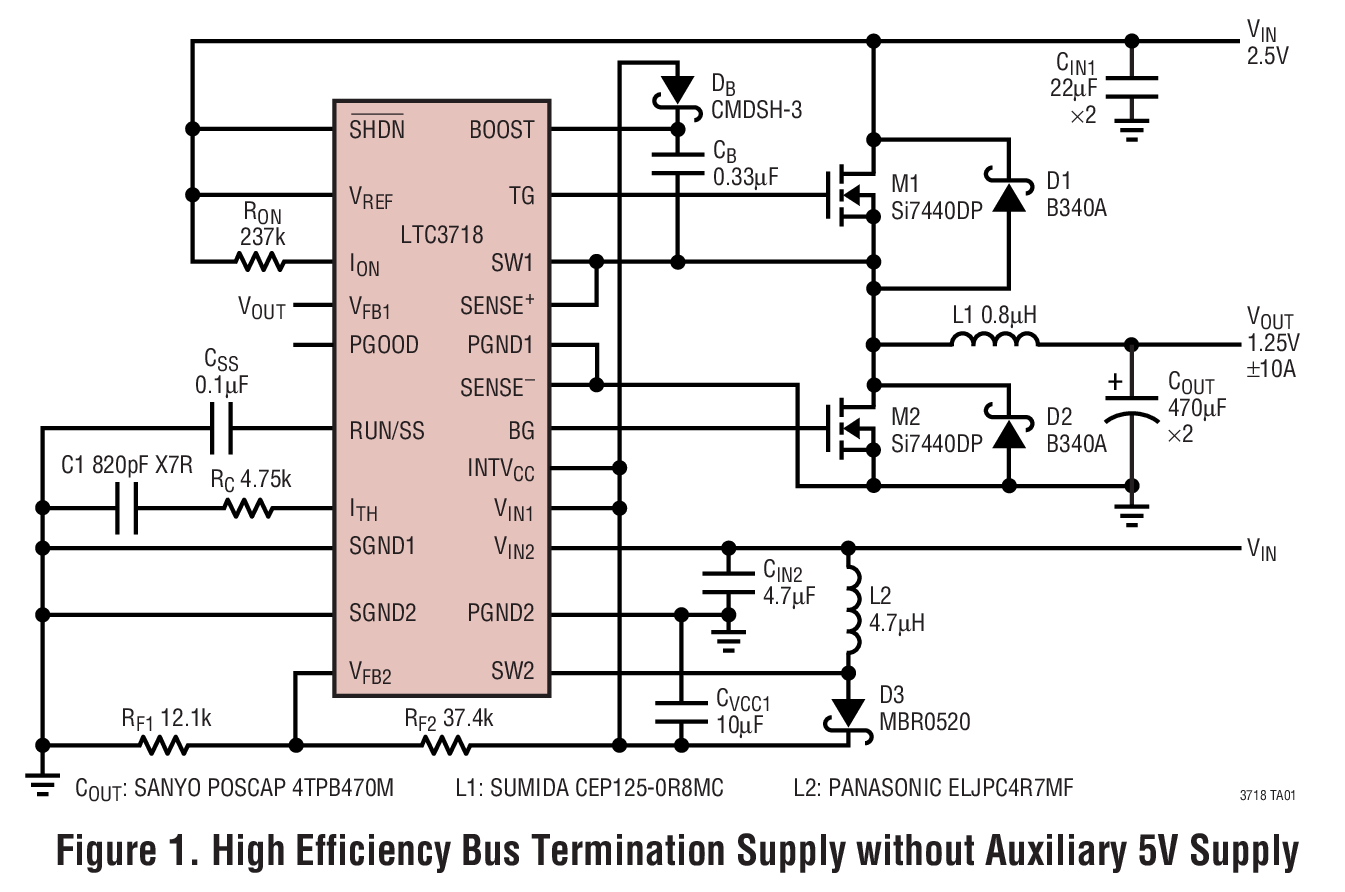

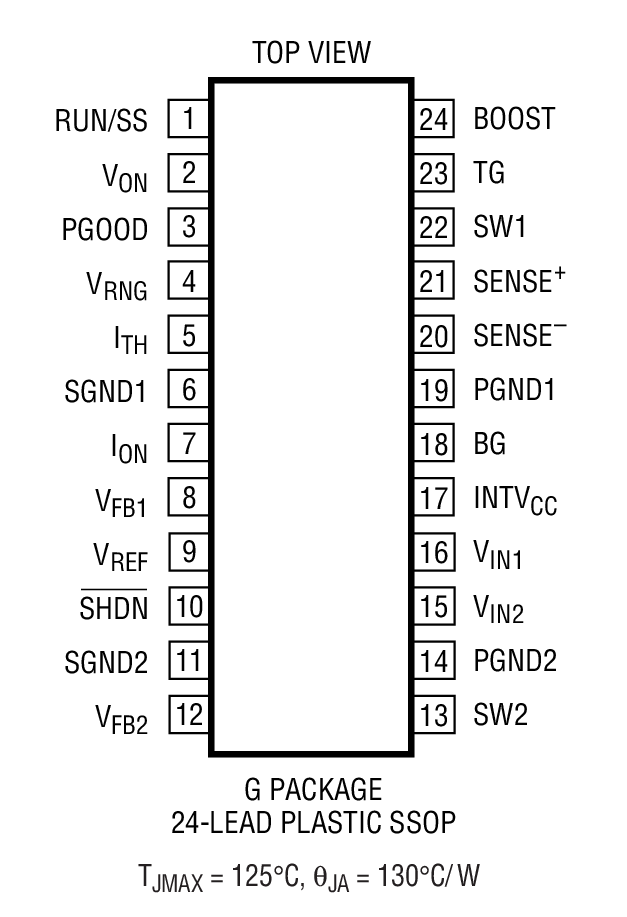

The LTC®3718 is a high current, high efficiency synchronous switching regulator controller for DDR and QDR™ memory termination. It operates from an input as low as 1.5V and provides a regulated output voltage equal to (0.5)VIN. The controller uses a valley current control architecture to enable high frequency operation with very low on-times without requiring a sense resistor. Operating frequency is selected by an external resistor and is compensated for variations in VIN and VOUT. The LTC3718 uses a pair of standard 5V logic level N-channel external MOSFETs, eliminating the need for expensive P-channel or low threshold devices.

Forced continuous operation reduces noise and RF interference. Fault protection is provided by internal foldback current limiting, an output overvoltage comparator and an optional short-circuit timer. Soft-start capability for supply sequencing can be accomplished using an external timing capacitor. OPTI-LOOP® compensation allows the transient response to be optimized over a wide range of loads and output capacitors.

OPTI-LOOP is a registered trademark of Linear Technology Corporation. No RSENSE is a trademark of Linear Technology Corporation. QDR RAMs and Quad Data Rate RAMs comprise a new family of products developed by Cypress Semiconductor, IDT and Micron Technology, Inc.

| 器件型号 | 封装 | 温度 | 价格 (以 1 ~ 99 片为批量) | 价格 (以 1000 片为批量) * |

|---|---|---|---|---|

| LTC3718EG#PBF | SSOP-24 | E | $4.91 | $3.45 |

| LTC3718EG#TRPBF | SSOP-24 | E | $3.55 |

演示电路板

| 器件型号 | 描述 | 价格 |

|---|---|---|

| DC464A | LTC3718EG | Low Input Voltage, High Current, DDR Termination Supply, 1.5-5Vin, VRef/2 @ 0-12a | 联系凌力尔特 |