# 64Mb B-die SLC NOR Specification

INFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS, AND IS SUBJECT TO CHANGE WITHOUT NOTICE.

NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE,

TO ANY INTELLECTUAL PROPERTY RIGHTS IN SAMSUNG PRODUCTS OR TECHNOLOGY. ALL INFORMATION IN THIS DOCUMENT IS PROVIDED

ON AS "AS IS" BASIS WITHOUT GUARANTEE OR WARRANTY OF ANY KIND.

- 1. For updates or additional information about Samsung products, contact your nearest Samsung office.

- 2. Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where Product failure couldresult in loss of life or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply.

<sup>\*</sup> Samsung Electronics reserves the right to change products or specification without notice.

## **Document Title**

## 64M Bit (4M x16) Muxed Burst , Multi Bank NOR Flash Memory

## **Revision History**

| Revision No. | <u>History</u>                                                                                                   | <b>Draft Date</b>  | <u>Remark</u> |

|--------------|------------------------------------------------------------------------------------------------------------------|--------------------|---------------|

| 0.0          | Initial Issue                                                                                                    | October 20, 2004   |               |

| 1.0          | Revision - Specification finalized - Add the requirement and note of Quadruple word program operation            | March 22, 2005     |               |

| 1.1          | Bottom boot block description is added                                                                           | January 09, 2006   |               |

| 1.2          | "Asynchronous mode may not support read following four sequential invalid read condition within 200ns." is added | September 08, 2006 |               |

## 64M Bit (4M x16) Muxed Burst , Multi Bank NOR Flash Memory

#### **FEATURES**

- Single Voltage, 1.7V to 1.95V for Read and Write operations

- Organization

- 4,194,304 x 16 bit ( Word Mode Only)

- Multiplexed Data and Address for reduction of interconnections

A/DQ0 ~ A/DQ15

- Read While Program/Erase Operation

- Multiple Bank Architecture

- 16 Banks (4Mb Partition)

- OTP Block : Extra 256Bvte block

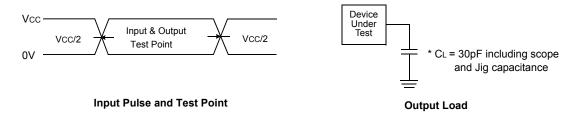

- Read Access Time (@ CL=30pF)

- Asynchronous Random Access Time : 90ns (54MHz) / 80ns (66MHz)

- Synchronous Random Access Time : 88.5ns (54MHz) / 70ns (66MHz)

- Burst Access Time :

- 14.5ns (54MHz) / 11ns (66MHz)

- Burst Length:

- Continuous Linear Burst

- Linear Burst: 8-word & 16-word with No-wrap & Wrap

- Block Architecture

- Eight 4Kword blocks and one hundreds twenty seven 32Kword blocks

- Bank 0 contains eight 4 Kword blocks and seven 32Kword blocks

- Bank 1 ~ Bank 15 contain one hundred twenty 32Kword blocks

- Reduce program time using the VPP

- Support Single & Quad word accelerate program

- Power Consumption (Typical value, CL=30pF)

- Burst Access Current: 30mA

- Program/Erase Current: 15mA

- Read While Program/Erase Current : 40mA

- Standby Mode/Auto Sleep Mode: 15uA

- Block Protection/Unprotection

- Using the software command sequence

- Last two boot blocks are protected by WP=VIL

- All blocks are protected by VPP=VIL

- · Handshaking Feature

- Provides host system with minimum latency by monitoring RDY

- Erase Suspend/Resume

- Program Suspend/Resume

- Unlock Bypass Program/Erase

- Hardware Reset (RESET)

- Data Polling and Toggle Bits

- Provides a software method of detecting the status of program or erase completion

- Endurance

- 100K Program/Erase Cycles Minimum

- Data Retention: 10 years

- Extended Temperature : -25°C ~ 85°C

- Support Common Flash Memory Interface

- Low Vcc Write Inhibit

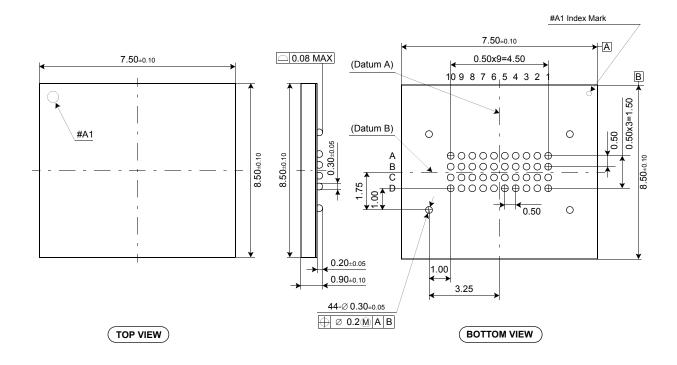

- Package: 44 ball FBGA Type, 7.5x8.5mm

0.5 mm ball pitch 1.0 mm (Max.) Thickness

#### **GENERAL DESCRIPTION**

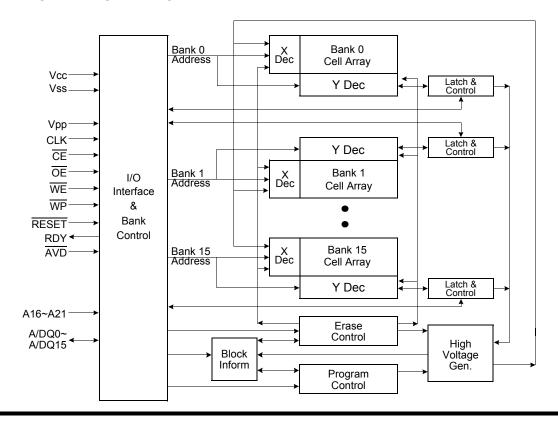

The K8S6415E featuring single 1.8V power supply is a 64Mbit Muxed Burst Multi Bank Flash Memory organized as 4Mbx16. The memory architecture of the device is designed to divide its memory arrays into 135 blocks with independent hardware protection. This block architecture provides highly flexible erase and program capability. The K8S6415E NOR Flash consists of sixteen banks. This device is capable of reading data from one bank while programming or erasing in the other bank.

Regarding read access time, the K8S6415E provides an 14.5ns burst access time and an 90ns initial access time at 54MHz. At 66MHz, the K8S6415E provides an 11ns burst access time and 70ns initial access time. The device performs a program operation in units of Single 16 bits (word) and an erase operation in units of a block. Single or multiple blocks can be erased. The block erase operation is completed within typically 0.7 sec. The device requires 15mA as program/erase current in the extended temperature ranges.

The K8S6415E NOR Flash Memory is created by using Samsung's advanced CMOS process technology. This device is available in 44 ball FBGA package.

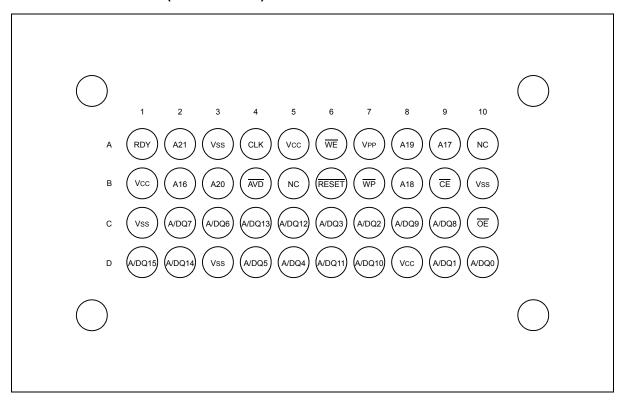

### **PIN DESCRIPTION**

| Pin Name       | Pin Function                          |  |  |  |  |

|----------------|---------------------------------------|--|--|--|--|

| A16 - A21      | Address Inputs                        |  |  |  |  |

| A/DQ0 - A/DQ15 | Multiplexed Address/Data input/output |  |  |  |  |

| CE             | Chip Enable                           |  |  |  |  |

| ŌĒ             | Output Enable                         |  |  |  |  |

| RESET          | Hardware Reset Pin                    |  |  |  |  |

| VPP            | Accelerates Programming               |  |  |  |  |

| WE             | Write Enable                          |  |  |  |  |

| WP             | Hardware Write Protection Input       |  |  |  |  |

| CLK            | Clock                                 |  |  |  |  |

| RDY            | Ready Output                          |  |  |  |  |

| AVD            | Address Valid Input                   |  |  |  |  |

| Vcc            | Power Supply                          |  |  |  |  |

| Vss            | Ground                                |  |  |  |  |

SAMSUNG ELECTRONICS CO., LTD. reserves the right to change products and specifications without notice.

## 44 Ball FBGA TOP VIEW (BALL DOWN)

### **FUNCTIONAL BLOCK DIAGRAM**

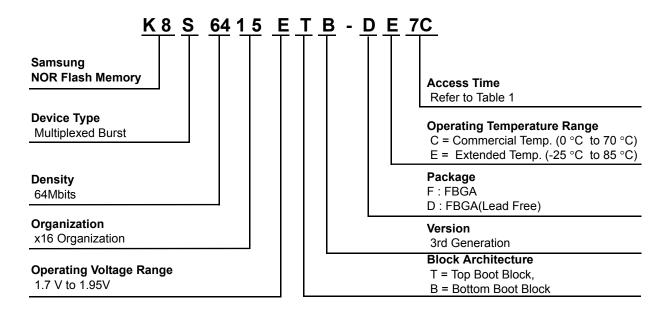

## **ORDERING INFORMATION**

**Table 1. PRODUCT LINE-UP**

|                | K8S6415E                            |               |               |                              |               |               |  |  |

|----------------|-------------------------------------|---------------|---------------|------------------------------|---------------|---------------|--|--|

|                | Synchronous/E                       | Burst         | Asynchronous  |                              |               |               |  |  |

|                | Speed Option                        | 7B<br>(54MHz) | 7C<br>(66MHz) | Speed Option                 | 7B<br>(54MHz) | 7C<br>(66MHz) |  |  |

|                | Max. Initial Access Time (tIAA, ns) | 88.5          | 70            | Max Access Time (taa, ns)    | 90            | 80            |  |  |

| Vcc=1.7V-1.95V | Max. Burst Access Time (tba, ns)    | 14.5          | 11            | Max CE Access Time (tce, ns) | 90            | 80            |  |  |

|                | Max. OE Access Time (toe, ns)       | 20            | 20            | Max OE Access Time (toe, ns) | 20            | 20            |  |  |

Table 2. K8S6415E DEVICE BANK DIVISIONS

|        | Bank 0                           | Bank 1 ~ Bank 15 |                                |  |

|--------|----------------------------------|------------------|--------------------------------|--|

| Mbit   | Block Sizes                      | Mbit             | Block Sizes                    |  |

| 4 Mbit | Eight 4Kwords,<br>Seven 32Kwords | 60 Mbit          | One hundred<br>twenty 32Kwords |  |

## **NOR FLASH MEMORY**

Table 3. Block Address Table

| Bank   | Block | Block Size | (x16) Address Range |

|--------|-------|------------|---------------------|

|        | BA134 | 4 Kwords   | 3FF000h-3FFFFFh     |

|        | BA133 | 4 Kwords   | 3FE000h-3FEFFFh     |

|        | BA132 | 4 Kwords   | 3FD000h-3FDFFFh     |

|        | BA131 | 4 Kwords   | 3FC000h-3FCFFFh     |

|        | BA130 | 4 Kwords   | 3FB000h-3FBFFFh     |

|        | BA129 | 4 Kwords   | 3FA000h-3FAFFFh     |

|        | BA128 | 4 Kwords   | 3F9000h-3F9FFFh     |

| Bank0  | BA127 | 4 Kwords   | 3F8000h-3F8FFFh     |

|        | BA126 | 32 Kwords  | 3F0000h-3F7FFFh     |

|        | BA125 | 32 Kwords  | 3E8000h-3EFFFFh     |

|        | BA124 | 32 Kwords  | 3E0000h-3E7FFFh     |

|        | BA123 | 32 Kwords  | 3D8000h-3DFFFFh     |

|        | BA122 | 32 Kwords  | 3D0000h-3D7FFFh     |

|        | BA121 | 32 Kwords  | 3C8000h-3CFFFFh     |

|        | BA120 | 32 Kwords  | 3C0000h-3C7FFFh     |

|        | BA119 | 32 Kwords  | 3B8000h-3BFFFFh     |

|        | BA118 | 32 Kwords  | 3B0000h-3B7FFFh     |

|        | BA117 | 32 Kwords  | 3A8000h-3AFFFFh     |

| David  | BA116 | 32 Kwords  | 3A0000h-3A7FFFh     |

| Bank1  | BA115 | 32 Kwords  | 398000h-39FFFFh     |

|        | BA114 | 32 Kwords  | 390000h-397FFFh     |

|        | BA113 | 32 Kwords  | 388000h-38FFFFh     |

|        | BA112 | 32 Kwords  | 380000h-387FFFh     |

|        | BA111 | 32 Kwords  | 378000h-37FFFFh     |

|        | BA110 | 32 Kwords  | 370000h-377FFFh     |

|        | BA109 | 32 Kwords  | 368000h-36FFFFh     |

| Bank2  | BA108 | 32 Kwords  | 360000h-367FFFh     |

| Dankz  | BA107 | 32 Kwords  | 358000h-35FFFFh     |

|        | BA106 | 32 Kwords  | 350000h-357FFFh     |

|        | BA105 | 32 Kwords  | 348000h-34FFFFh     |

|        | BA104 | 32 Kwords  | 340000h-347FFFh     |

|        | BA103 | 32 Kwords  | 338000h-33FFFFh     |

|        | BA102 | 32 Kwords  | 330000h-337FFFh     |

|        | BA101 | 32 Kwords  | 328000h-32FFFFh     |

| Bank3  | BA100 | 32 Kwords  | 320000h-327FFFh     |

| Barino | BA99  | 32 Kwords  | 318000h-31FFFFh     |

|        | BA98  | 32 Kwords  | 310000h-317FFFh     |

|        | BA97  | 32 Kwords  | 308000h-30FFFFh     |

|        | BA96  | 32 Kwords  | 300000h-307FFFh     |

|        | BA95  | 32 Kwords  | 2F8000h-2FFFFFh     |

|        | BA94  | 32 Kwords  | 2F0000h-2F7FFFh     |

|        | BA93  | 32 Kwords  | 2E8000h-2EFFFFh     |

| Bank4  | BA92  | 32 Kwords  | 2E0000h-2E7FFFh     |

| Dankt  | BA91  | 32 Kwords  | 2D8000h-2DFFFFh     |

|        | BA90  | 32 Kwords  | 2D0000h-2D7FFFh     |

|        | BA89  | 32 Kwords  | 2C8000h-2CFFFFh     |

|        | BA88  | 32 Kwords  | 2C0000h-2C7FFFh     |

**Table 3. Block Address Table (Continued)**

| Bank                                             | Block | Block Size | (x16) Address Range |

|--------------------------------------------------|-------|------------|---------------------|

|                                                  | BA87  | 32 Kwords  | 2B8000h-2BFFFFh     |

|                                                  | BA86  | 32 Kwords  | 2B0000h-2B7FFFh     |

|                                                  | BA85  | 32 Kwords  | 2A8000h-2AFFFFh     |

| D15                                              | BA84  | 32 Kwords  | 2A0000h-2A7FFh      |

| Bank5                                            | BA83  | 32 Kwords  | 298000h-29FFFFh     |

|                                                  | BA82  | 32 Kwords  | 290000h-297FFFh     |

|                                                  | BA81  | 32 Kwords  | 288000h-28FFFFh     |

|                                                  | BA80  | 32 Kwords  | 280000h-287FFFh     |

|                                                  | BA79  | 32 Kwords  | 278000h-27FFFFh     |

|                                                  | BA78  | 32 Kwords  | 270000h-277FFFh     |

|                                                  | BA77  | 32 Kwords  | 268000h-26FFFFh     |

|                                                  | BA76  | 32 Kwords  | 260000h-267FFh      |

| Bank6                                            | BA75  | 32 Kwords  | 258000h-25FFFFh     |

|                                                  | BA74  | 32 Kwords  | 250000h-257FFFh     |

|                                                  | BA73  | 32 Kwords  | 248000h-24FFFFh     |

| <del>-</del>                                     | BA72  | 32 Kwords  | 240000h-247FFFh     |

|                                                  | BA71  | 32 Kwords  | 238000h-23FFFFh     |

| <del>-</del>                                     | BA70  | 32 Kwords  | 230000h-237FFFh     |

| <del> </del>                                     | BA69  | 32 Kwords  | 228000h-22FFFFh     |

| <del>                                     </del> | BA68  | 32 Kwords  | 220000h-227FFFh     |

| Bank7                                            | BA67  | 32 Kwords  | 218000h-21FFFFh     |

| <del>                                     </del> | BA66  | 32 Kwords  | 210000h-217FFFh     |

| <del>                                     </del> | BA65  | 32 Kwords  | 208000h-20FFFFh     |

| <u> </u>                                         | BA64  | 32 Kwords  | 200000h-207FFFh     |

|                                                  | BA63  | 32 Kwords  | 1F8000h-1FFFFh      |

| <del>                                     </del> | BA62  | 32 Kwords  | 1F0000h-1F7FFFh     |

| <u> </u>                                         | BA61  | 32 Kwords  | 1E8000h-1EFFFFh     |

| <u> </u>                                         | BA60  | 32 Kwords  | 1E0000h-1E7FFh      |

| Bank8                                            | BA59  | 32 Kwords  | 1D8000h-1DFFFFh     |

| <del>                                     </del> | BA58  | 32 Kwords  | 1D0000h-1D7FFFh     |

| <del>                                     </del> | BA57  | 32 Kwords  | 1C8000h-1CFFFh      |

| <del>                                     </del> | BA56  | 32 Kwords  | 1C0000h-1C7FFFh     |

|                                                  | BA55  | 32 Kwords  | 1B8000h-1BFFFFh     |

| -                                                | BA54  | 32 Kwords  | 1B0000h-1B7FFFh     |

| <del> </del>                                     | BA53  | 32 Kwords  | 1A8000h-1AFFFFh     |

| <del> </del>                                     | BA52  | 32 Kwords  | 1A0000h-1A7FFFh     |

| Bank9                                            | BA51  | 32 Kwords  | 198000h-19FFFh      |

| <del>                                     </del> | BA50  | 32 Kwords  | 190000h-197FFh      |

| <del>                                     </del> | BA49  | 32 Kwords  | 188000h-18FFFFh     |

| <del>                                   </del>   | BA48  | 32 Kwords  | 180000h-187FFFh     |

|                                                  | BA47  | 32 Kwords  | 178000h-17FFFh      |

| <del>                                   </del>   | BA46  | 32 Kwords  | 170000h-177FFFh     |

|                                                  |       |            |                     |

| Bank10                                           | BA45  | 32 Kwords  | 168000h-16FFFFh     |

| <u> </u>                                         | BA44  | 32 Kwarda  | 160000h-167FFFh     |

|                                                  | BA43  | 32 Kwords  | 158000h-15FFFFh     |

|                                                  | BA42  | 32 Kwords  | 150000h-157FFFh     |

## **NOR FLASH MEMORY**

Table 3. Block Address Table (Continued)

| Bank   | Block | Block Size | (x16) Address Range |

|--------|-------|------------|---------------------|

| Bank10 | BA41  | 32 Kwords  | 148000h-14FFFFh     |

| Bankiu | BA40  | 32 Kwords  | 140000h-147FFFh     |

|        | BA39  | 32 Kwords  | 138000h-13FFFFh     |

|        | BA38  | 32 Kwords  | 130000h-137FFFh     |

|        | BA37  | 32 Kwords  | 128000h-12FFFFh     |

| D1-44  | BA36  | 32 Kwords  | 120000h-127FFFh     |

| Bank11 | BA35  | 32 Kwords  | 118000h-11FFFFh     |

|        | BA34  | 32 Kwords  | 110000h-117FFFh     |

|        | BA33  | 32 Kwords  | 108000h-10FFFFh     |

|        | BA32  | 32 Kwords  | 100000h-107FFFh     |

|        | BA31  | 32 Kwords  | 0F8000h-0FFFFh      |

|        | BA30  | 32 Kwords  | 0F0000h-0F7FFh      |

|        | BA29  | 32 Kwords  | 0E8000h-0EFFFFh     |

| Ponk12 | BA28  | 32 Kwords  | 0E0000h-0E7FFh      |

| Bank12 | BA27  | 32 Kwords  | 0D8000h-0DFFFFh     |

|        | BA26  | 32 Kwords  | 0D0000h-0D7FFFh     |

|        | BA25  | 32 Kwords  | 0C8000h-0CFFFFh     |

|        | BA24  | 32 Kwords  | 0C0000h-0C7FFFh     |

|        | BA23  | 32 Kwords  | 0B8000h-0BFFFFh     |

|        | BA21  | 32 Kwords  | 0B0000h-0B7FFFh     |

|        | BA21  | 32 Kwords  | 0A8000h-0AFFFFh     |

| Donk12 | BA20  | 32 Kwords  | 0A0000h-0A7FFFh     |

| Bank13 | BA19  | 32 Kwords  | 098000h-09FFFh      |

|        | BA18  | 32 Kwords  | 090000h-097FFh      |

|        | BA17  | 32 Kwords  | 088000h-08FFFFh     |

|        | BA16  | 32 Kwords  | 080000h-087FFh      |

|        | BA15  | 32 Kwords  | 078000h-07FFFFh     |

|        | BA14  | 32 Kwords  | 070000h-077FFFh     |

|        | BA13  | 32 Kwords  | 068000h-06FFFFh     |

| Donk14 | BA12  | 32 Kwords  | 060000h-067FFFh     |

| Bank14 | BA11  | 32 Kwords  | 058000h-05FFFFh     |

|        | BA10  | 32 Kwords  | 050000h-057FFFh     |

|        | BA9   | 32 Kwords  | 048000h-04FFFFh     |

|        | BA8   | 32 Kwords  | 040000h-047FFFh     |

|        | BA7   | 32 Kwords  | 038000h-03FFFFh     |

|        | BA6   | 32 Kwords  | 030000h-037FFFh     |

|        | BA5   | 32 Kwords  | 028000h-02FFFFh     |

| Rank15 | BA4   | 32 Kwords  | 020000h-027FFFh     |

| Bank15 | BA3   | 32 Kwords  | 018000h-01FFFFh     |

|        | BA2   | 32 Kwords  | 010000h-017FFFh     |

|        | BA1   | 32 Kwords  | 008000h-00FFFh      |

|        | BA0   | 32 Kwords  | 000000h-007FFh      |

Table 3-1. OTP Block Addresses

| ОТР | Block Address<br>A21 ~ A8 | Block Size | (x16) Address Range |

|-----|---------------------------|------------|---------------------|

|     | 7FFFh                     | 128words   | 3FFF80h-3FFFFFh     |

After entering OTP block, any issued addresses should be in the range of OTP block address

### PRODUCT INTRODUCTION

The K8S6415E is an 64Mbit (67,108,364 bits) NOR-type Burst Flash memory. The device features 1.8V single voltage power supply operating within the range of 1.7V to 1.95V. The device is programmed by using the Channel Hot Electron (CHE) injection mechanism which is used to program EPROMs. The device is erased electrically by using Fowler-Nordheim tunneling mechanism. To provide highly flexible erase and program capability, the device adapts a block memory architecture that divides its memory array into 135 blocks (32-Kword x 127, 4-Kword x 8, ). Programming is done in units of 16 bits (Word). All bits of data in one or multiple blocks can be erased when the device executes the erase operation. To prevent the device from accidental erasing or over-writing the programmed data, 135 memory blocks can be hardware protected. Regarding read access time, at 54MHz, the K8S6415E provides a burst access of 14.5ns with initial access times of 90ns at 30pF. At 66MHz, the K8S6415E provides a burst access of 11ns with initial access times of 70ns at 30pF. The command set of K8S6415E is compatible with standard Flash devices. The device uses Chip Enable  $(\overline{CE})$ , Write Enable  $(\overline{WE})$ , Address Valid $(\overline{AVD})$  and Output Enable  $(\overline{OE})$  to control asynchronous read and write operation. For burst operations, the device additionally requires Ready (RDY) and Clock (CLK). Device operations are executed by selective command codes. The command codes to be combined with addresses and data are sequentially written to the command registers using microprocessor write timing. The command codes serve as inputs to an internal state machine which controls the program/erase circuitry. Register contents also internally latch addresses and data necessary to execute the program and erase operations. The K8S6415E is implemented with Internal Program/Erase Routines to execute the program/erase operations. The Internal Program/ Erase Routines are invoked by program/erase command sequences. The Internal Program Routine automatically programs and verifies data at specified address. The Internal Erase Routine automatically pre-programs the memory cell which is not programmed and then executes the erase operation. The K8S6415E has means to indicate the status of completion of program/erase operations. The status can be indicated via Data polling of DQ7, or the Toggle bit (DQ6). Once the operations have been completed, the device automatically resets itself to the read mode. The device requires only 25 mA as burst and asynchronous mode read current and 15 mA for program/erase operations.

**Table 4. Device Bus Operations**

| Operation                                                            | CE | OE | WE | A16-21 | A/DQ0-15        | RESET | CLK | AVD |

|----------------------------------------------------------------------|----|----|----|--------|-----------------|-------|-----|-----|

| Asynchronous Read Operation                                          | L  | L  | Н  | Add In | Add In/<br>Dout | Н     | L   | L   |

| Write                                                                | L  | Н  |    | Add In | Add In / DIN    | Н     | L   | Х   |

| Standby                                                              | Н  | Х  | х  | х      | High-Z          | Н     | Х   | Х   |

| Hardware Reset                                                       | х  | х  | х  | х      | High-Z          | L     | Х   | Х   |

| Load Initial Burst Address                                           | L  | Н  | Н  | Add In | Add In          | Н     |     |     |

| Burst Read Operation                                                 | L  | L  | Н  | Х      | Burst<br>Dout   | Н     |     | Н   |

| Terminate Burst Read Cycle via CE                                    | Н  | Х  | Х  | X      | High-Z          | Н     | Х   | Х   |

| Terminate Burst Read Cycle via RESET                                 | х  | х  | х  | Х      | High-Z          | L     | Х   | Х   |

| Terminate Current Burst Read Cycle and Start<br>New Burst Read Cycle | L  | Н  | Н  | Add In | Add In          | Н     |     |     |

Note: L=VIL (Low), H=VIH (High), X=Don't Care.

## **COMMAND DEFINITIONS**

The K8S6415E operates by selecting and executing its operational modes. Each operational mode has its own command set. In order to select a certain mode, a proper command with specific address and data sequences must be written into the command register. Writing incorrect information which include address and data or writing an improper command will reset the device to the read mode. The defined valid register command sequences are stated in Table 5.

**Table 5. Command Sequences**

| Command Definitions                       |      | Cycle | 1st Cycle | 2nd Cycle | 3rd Cycle | 4th Cycle | 5th Cycle | 6th Cycle |

|-------------------------------------------|------|-------|-----------|-----------|-----------|-----------|-----------|-----------|

|                                           | Add  |       | RA        |           |           |           |           |           |

| Asynchronous Read                         | Data | 1     | RD        |           |           |           |           |           |

|                                           | Add  | ,     | XXXH      |           |           |           |           |           |

| Reset(Note 5)                             | Data | 1     | F0H       |           |           |           |           |           |

| Autoselect                                | Add  |       | 555H      | 2AAH      | (DA)555H  | (DA)X00H  |           |           |

| Manufacturer ID(Note 6)                   | Data | 4     | AAH       | 55H       | 90H       | ECH       |           |           |

| Autoselect                                | Add  |       | 555H      | 2AAH      | (DA)555H  | (DA)X01H  |           |           |

| Device ID(Note 6)                         | Data | 4     | AAH       | 55H       | 90H       | Note6     |           |           |

| Autoselect                                | Add  | 4     | 555H      | 2AAH      | (BA)555H  | (BA)X02H  |           |           |

| Block Protection Verify(Note 7)           | Data | 4     | AAH       | 55H       | 90H       | 00H/01H   |           |           |

| Des succes                                | Add  | 4     | 555H      | 2AAH      | 555H      | PA        |           |           |

| Program                                   | Data | 4     | AAH       | 55H       | A0H       | PD        |           |           |

| Halad Barra                               | Add  |       | 555H      | 2AAH      | 555H      |           |           |           |

| Unlock Bypass                             | Data | 3     | AAH       | 55H       | 20H       |           |           |           |

| Liniada Dunasa Dragram/Nata (I)           | Add  | 2     | XXX       | PA        |           |           |           |           |

| Unlock Bypass Program(Note 8)             | Data |       | A0H       | PD        |           |           |           |           |

| Halad B Blad Face (Note 2)                | Add  | 2     | XXX       | BA        |           |           |           |           |

| Unlock Bypass Block Erase(Note 8)         | Data |       | 80H       | 30H       |           |           |           |           |

| Liniari, Dungan Chin Ernan (Nota 9)       | Add  |       | XXXH      | XXXH      |           |           |           |           |

| Unlock Bypass Chip Erase(Note 8)          | Data | 2     | 80H       | 10H       |           |           |           |           |

| Halaak Dimasa Dasat                       | Add  | 2     | XXXH      | XXXH      |           |           |           |           |

| Unlock Bypass Reset                       | Data | 2     | 90H       | 00H       |           |           |           |           |

| Quadruple word Accelerated Program(Note9) | Add  | 5     | XXX       | PA1       | PA2       | PA3       | PA4       |           |

| Quadruple word Accelerated Program(Notes) | Data | 5     | A5H       | PD1       | PD2       | PD3       | PD4       |           |

| Chin France                               | Add  | 6     | 555H      | 2AAH      | 555H      | 555H      | 2AAH      | 555H      |

| Chip Erase                                | Data | 6     | AAH       | 55H       | 80H       | AAH       | 55H       | 10H       |

| Block Erase                               | Add  | 6     | 555H      | 2AAH      | 555H      | 555H      | 2AAH      | BA        |

| DIOCK Elase                               | Data | 0     | AAH       | 55H       | 80H       | AAH       | 55H       | 30H       |

| Erase Suspend (Note 10)                   | Add  | 1     | (DA)XXXH  |           |           |           |           |           |

| Liase Suspenu (Note 10)                   | Data | '     | вон       |           |           |           |           |           |

| Erana Basuma (Nota 11)                    | Add  | 1     | (DA)XXXH  |           |           |           |           |           |

| Erase Resume (Note 11)                    | Data | '     | 30H       |           |           |           |           |           |

| Program Suspend (Note12)                  | Add  | 1     | (DA)XXXH  |           |           |           |           |           |

| i rogram Suspenu (Note12)                 | Data | '     | вон       |           |           |           |           |           |

| Program Resume (Note11)                   | Add  | 1     | (DA)XXXH  |           |           |           |           |           |

| i iogiaili Nesullie (Note II)             | Data | '     | 30H       |           |           |           |           |           |

## NOR FLASH MEMORY

### **Table 5. Command Sequences (Continued)**

| Command Definitions                             |      |     | 1st Cycle | 2nd Cycle | 3rd Cycle | 4th Cycle | 5th Cycle | 6th Cycle |

|-------------------------------------------------|------|-----|-----------|-----------|-----------|-----------|-----------|-----------|

| Block Protection/Unprotection (Note 13)         | Add  | 3   | XXX       | XXX       | ABP       |           |           |           |

| Block Protection/Onprotection (Note 13)         | Data | 3   | 60H       | 60H       | 60H       |           |           |           |

| CEL Query (Note 14)                             | Add  | 1   | (DA)X55H  |           |           |           |           |           |

| CFI Query (Note 14)                             | Data | ] ! | 98H       |           |           |           |           |           |

| Set Burst Mode Configuration Register (Note 15) | Add  |     | 555H      | 2AAH      | (CR)555H  |           |           |           |

| Set Burst Mode Configuration Register (Note 15) | Data | 3   | AAH       | 55H       | C0H       |           |           |           |

| Enter OTP Block Region                          | Addr | 3   | 555H      | 2AAH      | 555H      |           |           |           |

| Effet OTF block Region                          | Data | 3   | AAH       | 55H       | 70H       |           |           |           |

| Suit OTD Block Donies                           | Addr | 4   | 555H      | 2AAH      | 555H      | XXX       |           |           |

| Exit OTP Block Region                           | Data | 4   | AAH       | 55H       | 75H       | 00H       |           |           |

- 1. RA: Read Address, PA: Program Address, RD: Read Data, PD: Program Data, BA: Block Address (A21 ~ A12)

DA: Bank Address (A21 ~ A18), ABP: Address of the block to be protected or unprotected, CR: Configuration Register Setting

- 2. The 4th cycle data of autoselect mode and RD are output data. The others are input data.

- 3. Data bits DQ15-DQ8 are don't care in command sequences, except for RD, PD and Device ID.

- 4. Unless otherwise noted, address bits A21 ~ A11 are don't cares.

- 5. The reset command is required to return to read mode.

- If a bank entered the autoselect mode during the erase suspend mode, writing the reset command returns that bank to the erase suspend mode. If a bank entered the autoselect mode during the program suspend mode, writing the reset command returns that bank to the program suspend mode. If DQ5 goes high during the program or erase operation, writing the reset command returns that bank to read mode or erase suspend mode if that bank was in erase suspend mode.

- 6. The 3rd and 4th cycle bank address of autoselect mode must be same.

- Device ID Data: "2250H" for Top Boot Block Device, "2251H" for Bottom Boot Block Device

- 7. Normal Block Protection Verify: 00H for an unprotected block and 01H for a protected block.

- OTP Block Protect verify (with OTP Block Address after Entering OTP Block): 00H for unlocked, and 01H for locked.

- 8. The unlock bypass command sequence is required prior to this command sequence.

- Quadruple word accelerated program is invoked only at Vpp=Vip ,Vpp setup is required prior to this command sequence.

PA1, PA2, PA3, PA4 have the same A21~A2 address.

- 10. The system may read and program in non-erasing blocks when in the erase suspend mode.

- The system may enter the autoselect mode when in the erase suspend mode.

- The erase suspend command is valid only during a block erase operation, and requires the bank address.

- 11. The erase/program resume command is valid only during the erase/program suspend mode, and requires the bank address.

- 12. This mode is used only to enable Data Read by suspending the Program operation.

- 13. Set block address(BA) as either A6 = VIH, A1 = VIH and A0 = VIL for unprotected or A6 = VIL, A1 = VIH and A0 = VIL for protected.

- 14. Command is valid when the device is in Read mode or Autoselect mode.

- 15. See "Set Burst Mode Congiguration Register" for details.

## **NOR FLASH MEMORY**

## K8S6415ET(B)B

### **DEVICE OPERATION**

The device has I/Os that accept both address and data information. To write a command or command sequence (which includes programming data to the device and erasing blocks of memory), the system must drive CLK,  $\overline{\text{AVD}}$  and  $\overline{\text{CE}}$  to VIL and  $\overline{\text{OE}}$  to VIH when providing an address to the device, and drive CLK,  $\overline{\text{WE}}$  and  $\overline{\text{CE}}$  to VIL and  $\overline{\text{OE}}$  to VIH when writing commands or data.

The device provide the unlock bypass mode to save its program time for program operation. Unlike the standard program command sequence which is comprised of four bus cycles, only two program cycles are required to program a word in the unlock bypass mode. One block, multiple blocks, or the entire device can be erased. Table 3 indicates the address space that each block occupies. The device's address space is divided into sixteen banks: Bank 0 contains the boot/parameter blocks, and the other banks(from Bank 1 to 15) consist of uniform blocks. A "bank address" is the address bits required to uniquely select a bank. Similarly, a "block address" is the address bits required to uniquely select a block. Icc2 in the DC Characteristics table represents the active current specification for the write mode. The AC Characteristics section contains timing specification tables and timing diagrams for write operations.

#### Read Mode

The device automatically enters to asynchronous read mode after device power-up. No commands are required to retrieve data in asynchronous mode. After completing an Internal Program/Erase Routine, each bank is ready to read array data. The reset command is required to return a bank to the read(or erase-suspend-read)mode if DQ5 goes high during an active program/erase operation, or if the bank is in the autoselect mode.

The synchronous(burst) mode will **automatically** be enabled on the first rising edge on the CLK input while  $\overline{\text{AVD}}$  is held low. That means device enters burst read mode from asynchronous read mode to burst read mode using CLK and  $\overline{\text{AVD}}$  signal. When the burst read is finished(or terminated), the device return to asynchronous read mode automatically.

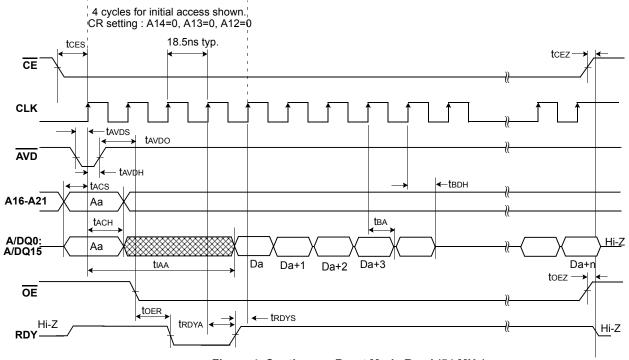

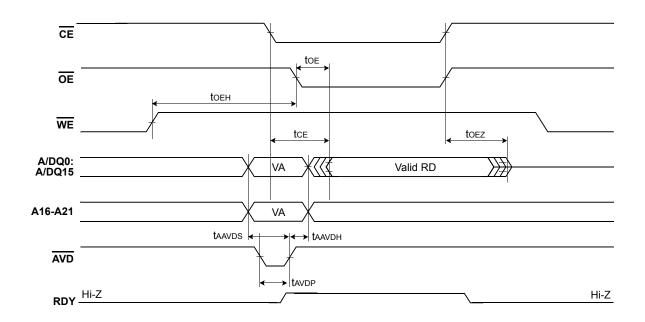

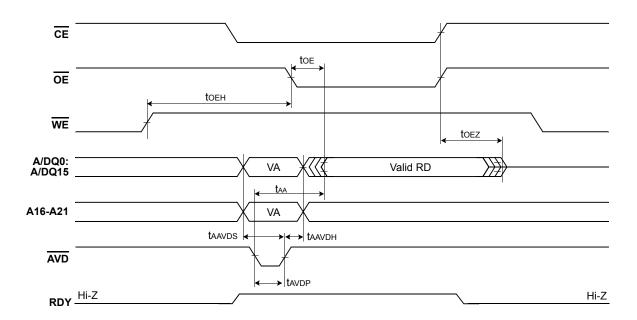

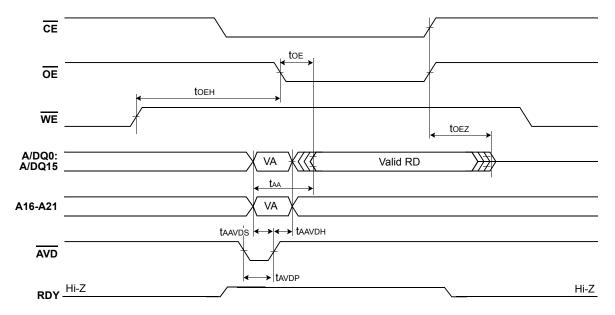

### **Asynchronous Read Mode**

For the asynchronous read mode a valid address should be asserted on A/DQ0-A/DQ15 and A16-A21, while driving  $\overline{\text{AVD}}$  and  $\overline{\text{CE}}$  to  $\overline{\text{VIL}}$ .  $\overline{\text{WE}}$  should remain at  $\overline{\text{VIH}}$ . Note that  $\overline{\text{CLK}}$  must remain low for asynchronous read mode. The address is latched at the rising edge of  $\overline{\text{AVD}}$ , and then the system can drive  $\overline{\text{OE}}$  to  $\overline{\text{VIL}}$ . The data will appear on A/DQ0-A/DQ15. Since the memory array is divided into sixteen banks, each bank remains enabled for read access until the command register contents are altered.

Address access time (tAA) is equal to the delay from valid addresses to valid output data. The chip enable access time(tCE) is the delay from the falling edge of  $\overline{\text{CE}}$  to valid data at the outputs. The output enable access time(tOE) is the delay from the falling edge of  $\overline{\text{OE}}$  to valid data at the output. The asynchronous access time is measured from a valid address, falling edge of  $\overline{\text{AVD}}$  or falling edge of  $\overline{\text{CE}}$  whichever occurs last. To prevent the memory content from spurious altering during power transition, the initial state machine is set for reading array data upon device power-up, or after a hardware reset.

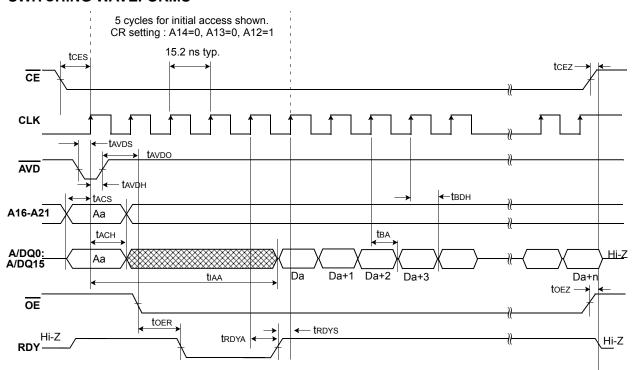

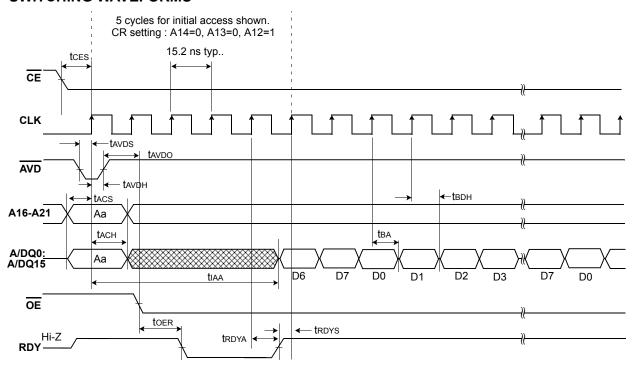

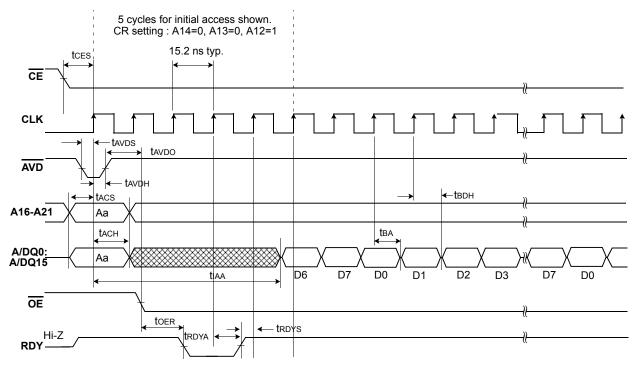

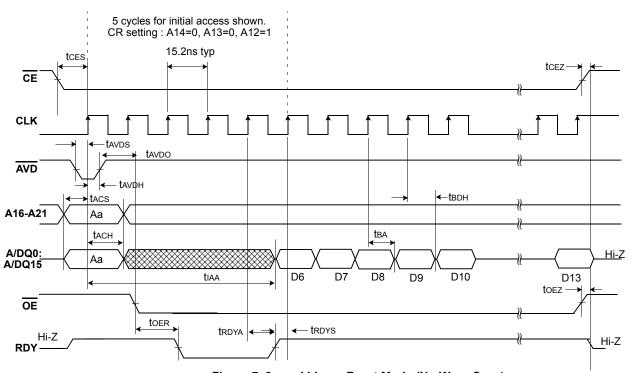

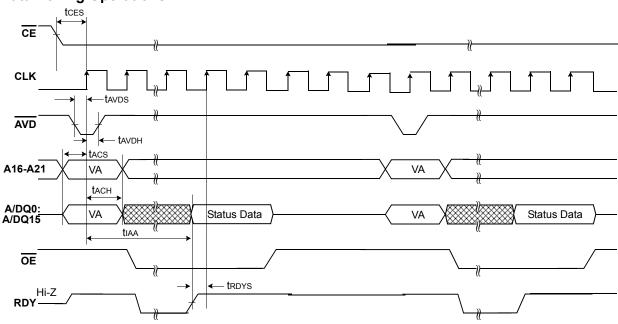

#### Synchronous (Burst) Read Mode

The device is capable of continuous linear burst operation and linear burst operation of a preset length. For the burst mode, the system should determine how many clock cycles are desired for the initial word(tiAA) of each burst access and what mode of burst operation is desired using "Burst Mode Configuration Register" command sequences. See "Set Burst Mode Configuration" for further details. The status data also can be read during burst read mode by using  $\overline{\text{AVD}}$  signal with a bank address. To initiate the synchronous read again, a new address and  $\overline{\text{AVD}}$  pulse is needed after the host has completed status reads or the device has completed the program or erase operation.

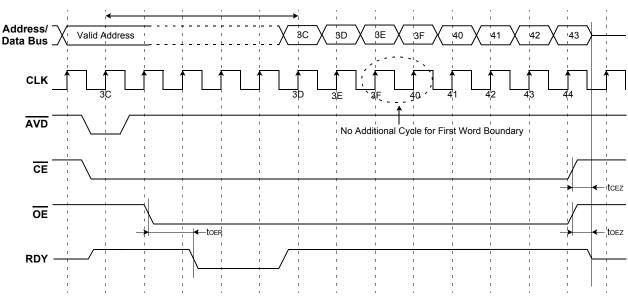

#### **Continuous Linear Burst Read**

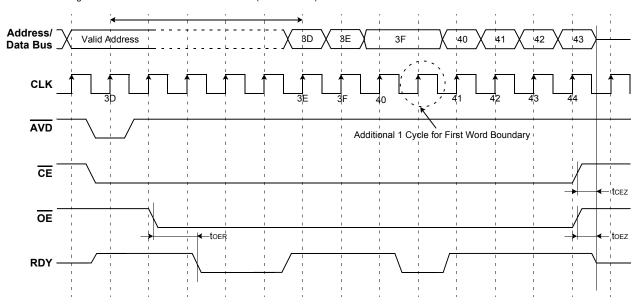

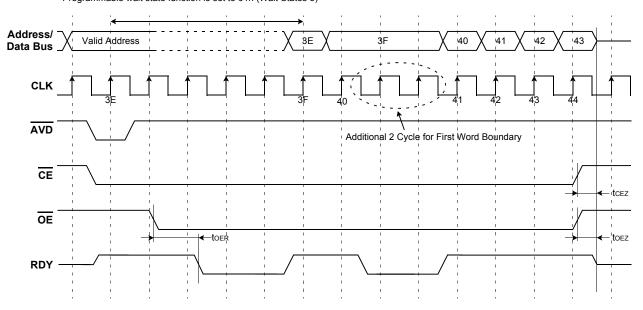

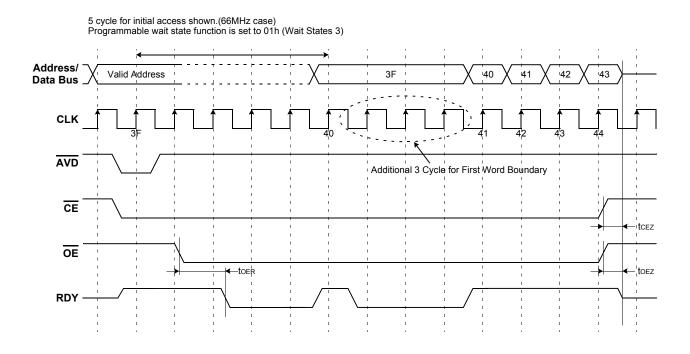

The synchronous(burst) mode will *automatically* be enabled on the first rising edge on the CLK input while  $\overline{\text{AVD}}$  is held low. Note that the device is enabled for asynchronous mode when it first powers up. The initial word is output tiAA after the rising edge of the first CLK cycle. Subsequent words are output tiBA after the rising edge of each successive clock cycle, which automatically increments the internal address counter. Note that the device has internal address boundary that occurs every 16 words. When the device is crossing the first word boundary, additional clock cycles are needed before data appears for the next address. The number of additional clock cycle can vary from zero to three cycles, and the exact number of additional clock cycle depends on the starting address of burst read. (Refer to Figure 13) The RDY output indicates this condition to the system by pulsing low. The device will continue to output sequential burst data, wrapping around to address 000000h after it reaches the highest addressable memory location until the system asserts  $\overline{\text{CE}}$  high,  $\overline{\text{RESET}}$  low or  $\overline{\text{AVD}}$  low in conjunction with a new address. (See Table 4.) The reset command does not terminate the burst read operation. When it accessed the bank is programming or erasing, continuous burst read mode will output status data. And status data will be sustained until the system asserts  $\overline{\text{CE}}$  high or  $\overline{\text{RESET}}$  low or  $\overline{\text{AVD}}$  low in conjunction with a new address.

Note that at least  $\underline{10}$ ns is needed to start next burst read operation from terminating previous burst read operation in the case of asserting  $\overline{CE}$  high.

#### 8-,16-Word Linear Burst Read

As well as the Continuous Linear Burst Mode, there are two(8 & 16 word) linear wrap & no-wrap mode, in which a fixed number of words are read from consecutive addresses. In these modes, the addresses for burst read are determined by the group within which the starting address falls. The groups are sized according to the number of words read in a single burst sequence for a given mode.(See Table. 6)

Table 6. Burst Address Groups(Wrap mode only)

| Burst Mode | Group Size | Group Address Ranges  |

|------------|------------|-----------------------|

| 8 word     | 8 words    | 0-7h, 8-Fh, 10-17h,   |

| 16 word    | 16 words   | 0-Fh, 10-1Fh, 20-2Fh, |

As an example:

In wrap mode case, if the starting address in the 8-word mode is 2h, the address range to be read would be 0-7h, and the wrap burst sequence would be 2-3-4-5-6-7-0-1h. The burst sequence begins with the starting address written to the device, but wraps back to the first address in the selected group. In a similar manner, 16-word wrap mode begin their burst sequence on the starting address written to the device, and then wrap back to the first address in the selected address group.

In no-wrap mode case, if the starting address in the 8-word mode is 2h, the no-wrap burst sequence would be 2-3-4-5-6-7-8-9h. The burst sequence begins with the starting address written to the device, and continue to the 8th address from starting address. In a similar manner, 16-word no-wrap mode begin their burst sequence on the starting address written to the device, and continue to the 16th address from starting address. Also, when the address cross the word boundary in no-wrap mode, same number of additional clock cycles as continuous linear mode is needed.

## **Programmable Wait State**

The programmable wait state feature indicates to the device the number of additional clock cycles that must elapse after  $\overline{\text{AVD}}$  is driven active for burst read mode. Upon power up, the number of total initial access cycles defaults to seven.

#### Handshaking

The handshaking feature allows the host system to simply monitor the RDY signal from the device to determine when the initial word of burst data is ready to be read. To set the number of initial cycle for optimal burst mode, the host should use the programmable wait state configuration.(See "Set Burst Mode Configuration Register" for details.) The rising edge of RDY after  $\overline{OE}$  goes low indicates the initial word of valid burst data. Using the autoselect command sequence the handshaking feature may be verified in the device.

### **Set Burst Mode Configuration Register**

The device uses a configuration register to set the various burst parameters: the number of initial cycles for burst and burst read mode. The burst mode configuration register must be set before the device enter burst mode.

The burst mode configuration register is loaded with a three-cycle command sequences. On the third cycle, the data should be C0h, address bits A11-A0 should be 555h, and address bits A18-A12 set the code to be latched. The device will power up or after a hardware reset with the default setting.

**Table 7. Burst Mode Configuration Register Table**

| Address Bit | Function                | Settings(Binary)                                                                                                                                                                   |

|-------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A18         | RDY Active              | 1 = RDY active one clock cycle before data<br>0 = RDY active with data(default)                                                                                                    |

| A17         |                         | 000 = Continuous(default)                                                                                                                                                          |

| A16         | Downt David Mada        | 001 = 8-word linear with wrap<br>010 = 16-word linear with wrap                                                                                                                    |

| A15         | Burst Read Mode         | 011 = 8-word linear with no-wrap<br>100 = 16-word linear with no-wrap<br>101 ~ 111 = Reserve                                                                                       |

| A14         |                         | 000 = Data is valid on the 4th active CLK edge after AVD transition to Viн                                                                                                         |

| A13         |                         | 001 = Data is valid on the 5th active CLK edge after AVD transition to V <sub>I</sub> H<br>010 = Data is valid on the 6th active CLK edge after AVD transition to V <sub>I</sub> H |

| A12         | Programmable Wait State | 011 = Data is valid on the 7th active CLK edge after AVD transition to V <sub>I</sub> H (default)<br>100 = Reserve<br>101 = Reserve<br>110 = Reserve<br>111 = Reserve              |

#### **Programmable Wait State Configuration**

This feature informs the device of the number of clock cycles that must elapse after AVD# is driven active before data will be available. This value is determined by the input frequency of the device. Address bits A14-A12 determine the setting. (See Burst Mode Configuration Register Table)

The Programmable wait state setting instructs the device to set a particular number of clock cycles for the initial access in burst mode. Note that hardware reset will set the wait state to the default setting, that is 7 initial cycles.

#### **Burst Read Mode Setting**

The device supports five different burst read modes: continuous linear mode, 8 and 16 word linear burst modes with wrap and 8 and 16 word linear burst modes with no-wrap.

#### **RDY Configuration**

By default, the RDY pin will be high whenever there is valid data on the output. The device can be set so that RDY goes active one data cycle before active data. Address bit A18 determine this setting. Note that RDY always go high with valid data in case of word boundary crossing.

**Table 8. Burst Address Sequences**

|         | Start |                  | Burst Address Sequence(Decimal) |               |

|---------|-------|------------------|---------------------------------|---------------|

|         | Addr. | Continuous Burst | 8-word Burst                    | 16-word Burst |

|         | 0     | 0-1-2-3-4-5-6    | 0-1-2-3-4-5-6-7                 | 0-1-2-3D-E-F  |

|         | 1     | 1-2-3-4-5-6-7    | 1-2-3-4-5-6-7-0                 | 1-2-3-4E-F-0  |

| Wrap    | 2     | 2-3-4-5-6-7-8    | 2-3-4-5-6-7-0-1                 | 2-3-4-5F-0-1  |

|         |       |                  |                                 |               |

|         | -     | •                | •                               | •             |

|         | 0     | 0-1-2-3-4-5-6    | 0-1-2-3-4-5-6-7                 | 0-1-2-3D-E-F  |

|         | 1     | 1-2-3-4-5-6-7    | 1-2-3-4-5-6-7-8                 | 1-2-3-4E-F-10 |

| No-wrap | 2     | 2-3-4-5-6-7-8    | 2-3-4-5-6-7-8-9                 | 2-3-4-5F-0-11 |

|         |       |                  |                                 |               |

|         | •     | •                | •                               | •             |

#### **Autoselect Mode**

By writing the autoselect command sequences to the system, the device enters the autoselect mode. This mode can be read only by asynchronous read mode. The system can then read autoselect codes from the internal register(which is separate from the memory array). Standard asynchronous read cycle timings apply in this mode. The device offers the Autoselect mode to identify manufacturer and device type by reading a binary code. In addition, this mode allows the host system to verify the block protection or unprotection. Table 5 shows the address and data requirements. The autoselect command sequence may be written to an address within a bank that is in the read mode, erase-suspend-read mode or program-suspend-read mode. The autoselect command may not be written while the device is actively programming or erasing in the device. The autoselect command sequence is initiated by first writing two unlock cycles. This is followed by a third write cycle that contains the address and the autoselect command. Note that the block address is needed for the verification of block protection. The system may read at any address within the same bank any number of times without initiating another autoselect command sequence. And the burst read should be prohibited during Autoselect Mode. To terminate the autoselect operation, write Reset command(F0H) into the command register.

**Table 9. Autoselect Mode Description**

| Description                   | Address    | Read Data                                       |

|-------------------------------|------------|-------------------------------------------------|

| Manufacturer ID               | (DA) + 00H | ECH                                             |

| Device ID                     | (DA) + 01H | 2250H(Top Boot Block), 2251H(Bottom Boot Block) |

| Block Protection/Unprotection | (BA) + 02H | 01H (protected), 00H (unprotected)              |

### Standby Mode

When the  $\overline{\text{CE}}$  and  $\overline{\text{RESET}}$  inputs are both held at  $Vcc\pm0.2V$  or the system is not reading or writing, the device enters Stand-by mode to minimize the power consumption. In this mode, the device outputs are placed in the high impedence state, independent of the  $\overline{\text{OE}}$  input. When the device is in either of these standby modes, the device requires standard access time (tCE) for read access before it is ready to read data. If the device is deselected during erasure or programming, the device draws active current until the operation is completed. Iccs in the DC Characteristics table represents the standby current specification.

### **Automatic Sleep Mode**

The device features Automatic Sleep Mode to minimize the device power consumption during both asynchronous and burst mode. When addresses remain stable for tAA+60ns, the device automatically enables this mode. The automatic sleep mode is independent of the  $\overline{\text{CE}}$ ,  $\overline{\text{WE}}$ , and  $\overline{\text{OE}}$  control signals. In a sleep mode, output data is latched and always available to the system. When addresses are changed, the device provides new data without wait time. Automatic sleep mode current is equal to standby mode current.

## **NOR FLASH MEMORY**

## K8S6415ET(B)B

## **Output Disable Mode**

When the  $\overline{OE}$  input is at V<sub>IH</sub>, output from the device is disabled. The outputs are placed in the high impedance state.

## **Block Protection & Unprotection**

To protect the block from accidental writes, the block protection/unprotection command sequence is used. On power up, all blocks in the device are protected. To unprotect a block, the system must write the block protection/unprotection command sequence. The first two cycles are written: addresses are don't care and data is 60h. Using the third cycle, the block address (ABP) and command (60h) is written, while specifying with addresses A6, A1 and A0 whether that block should be protected (A6 = VIL, A1 = VIH, A0 = VIL). After the third cycle, the system can continue to protect or unprotect additional cycles, or exit the sequence by writing F0h (reset command).

The device offers three types of data protection at the block level:

- The block protection/unprotection command sequence disables or re-enables both program and erase operations in any block.

- When WP is at VIL, the two outermost blocks are protected.

- . When VPP is at VIL, all blocks are protected.

Note that user never float the Vpp and WP, that is, Vpp is always connected with ViH, ViL or Vi□ and WP is ViH or ViL.

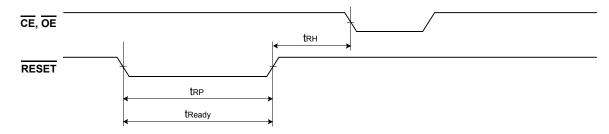

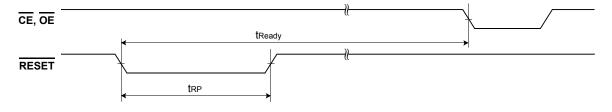

#### **Hardware Reset**

The device features a hardware method of resetting the device by the  $\overline{RESET}$  input. When the  $\overline{RESET}$  pin is held low(VIL) for at least a period of tRP, the device immediately terminates any operation in progress, tristates all outputs, and ignores all read/write commands for the duration of the  $\overline{RESET}$  pulse. The device also resets the internal state machine to asynchronous read mode. To ensure data integrity, the interrupted operation should be reinitiated once the device is ready to accept another command sequence. As previously noted, when  $\overline{RESET}$  is held at Vss  $\pm$  0.2V, the device enters standby mode. The  $\overline{RESET}$  pin may be tied to the system reset pin. If a system reset occurs during the Internal Program or Erase Routine, the device will be automatically reset to the asynchronous read mode; this will enable the systems microprocessor to read the boot-up firmware from the Flash memory. If  $\overline{RESET}$  is asserted during a program or erase operation, the device requires a time of tREADY (during Internal Routines) before the device is ready to read data again. If  $\overline{RESET}$  is asserted when a program or erase operation is not executing, the reset operation is completed within a time of tREADY (not during Internal Routines). tRH is needed to read data after  $\overline{RESET}$  returns to Vih. Refer to the AC Characteristics tables for  $\overline{RESET}$  parameters and to Figure 6 for the timing diagram.

#### Software Reset

The reset command provides that the bank is reseted to read mode, erase-suspend-read mode or program-suspend-read mode. The addresses are in Don't Care state. The reset command may be written between the sequence cycles in an erase command sequence before erasing begins, or in an program command sequence before programming begins. If the device begins erasure or programming, the reset command is ignored until the operation is completed. If the program command sequence is written to a bank that is in the Erase Suspend mode, writing the reset command returns that bank to the erase-suspend-read mode. The reset command valid between the sequence cycles in an autoselect command sequence. In an autoselect mode, the reset command must be written to return to the read mode. If a bank entered the autoselect mode while in the Erase Suspend mode, writing the reset command returns that bank to the erase-suspend-read mode. Also, if a bank entered the autoselect mode while in the Program Suspend mode, writing the reset command returns that bank to the program-suspend-read mode. If DQ5 goes high during a program or erase operation, writing the reset command returns the banks to the read mode. (or erase-suspend-read mode if the bank was in Erase Suspend)

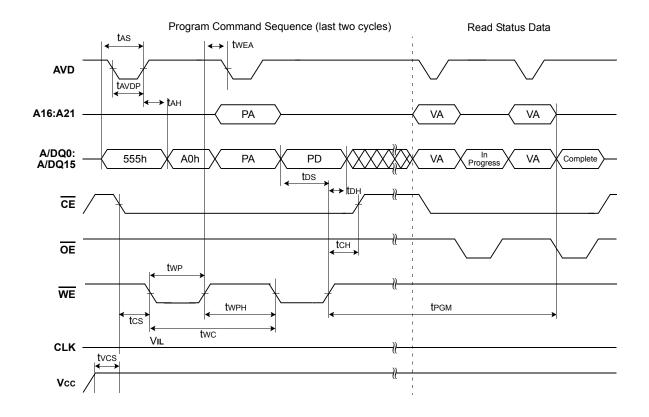

### **Program**

The K8S6415E can be programmed in units of a word. Programming is writing 0's into the memory array by executing the Internal Program Routine. In order to perform the Internal Program Routine, a four-cycle command sequence is necessary. The first two cycles are unlock cycles. The third cycle is assigned for the program setup command. In the last cycle, the address of the memory location and the data to be programmed at that location are written. The device automatically generates adequate program pulses and verifies the programmed cell margin by the Internal Program Routine. During the execution of the Routine, the system is not required to provide further controls or timings. During the Internal Program Routine, commands written to the device will be ignored. Note that a hardware reset during a program operation will cause data corruption at the corresponding location.

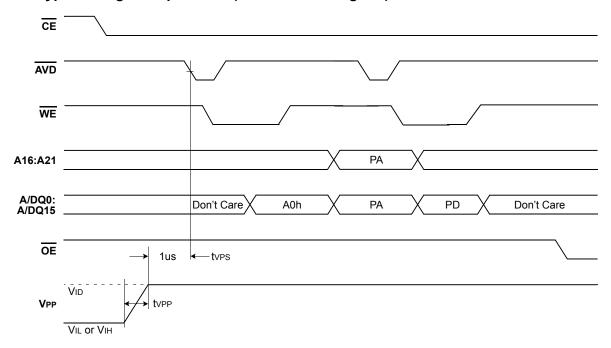

### **Accelerated Program Operation**

The device provides Single/Quadruple word accelerated program operations through the Vpp input. Using this mode, faster manufacturing throughput at the factory is possible. When VID is asserted on the Vpp input, the device automatically enters the Unlock Bypass mode, temporarily unprotects any protected blocks, and uses the higher voltage on the input to reduce the time required for program operations. By removing VID returns the device to normal operation mode.

Note that Read while Accelerated Program and Program suspend mode are not guaranteed

## NOR FLASH MEMORY

## K8S6415ET(B)B

#### Single word accelerated program operation

The system would use two-cycle program sequence (One-cycle (XXX - A0H) is for single word program command, and Next one-cycle (PA - PD) is for program address and data ).

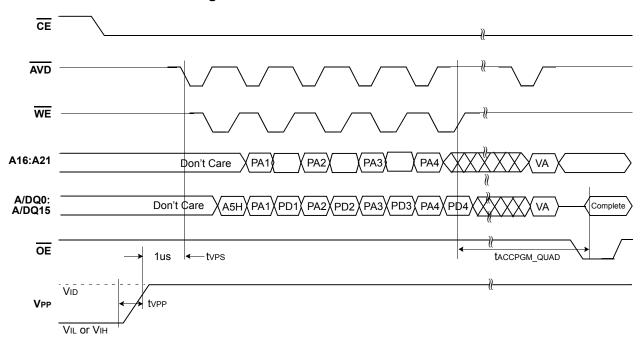

#### Quadruple word accelerated program operation

As well as Single word accelerated program, the system would use five-cycle program sequence (One-cycle (XXX - A5H) is for quadruple word program command, and four cycles are for program address and data).

- Only four words programming is possible

- Each program address must have the same A21~A2 address

- The device automatically generates adequate program pulses and ignores other command after program command

- Program/Erase cycling must be limited below 100cycles for optimum performance.

- Read while Write mode is not guaranteed

Requirements: Ambient temperature: Ta=30°C±10°C

#### **Unlock Bypass**

The K8S6415E provides the unlock bypass mode to save its operation time. This mode is possible for program, block erase and chip erase operation. There are two methods to enter the unlock bypass mode. The mode is invoked by the unlock bypass command sequence or the assertion of VID on VPP pin. Unlike the standard program/erase command sequence that contains four bus cycles, the unlock bypass program/erase command sequence comprises only two bus cycles. The unlock bypass mode is engaged by issuing the unlock bypass command sequence which is comprised of three bus cycles. Writing first two unlock cycles is followed by a third cycle containing the unlock bypass command (20H). Once the device is in the unlock bypass mode, the unlock bypass program/erase command sequence is necessary. The unlock bypass program command sequence is comprised of only two bus cycles; writing the unlock bypass program command (A0H) is followed by the program address and data. This command sequence is the only valid one for programming the device in the unlock bypass mode. Also, The unlock bypass erase command sequence is comprised of two bus cycles; writing the unlock bypass block erase command(80H-30H) or writing the unlock bypass chip erase command(80H-10H). This command sequence are the only valid ones for erasing the device in the unlock bypass mode. The unlock bypass reset command sequence is the only valid command sequence to exit the unlock bypass mode. The unlock bypass reset command sequence consists of two bus cycles. The first cycle must contain the data (90H). The second cycle contains only the data (00H). Then, the device returns to the read mode.

To enter the unlock bypass mode in hardware level, the VID also can be used. By assertion VID on the VPP pin, the device enters the unlock bypass mode. Also, the all blocks are temporarily unprotected when the device using the VID for unlock bypass mode. To exit the unlock bypass mode, just remove the asserted VID from the VPP pin.(Note that user never float the VPP, that is, VPP is always connected with VIH, VIL or VID.).

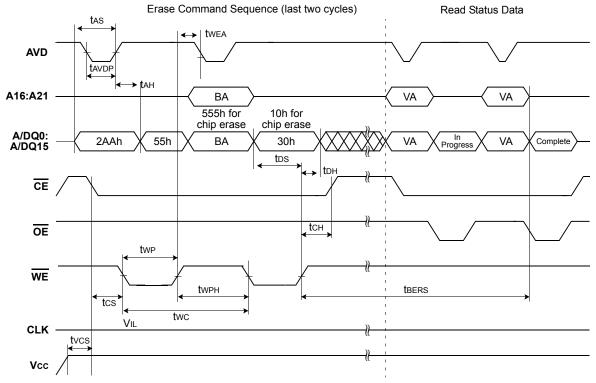

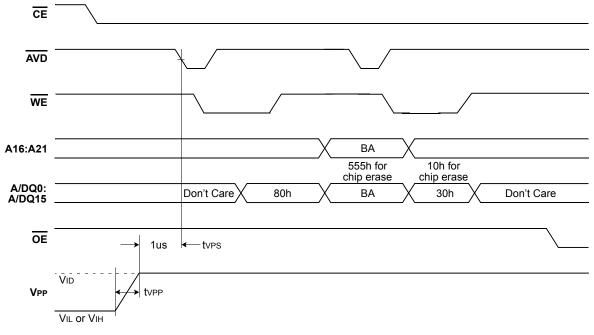

## **Chip Erase**

To erase a chip is to write 1's into the entire memory array by executing the Internal Erase Routine. The Chip Erase requires six bus cycles to write the command sequence. The erase set-up command is written after first two "unlock" cycles. Then, there are two more write cycles prior to writing the chip erase command. The Internal Erase Routine automatically pre-programs and verifies the entire memory for an all zero data pattern prior to erasing. The automatic erase begins on the rising edge of the last  $\overline{\text{WE}}$  pulse in the command sequence and terminates when DQ7 is "1". After that the device returns to the read mode.

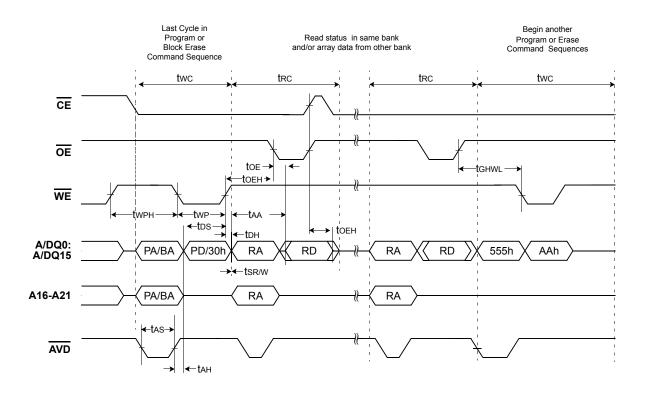

### **Block Erase**

To erase a block is to write 1's into the desired memory block by executing the Internal Erase Routine. The Block Erase requires six bus cycles to write the command sequence shown in Table 5. After the first two "unlock" cycles, the erase setup command (80H) is written at the third cycle. Then there are two more "unlock" cycles followed by the Block Erase command. The Internal Erase Routine automatically pre-programs and verifies the entire memory prior to erasing it. The block address is latched on the rising edge of  $\overline{\text{AVD}}$ , while the Block Erase command is latched on the rising edge of  $\overline{\text{WE}}$ . Multiple blocks can be erased sequentially by writing the sixth bus-cycle. Upon completion of the last cycle for the Block Erase, additional block address and the Block Erase command (30H) can be written to perform the Multi-Block Erase. For the Multi-Block Erase, only sixth cycle(block address and 30H) is needed.(Similarly, only second cycle is needed in unlock bypass block erase.) An 50us (typical) "time window" is required between the Block Erase command writes. The Block Erase command must be written within the 50us "time window", otherwise the Block Erase command will be ignored. The 50us "time window" is reset when the falling edge of the  $\overline{\text{WE}}$  occurs within the 50us of "time window" to latch the Block Erase command. During the 50us of "time window", any command other than the Block Erase or the Erase Suspend command written to the device will reset the device to read mode. After the 50 us of "time window", the Block Erase command will initiate the Internal Erase Routine to erase the selected blocks. Any Block Erase address and command following the exceeded "time window" may or may not be accepted. No other commands will be recognized except the Erase Suspend command during Block Erase operation.

The device provides accelerated erase operations through the Vpp input. When ViD is asserted on the Vpp input, the device automatically enters the Unlock Bypass mode, temporarily unprotects any protected blocks, and uses the higher voltage on the input to reduce the time required for erase. By removing ViD returns the device to normal operation mode.

## NOR FLASH MEMORY

## K8S6415ET(B)B

## **Erase Suspend / Resume**

The Erase Suspend command interrupts the Block Erase to read or program data in a block that is not being erased. Also, it is possible to protect or unprotect of the block that is not being erased in erase suspend mode. The Erase Suspend command is only valid during the Block Erase operation including the time window of 50 us. The Erase Suspend command is not valid while the Chip Erase or the Internal Program Routine sequence is running. When the Erase Suspend command is written during a Block Erase operation, the device requires a maximum of 20 us(recovery time) to suspend the erase operation. Therefore system must wait for 20us(recovery time) to read the data from the bank which include the block being erased. Otherwise, system can read the data immediately from a bank which don't include the block being erased without recovery time(max. 20us) after Erase Suspend command. And, after the maximum 20us recovery time, the device is available for programming data in a block that is not being erased. But, when the Erase Suspend command is written during the block erase time window (50 us), the device immediately terminates the block erase time window and suspends the erase operation. The system may also write the autoselect command sequence when the device is in the Erase Suspend mode. When the Erase Resume command is executed, the Block Erase operation will resume. When the Erase Suspend or Erase Resume command is executed, the addresses are in Don't Care state.

## **Program Suspend / Resume**

The device provides the Program Suspend/Resume mode. This mode is used to enable Data Read by suspending the Program operation. The device accepts a Program Suspend command in Program mode(including Program operations performed during Erase Suspend) but other commands are ignored. After input of the Program Suspend command, 2us is needed to enter the Program Suspend Read mode. Therefore system must wait for 2us(recovery time) to read the data from the bank which include the block being programmed. Othwewise, system can read the data immediately from a bank which don't include block being programmed without ecovery time(max. 2us) after Program Suspen command. Like an Erase Suspend mode, the device can be returned to Program mode by using a Program Resume command.

### **Read While Write Operation**

The device is capable of reading data from one bank while writing in the other banks. This is so called the Read While Write operation. An erase operation may also be suspended to read from or program to another location within the same bank(except the block being erased). The Read While Write operation is prohibited during the chip erase operation. Figure 12 shows how read and write cycles may be initiated for simultaneous operation with zero latency. Refer to the DC Characteristics table for read-while-write current specifications.

## **OTP Block Region**

The OTP Block feature provides a 256-byte Flash memory region that enables permanent part identification through an Electronic Serial Number (ESN). The OTP Block is customer lockable and shipped with itself unlocked, allowing customers to untilize the that block in any manner they choose. The customer-lockable OTP Block has the Protection Verify Bit (DQ0) set to a "0" for Unlocked state or a "1" for Locked state.

The system accesses the OTP Block through a command sequence (see "Enter OTP Block / Exit OTP Block Command sequence" at Table8). After the system has written the "Enter OTP Block" Command sequence, it may read the OTP Block by using the addresses (7FFF80h~7FFFFFh) normally and may check the Protection Verify Bit (DQ0) by using the "Autoselect Block Protection Verify" Command sequence with OTP Block address. This mode of operation continues until the system issues the "Exit OTP Block" Command suquence, a hardware reset or until power is removed from the device. On power-up, or following a hardware reset, the device reverts to sending commands to main blocks. Note that the Accelerated function and unlock bypass modes are not available when the OTP Block is enabled.

#### **Customer Lockable**

In a Customer lockable device, The OTP Block is one-time programmable and can be locked only once. Note that the Accelerated programming and Unlock bypass functions are not available when programming the OTP Block. Locking operation to the OTP Block is started by writing the "Enter OTP Block" Command sequence, and then the "Block Protection" Command sequence (Table 8) with an OTP Block address. Hardware reset terminates Locking operation, and then makes exiting from OTP Block. The Locking operation has to be above 100us.

The OTP Block Lock operation must be used with caution since, once locked, there is no procedure available for unlocking and none of the bits in the OTP Block space can be modified in any way.

#### Write Pulse "Glitch" Protection

Noise pulses of less than 5ns (typical) on  $\overline{OE}$ ,  $\overline{CE}$ ,  $\overline{AVD}$  or  $\overline{WE}$  do not initiate a write cycle.

## **Low Vcc Write Inhibit**

To avoid initiation of a write cycle during Vcc power-up and power-down, a write cycle is locked out for Vcc less than VLKO. If the Vcc < VLKO (Lock-Out Voltage), the command register and all internal program/erase circuits are disabled. Under this condition the device will reset itself to the read mode. Subsequent writes will be ignored until the Vcc level is greater than VLKO. It is the user's responsibility to ensure that the control pins are logically correct to prevent unintentional writes when Vcc is above VLKO.

### **Logical Inhibit**

Write cycles are inhibited by holding any one of  $\overline{OE} = VIL$ ,  $\overline{CE} = VIH$  or  $\overline{WE} = VIH$ . To initiate a write cycle,  $\overline{CE}$  and  $\overline{WE}$  must be a logical zero while  $\overline{OE}$  is a logical one.

## **Power-up Protection**

To avoid initiation of a write cycle during Vcc power-up, RESET low must be asserted during Power-up. After RESET goes high, the device is reset to the read mode.

### **FLASH MEMORY STATUS FLAGS**

The K8S6415E has means to indicate its status of operation in the bank where a program or erase operation is in processes. Address must include bank address being executed internal routine operation. The status is indicated by raising the device status flag via corresponding DQ pins. The status data can be read during burst read mode by using  $\overline{\text{AVD}}$  signal with a bank address. That means status read is supported in synchronous mode. If status read is performed, the data provided in the burst read is identical to the data in the initial access. To initiate the synchronous read again, a new address and  $\overline{\text{AVD}}$  pulse is needed after the host has completed status reads or the device has completed the program or erase operation. The corresponding DQ pins are DQ7, DQ6, DQ5, DQ3 and DQ2.

Table 10. Hardware Sequence Flags

|                         | Status                    |                                 | DQ7  | DQ6    | DQ5  | DQ3  | DQ2                |

|-------------------------|---------------------------|---------------------------------|------|--------|------|------|--------------------|

|                         | Programming               |                                 | DQ7  | Toggle | 0    | 0    | 1                  |

|                         | Block Erase or Chip Erase |                                 | 0    | Toggle | 0    | 1    | Toggle             |

|                         | Erase Suspend Read        | Erase Suspended<br>Block        | 1    | 1      | 0    | 0    | Toggle<br>(Note 1) |

| In Progress             | Erase Suspend Read        | Non-Erase Suspended<br>Block    | Data | Data   | Data | Data | Data               |

|                         | Erase Suspend<br>Program  | Non-Erase Suspended<br>Block    | DQ7  | Toggle | 0    | 0    | 1                  |

|                         | Program Suspend Read      | Program Suspended<br>Block      | DQ7  | 1      | 0    | 0    | Toggle<br>(Note 1) |

|                         | Program Suspend Read      | Non- program<br>Suspended Block | Data | Data   | Data | Data | Data               |

|                         | Programming               |                                 | DQ7  | Toggle | 1    | 0    | No<br>Toggle       |

| Exceeded<br>Time Limits | Block Erase or Chip Erase |                                 | 0    | Toggle | 1    | 1    | (Note 2)           |

| 2                       | Erase Suspend Program     |                                 | DQ7  | Toggle | 1    | 0    | No<br>Toggle       |

#### Notes

- 1. DQ2 will toggle when the device performs successive read operations from the erase/program suspended block.

- 2. If DQ5 is High (exceeded timing limits), successive reads from a problem block will cause DQ2 to toggle.

### DQ7 : Data Polling

When an attempt to read the device is made while executing the Internal Program, the complement of the data is written to DQ7 as an indication of the Routine in progress. When the Routine is completed an attempt to access to the device will produce the true data written to DQ7. When a user attempts to read the block being erased, DQ7 will be low. If the device is placed in the Erase/Program Suspend Mode, the status can be detected via the DQ7 pin. If the system tries to read an address which belongs to a block that is being erase suspended, DQ7 will be high. And, if the system tries to read an address which belongs to a block that is being program suspended, the output will be the true data of DQ7 itself. If a non-erase-suspended or non-program-suspended block address is read, the device will produce the true data to DQ7. If an attempt is made to program a protected block, DQ7 outputs complements the data for approximately  $1\mu s$  and the device then returns to the Read Mode without changing data in the block. If an attempt is made to erase a protected block, DQ7 outputs complement data in approximately 100us and the device then returns to the Read Mode without erasing the data in the block.

### DQ6: Toggle Bit

Toggle bit is another option to detect whether an Internal Routine is in progress or completed. Once the device is at a busy state, DQ6 will toggle. Toggling DQ6 will stop after the device completes its Internal Routine. If the device is in the Erase/Program Suspend Mode, an attempt to read an address that belongs to a block that is being erased or programmed will produce a high output of DQ6. If an address belongs to a block that is not being erased or programmed, toggling is halted and valid data is produced at DQ6. If an attempt is made to program a protected block, DQ6 toggles for approximately 1us and the device then returns to the Read Mode without changing the data in the block. If an attempt is made to erase a protected block, DQ6 toggles for approximately  $100\mu s$  and the device then returns to the Read Mode without erasing the data in the block.

#### **DQ5**: Exceed Timing Limits

If the Internal Program/Erase Routine extends beyond the timing limits, DQ5 will go High, indicating program/erase failure.

#### **DQ3**: Block Erase Timer

The status of the multi-block erase operation can be detected via the DQ3 pin. DQ3 will go High if  $50\mu s$  of the block erase time window expires. In this case, the Internal Erase Routine will initiate the erase operation. Therefore, the device will not accept further write commands until the erase operation is completed. DQ3 is Low if the block erase time window is not expired. Within the block erase time window, an additional block erase command (30H) can be accepted. To confirm that the block erase command has been accepted, the software may check the status of DQ3 following each block erase command.

### DQ2: Toggle Bit 2

The device generates a toggling pulse in DQ2 only if an Internal Erase Routine or an Erase/Program Suspend is in progress. When the device executes the Internal Erase Routine, DQ2 toggles only if an erasing block is read. Although the Internal Erase Routine is in the Exceeded Time Limits, DQ2 toggles only if an erasing block in the Exceeded Time Limits is read. When the device is in the Erase/Program Suspend mode, DQ2 toggles only if an address in the erasing or programming block is read. If a non-erasing or non-programmed block address is read during the Erase/Program Suspend mode, then DQ2 will produce valid data. DQ2 will go High if the user tries to program a non-erase suspend block while the device is in the Erase Suspend mode.

## **RDY: Ready**

Normally the RDY signal is used to indicate if new burst data is available at the rising edge of the clock cycle or not. If RDY is low state, data is not valid at expected time, and if high state, data is valid. Note that, if  $\overline{CE}$  is low and  $\overline{OE}$  is high, the RDY is high state.

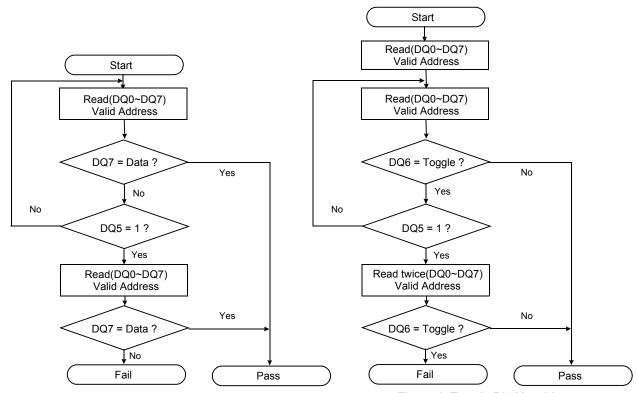

Figure 1. Data Polling Algorithms

Figure 2. Toggle Bit Algorithms

## **Commom Flash Memory Interface**

Common Flash Momory Interface is contrived to increase the compatibility of host system software. It provides the specific information of the device, such as memory size and electrical features. Once this information has been obtained, the system software will know which command sets to use to enable flash writes, block erases, and control the flash component.

When the system writes the CFI command(98H) to address 55H, the device enters the CFI mode. And then if the system writes the address shown in Table 11, the system can read the CFI data. Query data are always presented on the lowest-order data outputs(DQ0-7) only. In word(x16) mode, the upper data outputs(DQ8-15) is 00h. To terminate this operation, the system must write the reset command.

**Table 11. Common Flash Memory Interface Code**

| Description                                                                        | Addresses<br>(Word Mode) | Data   |

|------------------------------------------------------------------------------------|--------------------------|--------|

|                                                                                    | 10H                      | 0051H  |

| Query Unique ASCII string "QRY"                                                    | 11H                      | 0052H  |

|                                                                                    | 12H                      | 0059H  |

| Primary OEM Command Set                                                            | 13H                      | 0002H  |

| Timary OLM Command Oct                                                             | 14H                      | 0000H  |

| Address for Primary Extended Table                                                 | 15H                      | 0040H  |

| Address for Filliary Extended Table                                                | 16H                      | H0000  |

| Alternate OEM Command Set (00h = none exists)                                      | 17H                      | 0000H  |

| Alternate OEM Command Cet (Com - Horie Cxists)                                     | 18H                      | H0000  |

| Address for Alternate OEM Extended Table (00h = none exists)                       | 19H                      | 0000H  |

| Address for Alternate SEW Extended Table (SSI Thorie Salsto)                       | 1AH                      | 0000H  |

| Vcc Min. (write/erase)                                                             | 1BH                      | 0017H  |

| D7-D4: volt, D3-D0: 100 millivolt                                                  | .5                       |        |

| Vcc Max. (write/erase)                                                             | 1CH                      | 0019H  |

| D7-D4: volt, D3-D0: 100 millivolt                                                  |                          |        |

| Vpp(Acceleration Program) Supply Minimum                                           |                          |        |