# Class-D Audio Power Stage

# **ADAU1513**

#### **FEATURES**

Integrated stereo power stage  $R_{DS-ON} < 0.3~\Omega$  (per transistor) Efficiency > 90% Short-circuit protection Overtemperature protection

#### **APPLICATIONS**

Flat panel televisions PC audio systems Mini components

### **GENERAL DESCRIPTION**

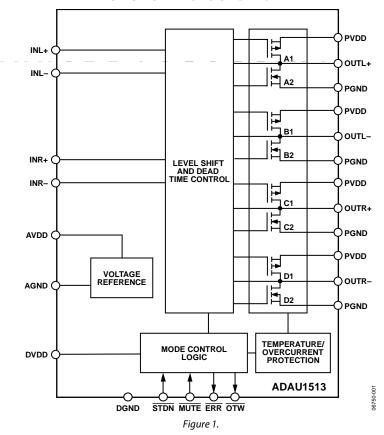

The ADAU1513 is a 2-channel bridge-tied load (BTL) Class-D audio power stage. The power stage can drive the speaker loads of 4  $\Omega$  at up to 15 W per channel at high efficiency. The 4-channel audio system can be formed when used with an ADAV4201 pulse-width modulator (PWM) processor using two ADAU1513s. The power stage accepts a 3.3 V logic differential PWM as input from an ADAV4201 processor. The power stage comprises thermal and output short-circuit protection with logic-level error flag outputs for interfacing to a system microcontroller along with reset and mute control of the power stage. The power stage operates from a range of power supply voltages from 9 V up to 18 V. The low power digital logic operates from a 3.3 V supply. The power stage can be used with modulators other than the ADAV4201. Contact your local sales department for application assistance.

#### **FUNCTIONAL BLOCK DIAGRAM**

## **TABLE OF CONTENTS**

| Features                                   | 1 |

|--------------------------------------------|---|

| Applications                               | 1 |

| General Description                        | 1 |

| Functional Block Diagram                   | 1 |

| Revision History                           | 2 |

| Specifications                             | 3 |

| Performance Summary                        | 3 |

| Power Supplies                             | 3 |

| Digital I/O                                | 4 |

| PWM Input Logic Table                      | 4 |

| Digital Timing                             | 4 |

| Absolute Maximum Ratings                   | 5 |

| ESD Caution                                | 5 |

| Pin Configuration and Function Description | 6 |

| Typical Performance Characteristics        | 8 |

| Τ | heory of Operation                  | 12 |

|---|-------------------------------------|----|

|   | Overview                            | 12 |

|   | Power Stage                         | 12 |

|   | Protection Circuits                 | 12 |

|   | Thermal Protection                  | 12 |

|   | Overcurrent Protection              | 12 |

|   | Undervoltage Protection             | 12 |

|   | Automatic Recovery from Protections | 12 |

|   | MUTE and STDN                       | 13 |

|   | Power-Up/Power-Down Sequence        | 13 |

| A | pplications Information             | 15 |

| C | Outline Dimensions                  | 16 |

|   | Ordering Guide                      | 16 |

|   |                                     |    |

### **REVISION HISTORY**

5/07—Revision 0: Initial Version

### **SPECIFICATIONS**

DVDD = 3.3 V, AVDD = 3.3 V, PVDD = 15 V, ambient temperature =  $25^{\circ}$ C, load impedance =  $8 \Omega$ , measurement bandwidth = 20 Hz to 20 kHz, unless otherwise noted. Audio performance test data measured with ADAV4201.

### **PERFORMANCE SUMMARY**

Table 1.

| Parameter                                      | Min Typ | Max | Unit | Test Conditions/Comments                  |

|------------------------------------------------|---------|-----|------|-------------------------------------------|

| OUTPUT POWER <sup>1</sup>                      |         |     |      | 1 kHz                                     |

|                                                | 11      |     | W    | 1% THD + N, 8 Ω                           |

|                                                | 14      |     | W    | 10% THD + N, 8 Ω                          |

|                                                | 14.5    |     | W    | 1% THD + N, 6 Ω                           |

|                                                | 17.5    |     | W    | 10% THD + N, 6 Ω                          |

|                                                | 19      |     | W    | 1% THD + N, 4 Ω                           |

|                                                | 23      |     | W    | 10% THD + N, 4 Ω                          |

| EFFICIENCY                                     | 90      |     | %    | P <sub>OUT</sub> = 15 W                   |

| R <sub>DS-ON</sub>                             |         |     |      |                                           |

| Per High-Side Transistor                       | 280     |     | mΩ   | $I_D = 100 \text{ mA}$                    |

| Per Low-Side Transistor                        | 250     |     | mΩ   | $I_D = 100 \text{ mA}$                    |

| THERMAL CHARACTERISTICS                        |         |     |      |                                           |

| Thermal Warning Active <sup>2</sup>            | 135     |     | °C   | Die temperature                           |

| Thermal Shutdown Active                        | 150     |     | °C   | Die temperature                           |

| OVERCURRENT SHUTDOWN ACTIVE                    | 5       |     | Α    | peak                                      |

| TOTAL HARMONIC DISTORTION PLUS NOISE (THD + N) | 0.1     |     | %    | Р <sub>ОИТ</sub> = 1 W, 1 kHz             |

| SIGNAL-TO-NOISE RATIO (SNR)                    | 96      |     | dB   | A-weighted, referred to 1% THD + N output |

| DYNAMIC RANGE                                  | 96      |     | dB   | A-weighted, measured with -60 dBFS input  |

| CROSSTALK BETWEEN LEFT AND RIGHT CHANNELS      | 65_     |     | dB   | @ 0 dBES input 20 Hz to 20 kHz            |

| UNDERVOLTAGE TRIP THRESHOLD                    | 5       |     | V    |                                           |

| MINIMUM OUTPUT PULSE WIDTH                     | 50      |     | ns   |                                           |

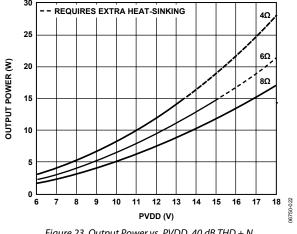

$<sup>^1</sup>$  Output powers above 15 W at 4  $\Omega$  and above 18 W at 6  $\Omega$  may need extra heat-sinking for continuous operation.  $^2$  Thermal warning flag is for indication of device  $T_J$  reaching close to shutdown temperature.

### **POWER SUPPLIES**

Table 2.

| Parameter                              | Min | Тур | Max | Unit | Test Conditions/Comments |

|----------------------------------------|-----|-----|-----|------|--------------------------|

| DIGITAL SUPPLY VOLTAGE (DVDD)          | 3.0 | 3.3 | 3.6 | V    |                          |

| ANALOG SUPPLY VOLTAGE (AVDD)           | 3.0 | 3.3 | 3.6 | V    |                          |

| POWER TRANSISTOR SUPPLY VOLTAGE (PVDD) | 9   | 15  | 18  | V    |                          |

| POWER-DOWN CURRENT                     |     |     |     |      | STDN held low            |

| AVDD                                   |     | 2   | 3   | μΑ   |                          |

| DVDD                                   |     | 50  | 55  | μΑ   |                          |

| PVDD                                   |     | 55  | 600 | μΑ   |                          |

| MUTE CURRENT                           |     |     |     |      | MUTE held low            |

| AVDD                                   |     | 0.5 | 0.6 | mA   |                          |

| DVDD                                   |     | 0.9 | 1.2 | mA   |                          |

| PVDD                                   |     | 0.3 | 0.9 | mA   |                          |

| OPERATING CURRENT                      |     |     |     |      | STDN and MUTE held high  |

| AVDD                                   |     | 0.5 | 0.6 | mA   |                          |

| DVDD                                   |     | 1.1 | 2.5 | mA   |                          |

| PVDD                                   |     | 34  | 40  | mA   |                          |

### **DIGITAL I/O**

Table 3.

| Parameter                         | Min | Тур | Max | Unit | Test Conditions/Comments |

|-----------------------------------|-----|-----|-----|------|--------------------------|

| INPUT VOLTAGE                     |     |     |     |      |                          |

| Input Voltage High                | 2.0 |     |     | V    |                          |

| Input Voltage Low                 |     |     | 8.0 | V    |                          |

| OUTPUT VOLTAGE                    |     |     |     |      |                          |

| Output Voltage High               | 2.4 |     |     | V    | @ 2 mA                   |

| Output Voltage Low                |     |     | 0.4 | V    | @ 2 mA                   |

| LEAKAGE CURRENT ON DIGITAL INPUTS |     |     | 10  | μΑ   |                          |

### **PWM INPUT LOGIC TABLE**

Table 4.

| MUTE | INL+/INR+ | INL-/INR- | OUTL+/OUTR+ | OUTL-/OUTR- | Mode            |

|------|-----------|-----------|-------------|-------------|-----------------|

| Low  | Low/High  | Low/High  | Off         | Off         | High-Z          |

| High | Low       | Low       | GND         | GND         | Output damped   |

| High | High      | Low       | PVDD        | GND         | Positive output |

| High | Low       | High      | GND         | PVDD        | Negative output |

| High | High      | High      | PVDD        | PVDD        | Not used        |

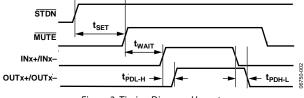

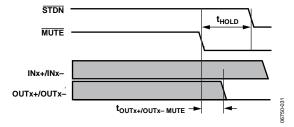

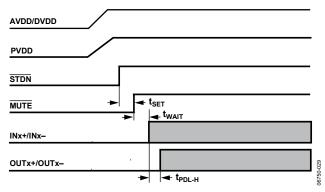

### **DIGITAL TIMING**

Table 5.

| Parameter                                  | Min | Тур | Unit | Description                                                 |

|--------------------------------------------|-----|-----|------|-------------------------------------------------------------|

| t <sub>SET</sub>                           | 10  |     | μs   | Wait Time for Unmute                                        |

| t <sub>HOLD</sub>                          | 10  |     | μs   | Wait Time for Shutdown                                      |

| twait                                      | 100 |     | ns   | Wait Time for Applying Input                                |

| t <sub>PDL-H</sub>                         |     | 13  | ns   | Propagation Delay (Low to High)                             |

| t <sub>PDH-L</sub>                         |     | 13  | ns   | Propagation Delay (High to Low)                             |

| $t_{\text{OUTx}+/\text{OUTx-}\text{MUTE}}$ |     | 600 | ns   | Time Delay After MUTE Held Low Until Output Stops Switching |

Figure 2. Timing Diagram Unmute

Figure 3. Timing Diagram Mute

### **ABSOLUTE MAXIMUM RATINGS**

Table 6.

| Parameter                                          | Rating                       |

|----------------------------------------------------|------------------------------|

| DVDD to DGND                                       | -0.3 V to +3.6 V             |

| AVDD to AGND                                       | −0.3 V to +3.6 V             |

| PVDD to PGND <sup>1</sup>                          | −0.3 V to +20.0 V            |

| PWM Inputs                                         | DGND - 0.3 V to DVDD + 0.3 V |

| MUTE/STDN Inputs                                   | DGND - 0.3 V to DVDD + 0.3 V |

| Operating Temperature Range                        | −40°C to +85°C               |

| Storage Temperature Range                          | −65°C to +150°C              |

| Maximum Junction Temperature                       | 150°C                        |

| $\theta_{JA}$ Thermal Resistance                   | 26.7°C/W                     |

| $Ψ_{JB}$ Thermal Characterization (Junction-Board) | 13.3°C/W                     |

| Ψ <sub>JT</sub> Thermal Characterization           | 0.2°C/W                      |

| (Junction-Package Top)                             |                              |

| Lead Temperature                                   |                              |

| Soldering (10 sec)                                 | 260°C                        |

| Vapor Phase (60 sec)                               | 215°C                        |

| Infrared (15 sec)                                  | 220°C                        |

<sup>&</sup>lt;sup>1</sup> Includes any induced voltage due to inductive load.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

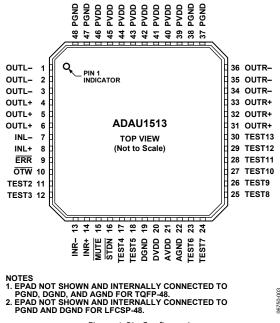

### PIN CONFIGURATION AND FUNCTION DESCRIPTION

Figure 4. Pin Configuration

**Table 7. Pin Function Descriptions**

| Pin Number | Mnemonic | Type <sup>1</sup> | Description                                                                                          |

|------------|----------|-------------------|------------------------------------------------------------------------------------------------------|

| 1, 2, 3    | OUTL     | 0_                | Output of High Power Transistors, Left Channel Negative Polarity.                                    |

| 4, 5, 6    | OUTL+    | 0                 | Output of High Power Transistors, Left Channel Positive Polarity.                                    |

| 7          | INL-     | 1                 | Differential PWM Left Input (–).                                                                     |

| 8          | INL+     | I                 | Differential PWM Left Input (+).                                                                     |

| 9          | ERR      | 0                 | Overtemperature Shutdown Error Indicator (Active Low Open-Drain Output).                             |

| 10         | OTW      | 0                 | Overtemperature Warning Indicator (Active Low Open-Drain Output).                                    |

| 11         | TEST2    | ı                 | Reserved for Internal Use. Connect to DGND.                                                          |

| 12         | TEST3    | ı                 | Reserved for Internal Use. Connect to DVDD.                                                          |

| 13         | INR-     | 1                 | Differential PWM Right Input (–).                                                                    |

| 14         | INR+     | 1                 | Differential PWM Right Input (+).                                                                    |

| 15         | MUTE     | 1                 | Mute (Active Low Input).                                                                             |

| 16         | STDN     | 1                 | Shutdown/Reset Input (Active Low Input).                                                             |

| 17         | TEST4    | 1                 | Reserved for Internal Use. Connect to DGND.                                                          |

| 18         | TEST5    | 0                 | Reserved for Internal Use. Do not connect.                                                           |

| 19         | DGND     | Р                 | Digital Ground for Digital Circuitry. Internally connected to exposed pad (ePAD) <sup>2</sup> .      |

| 20         | DVDD     | Р                 | Positive Supply for Digital Circuitry.                                                               |

| 21         | AVDD     | Р                 | Positive Supply for Analog Circuitry (Can be Tied to DVDD).                                          |

| 22         | AGND     | Р                 | Analog Ground for Analog Circuitry. Internally connected to ePAD <sup>2</sup> . Can be tied to DGND. |

| 23         | TEST6    | 1                 | Reserved for Internal Use. Connect to DGND.                                                          |

| 24         | TEST7    | 1                 | Reserved for Internal Use. Connect to DGND.                                                          |

| 25         | TEST8    | 1                 | Reserved for Internal Use. Connect to DGND.                                                          |

| 26         | TEST9    | I                 | Reserved for Internal Use. Connect to DGND.                                                          |

| 27         | TEST10   | 1                 | Reserved for Internal Use. Connect to DGND.                                                          |

| 28         | TEST11   | 1                 | Reserved for Internal Use. Connect to DGND.                                                          |

| 29         | TEST12   | 1                 | Reserved for Internal Use. Connect to DGND.                                                          |

| 30         | TEST13   | 1                 | Reserved for Internal Use. Connect to DGND.                                                          |

| 31, 32, 33 | OUTR+    | 0                 | Output of High Power Transistors, Right Channel Positive Polarity.                                   |

| Pin Number                     | Mnemonic | Type <sup>1</sup> | Description                                                                          |

|--------------------------------|----------|-------------------|--------------------------------------------------------------------------------------|

| 34, 35, 36                     | OUTR-    | 0                 | Output of High Power Transistors, Right Channel Negative Polarity.                   |

| 37, 38, 47, 48                 | PGND     | Р                 | Power Ground for High Power Transistors. Internally connected to ePAD <sup>2</sup> . |

| 39, 40, 41, 42, 43, 44, 45, 46 | PVDD     | Р                 | Positive Power Supply for High Power Transistors.                                    |

$<sup>^{1}</sup>$  I = input, O = output, P = power.

<sup>&</sup>lt;sup>2</sup> ePAD is connected internally to PGND, DGND, and AGND.

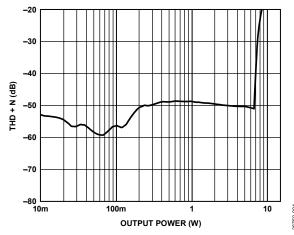

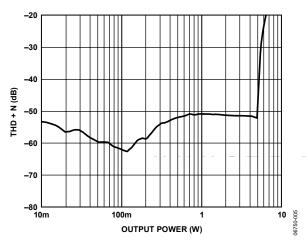

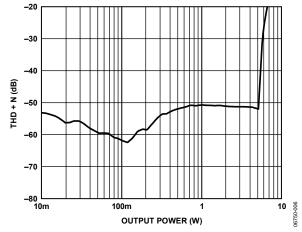

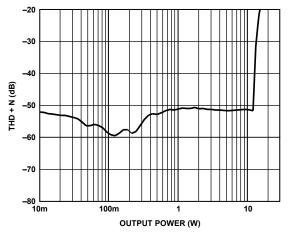

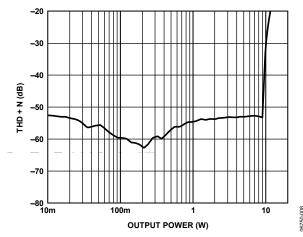

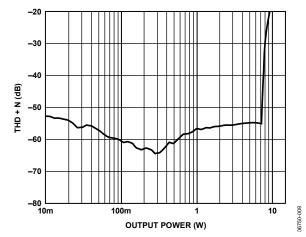

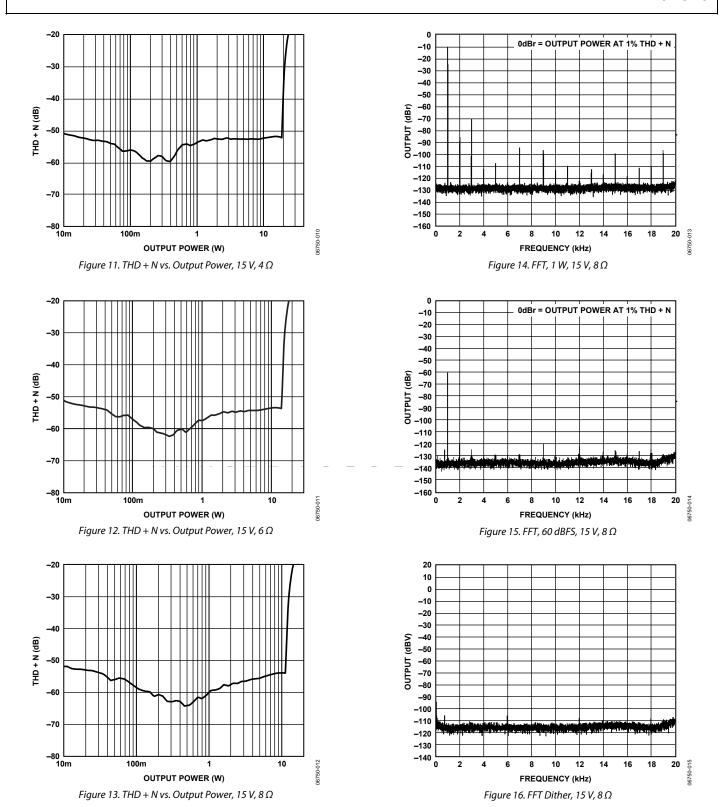

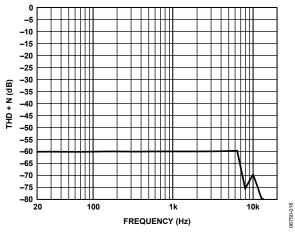

### TYPICAL PERFORMANCE CHARACTERISTICS

Figure 5. THD + N vs. Output Power, 9 V, 4  $\Omega$

Figure 6. THD + N vs. Output Power, 9 V, 6  $\Omega$

Figure 7. THD + N vs. Output Power, 9 V, 8  $\Omega$

Figure 8. THD + N vs. Output Power, 12 V,  $4\Omega$

Figure 9. THD + N vs. Output Power, 12 V, 6  $\Omega$

Figure 10. THD + N vs. Output Power, 12 V, 8  $\Omega$

Figure 17. THD + N vs. Frequency, 1 W, 15 V, 8  $\Omega$

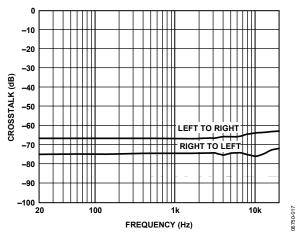

Figure 18. Crosstalk, 0 dBFS, 15 V,  $8 \Omega$

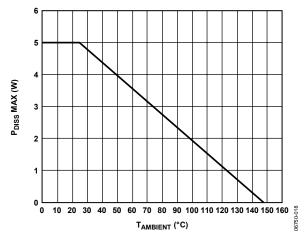

Figure 19. Power Dissipation vs. Ambient Temperature

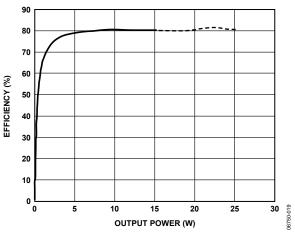

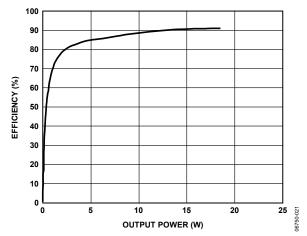

Figure 20. Efficiency vs .Output Power, 15 V, 4  $\Omega$

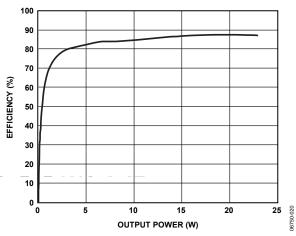

Figure 21. Efficiency vs. Output Power, 15 V, 6  $\Omega$

Figure 22. Efficiency vs. Output Power, 15 V, 8  $\Omega$

Figure 23. Output Power vs. PVDD, 40 dB THD + N

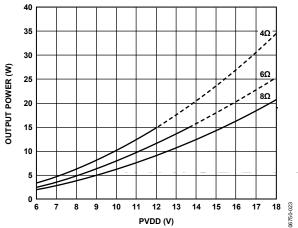

Figure 24. Output Power vs. PVDD, 20 dB THD + N

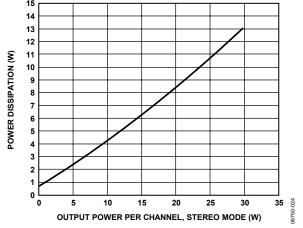

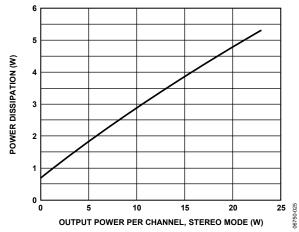

Figure 25. Power Dissipation vs. Output Power, 4  $\Omega$

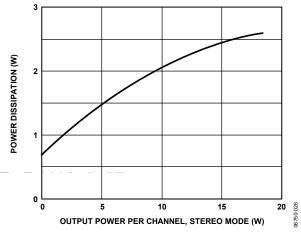

Figure 26. Power Dissipation vs. Output Power, 6  $\Omega$

Figure 27. Power Dissipation vs. Output Power, 8  $\Omega$

# THEORY OF OPERATION

### **OVERVIEW**

The ADAU1513 is a 2-channel integrated power stage designed to accept the logic level PWM inputs. The PWM inputs are amplified, low-pass filtered using a simple passive LC network, and then can be used to drive the speaker loads. The power stage has built-in circuits for overtemperature, overcurrent, short-circuit, and undervoltage protection.

### **POWER STAGE**

The 2-channel ADAU1513 power stage comprises a total of eight half bridges. Each half bridge is made up of PMOS and NMOS devices. The gate drive for the respective FETs is generated internally and does not need a special gate drive supply or bootstrap capacitor compared to all NMOS stages. This simplifies the high-side driver design and requires less external components.

### **PROTECTION CIRCUITS**

The ADAU1513 includes comprehensive protection circuits. It includes thermal warning, thermal overheat, and overcurrent or short-circuit protection on the outputs. The ERR and OTW outputs are open drain, requiring external pull-up resistors. The outputs are capable of sinking 10 mA. The open-drain outputs are useful in multichannel applications where more than one ADAU1513 are used. The error outputs of multiple ADAU1513s can be ORed to simplify the system design. The logic outputs of the error flags ease the system design using a microcontroller.

The power stage does not consist of protection in case PWM input stays high continuously. In such a case, the output produces dc and it is possible to damage the speaker. To prevent this, ensure that the modulator is switching whenever the power stage is turned on.

### THERMAL PROTECTION

Thermal protection in the ADAU1513 is categorized into two error flags: one as thermal warning and the other as thermal shutdown. When the device junction temperature reaches near  $135^{\circ}\text{C}\ (\pm 5^{\circ}\text{C})$  the ADAU1513 outputs a thermal warning error flag by pulling  $\overline{OTW}$  (Pin 10) low. This flag can be used by the microcontroller in the system as an indication to the user or can be used to lower the input level to the amplifier to prevent the thermal shutdown. The device continues operation until shutdown temperature is reached.

When the device junction temperature exceeds 150°C the device outputs an error flag by pulling the  $\overline{ERR}$  (Pin 9) low. This error flag is latched. To restore the operation,  $\overline{MUTE}$  (Pin 16) needs to be toggled to low and then to high again.

#### **OVERCURRENT PROTECTION**

The overcurrent protection in the ADAU1513 is set internally at 5 A peak output current. The device protects the output devices against excessive output current by pulling the  $\overline{ERR}$  (Pin 9) low.

This error flag is latched type. To restore the normal operation,  $\overline{\text{MUTE}}$  (Pin 16) needs to be toggled to low and then to high again. The error flag is useful for the microcontroller in the system to indicate an abnormal operation and to initiate the audio  $\overline{\text{MUTE}}$  sequence. The device senses the short-circuit condition on the outputs after the LC filter. Typical short-circuit conditions include shorting of the output load and shorting to either PVDD or GND.

### **UNDERVOLTAGE PROTECTION**

The ADAU1513 has an undervoltage protection circuit that senses the undervoltage on PVDD. When the PVDD supply goes below the operating threshold, the output FETs are turned to a high-Z condition. Also, the device issues an error flag by pulling the  $\overline{\rm ERR}$  pin low. This condition is latched. To restore the operation,  $\overline{\rm MUTE}$  (Pin 16) needs to be toggled to low and then to high again.

#### **AUTOMATIC RECOVERY FROM PROTECTIONS**

In certain applications, it is desired for the amplifier to recover itself from thermal protection without the need for system microcontroller intervention.

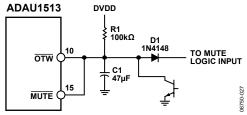

The ADAU1513 thermal protection circuit issues two error signals for this purpose: one thermal warning  $(\overline{OTW})$  and the other thermal shutdown  $(\overline{ERR})$ .

With these two error signals, there are two options for using the protections:

- Option 1: Using OTW

- Option 2: Using ERR

The following sections provide further details of these two options.

### Option 1: Using OTW

The  $\overline{\text{OTW}}$  pin is pulled low when the die temperature reaches 130°C to 135°C This pin can be wired to the  $\overline{\text{MUTE}}$  pin using an RC circuit as shown in Figure 28.

Figure 28. Option 1 Schematic for Autorecovery

The low logic level on  $\overline{OTW}$  also pulls down the  $\overline{MUTE}$  pin. The bridge is shut down and, therefore, starts cooling or the die temperature starts reducing. When it reaches 120°C, the  $\overline{OTW}$  signal starts going high. While this pin is tied to a capacitor with a resistor pulled to DVDD, the voltage on this pin starts rising slowly towards DVDD. When it reaches the input logic high threshold,  $\overline{MUTE}$  is deasserted and the

amplifier starts functioning again. This cycle repeats itself depending on the input signal conditions and the temperature of the die. This option allows part operation that is safely below the shutdown temperature of 150°C and allows the amplifier to recover itself without the need for microcontroller intervention.

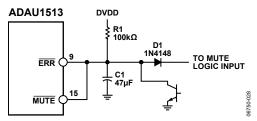

### Option 2: Using ERR

Option 2 is similar to Option 1 if the  $\overline{ERR}$  pin can be tied to MUTE instead of  $\overline{OTW}$ . See the circuit in Figure 29.

Figure 29. Option 2 Schematic for Autorecovery

In this case, the part goes into shutdown mode due to any of the error-generating events like output overcurrent, overtemperature, missing PVDD or DVDD, or clock loss. The part recovers itself based on the same circuit operation in Figure 28.

However, if the part goes into error mode due to overtemperature, then the device would have reached its maximum limit of 150°C (15°C to 20°C higher than Option 1). If it goes into error mode due to an overcurrent from a short circuit on the speaker outputs, then the part will keep itself recycling on and off until the short circuit is removed.

It is possible that, with this operation, the part is subjected to a much higher temperature and current stress continuously. This, in turn, reduces the part's reliability in the long term. Therefore, using Option 1 for autorecovery from the thermal protection and using the system microcontroller to indicate to the user of an error condition is recommended.

### **MUTE AND STDN**

The MUTE and STDN are 3.3 V logic-compatible inputs used to control the turn-on/turn-off for ADAU1513.

The STDN input is active low when the STDN pin is pulled low and the device is in its energy-saving mode. The power stage is in high-Z state. The high logic level input on the STDN pin will wake up the device. The logic circuits are running internally but the power stage is still in high-Z state.

When the  $\overline{\text{MUTE}}$  pin is pulled high, the power stage is active and starts responding to PWM inputs. The low level on the  $\overline{\text{MUTE}}$  pin disables the power stage and is recommended to be used to mute the audio output. See the Power-Up/Power-Down Sequence section for more details.

### POWER-UP/POWER-DOWN SEQUENCE

Figure 30 shows the recommended power-up sequence for the ADAU1513.

Figure 30. Recommended Power-Up Sequence

The ADAU1513 does not have any pop-and-click suppression circuits; therefore, care must be taken during the power-up. The power stage stays in Hi-Z on power-up. However, it is recommended to ensure that  $\overline{STDN}$  and  $\overline{MUTE}$  are held low during initial power-up. First,  $\overline{STDN}$  should be pulled high followed by  $\overline{MUTE}$  to turn on the power stage. The power stage turns on after the  $\overline{MUTE}$  signal is pulled high and responds to PWM inputs after a small propagation delay of 200 µs.

The special turn-on sequence may be necessary depending on the PWM used to prevent the turn-on pop or click. However, if the ADAV4201 processor is used, the processor has a built-in special turn-on PWM sequence. The processor sends a unique PWM input start sequence that ensures soft turn-on.

If another modulator is used, care must be taken to ensure that the modulator has built-in pop-and-click suppression. Also, because the power stage does not track the PWM inputs, it is recommended to use the system microcontroller to ensure that the modulator is ready to send the PWM sequence before turning on the power stage.

Similarly, for muting the amplifier, it may be necessary to supply a special muting PWM sequence for minimum pop and click. The ADAV4201 processor has a built-in feature that takes care of this need. If any other modulator is used, care must be taken during muting of the power stage.

The system microcontroller can be used to handle the mute/unmute of the power stage as well as a modulator.

The error outputs of the power stage should be connected to the microcontroller port. This error flag can be used to inform the modulator that the power stage is shut down and to mute the PWM inputs. On removal of the error condition, the microcontroller should initiate an unmute sequence to minimize pop and click while power stage is turning on/turning off.

The ADAU1513 uses three separate supplies: AVDD (3.3 V analog for internal reference), DVDD (3.3 V digital for control logic and clock oscillator), and PVDD (9 V to 18 V power stage and level shifter). Separate pins are provided for the AVDD,

DVDD, and PVDD supply connections, as well AGND, DGND, and PGND.

In addition, the ADAU1513 incorporates a built-in undervoltage lockout logic on DVDD as well as PVDD. This helps detect undervoltage operation and eliminates the need to have an external mechanism to sense the supplies.

The ADAU1513 monitors the DVDD and PVDD supply voltages and prevents the power stage from turning on if either of the supplies are not present or below the operating threshold. Therefore, if DVDD is missing or below the operating threshold, for example, the power stage will not turn on, even if the PVDD is present or vice versa.

Because this protection is only present on DVDD and PVDD and not on AVDD, shorting both AVDD and DVDD externally or generating AVDD and DVDD from one power source is recommended. This ensures both AVDD and DVDD supplies are tracking each other and avoids the need to monitor the sequence with respect to PVDD. This also ensures minimal pop and click during power-up.

When using separate AVDD and DVDD supplies, ensure that both supplies are stable before unmuting or turning on the power stage.

During power-up, it is recommended to keep  $\overline{STDN}$  and  $\overline{MUTE}$  low to ensure that the power stage stays in high-Z mode.

Similarly, during shutdown, pulling MUTE to logic low before pulling STDN down is recommended. However, where a fault event occurs, the power stage will shut down to protect the part. In this case, depending on the signal level, there is some pop at the speaker.

During shutdown of the power supplies to reduce power consumption, it is highly recommended to mute the amplifier first, followed by pulling \$\overline{STDN}\$ low before shutting down any of the supplies. After MUTE is pulled low, the power supplies can be shut down in the following order: PVDD, DVDD, then AVDD. Where AVDD and DVDD are generated from a single source, ensure that PVDD is tuned off before DVDD and AVDD, and after issuing \$\overline{MUTE}\$ and \$\overline{STDN}\$.

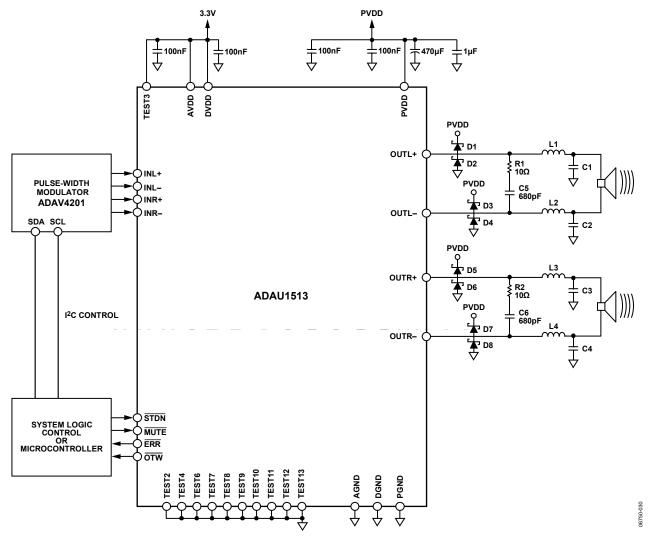

### APPLICATIONS INFORMATION

Refer to the application schematic in Figure 31 for details on connections and component values. For details on the PWM modulator part, refer to the ADAV4201 data sheet.

For applications with PVDD > 15 V, add components R1 and R2 =  $10 \Omega$  typical, C5 and C6 =  $680 \mu$ F typical, and D1 through D8 = CRS01/02.

Figure 31. Application Schematic

Table 8. Suggested Low-Pass Filter Values

| Load Impedance ( $\Omega$ ) | Inductance L1 to L4 (μH) | Capacitance C1 to C4 (μF) |

|-----------------------------|--------------------------|---------------------------|

| 4                           | 10                       | 1.5                       |

| 6                           | 15                       | 1                         |

| 8                           | 22                       | 0.68                      |

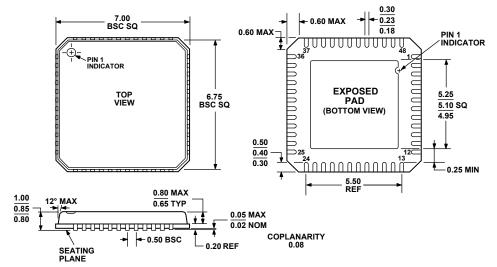

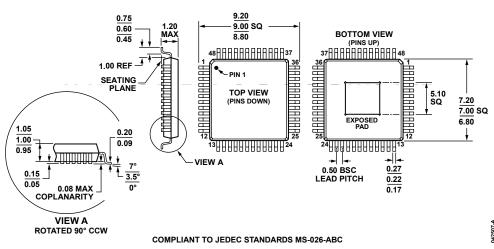

### **OUTLINE DIMENSIONS**

#### COMPLIANT TO JEDEC STANDARDS MO-220-VKKD-2

Figure 32. 48-Lead Lead Frame Chip Scale Package [LFCSP\_VQ] 7 mm × 7 mm Body, Very Thin Quad (CP-48-1) Dimensions shown in millimeters

Figure 33. 48-Lead Thin Quad Flat Package, Exposed Pad [TQFP\_EP] (SV-48-5) Dimensions shown in millimeters

### **ORDERING GUIDE**

| Model                         | Temperature<br>Range | Package Description                                                     | Package<br>Option |

|-------------------------------|----------------------|-------------------------------------------------------------------------|-------------------|

| ADAU1513ACPZ <sup>1</sup>     | -40°C to +85°C       | 48-Lead Lead Frame Chip Scale Package [LFCSP_VQ]                        | CP-48-1           |

| ADAU1513ACPZ-RL <sup>1</sup>  | -40°C to +85°C       | 48-Lead Lead Frame Chip Scale Package [LFCSP_VQ], 13" Tape and Reel     | CP-48-1           |

| ADAU1513ACPZ-RL7 <sup>1</sup> | -40°C to +85°C       | 48-Lead Lead Frame Chip Scale Package [LFCSP_VQ], 7"Tape and Reel       | CP-48-1           |

| ADAU1513ASVZ <sup>1</sup>     | -40°C to +85°C       | 48-Lead Thin Quad Flat Package, Exposed Pad [TQFP_EP]                   | SV-48-5           |

| ADAU1513ASVZ-RL <sup>1</sup>  | -40°C to +85°C       | 48-Lead Thin Quad Flat Package, Exposed Pad [TQFP_EP], 13"Tape and Reel | SV-48-5           |

| ADAU1513ASVZ-RL7 <sup>1</sup> | -40°C to +85°C       | 48-Lead Thin Quad Flat Package, Exposed Pad [TQFP_EP], 7"Tape and Reel  | SV-48-5           |

$<sup>^{1}</sup>$  Z = RoHS Compliant Part.