## Dual, 550kHz, 2-Phase Synchronous Regulators

#### FEATURES

- Dual, 180° Phased Controllers Reduce Required Input Capacitance and Power Supply Induced Noise

- OPTI-LOOP® Compensation Minimizes C<sub>OUT</sub>

- ±1% Output Voltage Accuracy (LTC3728LC)

- Power Good Output Voltage Indicator

- Phase-Lockable Fixed Frequency 250kHz to 550kHz

- Dual N-Channel MOSFET Synchronous Drive

- Wide V<sub>IN</sub> Range: 4.5V to 28V Operation

- Very Low Dropout Operation: 99% Duty Cycle

- Adjustable Soft-Start Current Ramping

- Foldback Output Current Limiting

- Latched Short-Circuit Shutdown with Defeat Option

- Output Overvoltage Protection

- Low Shutdown I<sub>Ω</sub>: 20μA

- 5V and 3.3V Standby Regulators

- 3 Selectable Operating Modes: Constant Frequency, Burst Mode® Operation and PWM

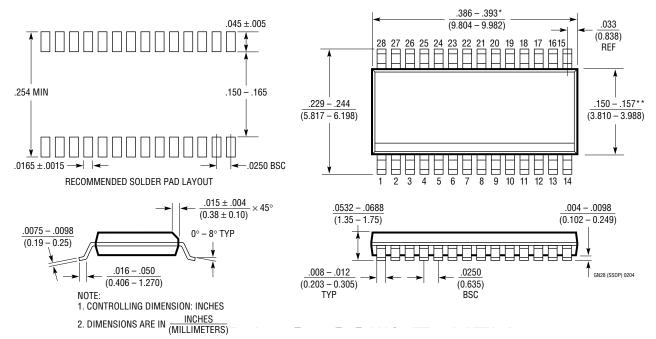

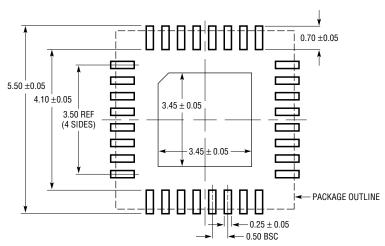

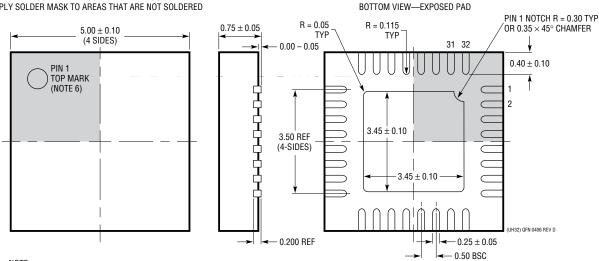

- 5mm × 5mm QFN and 28-Lead Narrow SSOP Packages

## **APPLICATIONS**

- Notebook and Palmtop Computers

- Telecom Systems

- Portable Instruments

- Battery-Operated Digital Devices

- DC Power Distribution Systems

## DESCRIPTION

The LTC®3728L/LTC3728LX are dual high performance step-down switching regulator controllers that drive all N-channel synchronous power MOSFET stages. A constant frequency current mode architecture allows phase-lockable frequency of up to 550kHz. Power loss and noise due to the ESR of the input capacitors are minimized by operating the two controller output stages out of phase.

OPTI-LOOP compensation allows the transient response to be optimized over a wide range of output capacitance and ESR values. The precision 0.8V reference and power good output indicator are compatible with future microprocessor generations, and a wide 4.5V to 28V (30V maximum) input supply range encompasses all battery chemistries.

A RUN/SS pin for each controller provides both soft-start and optional timed, short-circuit shutdown. Current foldback limits MOSFET dissipation during short-circuit conditions when overcurrent latchoff is disabled. Output overvoltage protection circuitry latches on the bottom MOSFET until V<sub>OUT</sub> returns to normal. The FCB mode pin can select among Burst Mode, constant frequency mode and continuous inductor current mode or regulate a secondary winding. The LTC3728L/LTC3728LX include a power good output pin that indicates when both outputs are within 7.5% of their designed set point.

7, LT, LTC, LTM, Burst Mode and OPTI-LOOP are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners

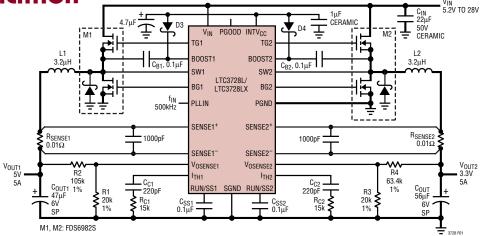

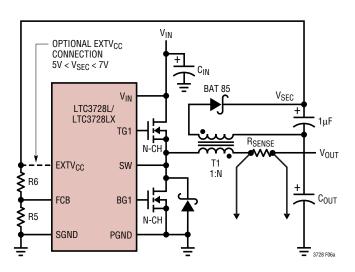

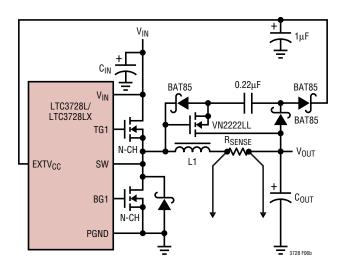

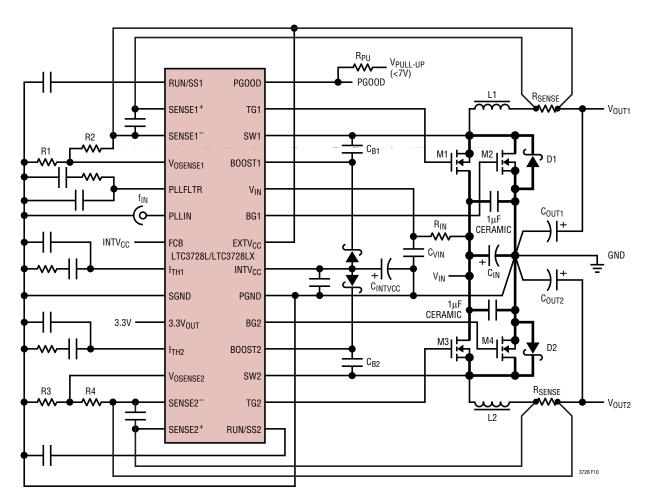

## TYPICAL APPLICATION

Figure 1. High Efficiency Dual 5V/3.3V Step-Down Converter

## **ABSOLUTE MAXIMUM RATINGS** (Note 1)

| Input Supply Voltage $(V_{IN})$                                           |

|---------------------------------------------------------------------------|

| Top Side Driver Voltages                                                  |

| (BOOST1, BOOST2) 36V to −0.3V                                             |

| Switch Voltage (SW1, SW2) 30V to −5V                                      |

| INTV <sub>CC</sub> , EXTV <sub>CC</sub> , RUN/SS1, RUN/SS2, (BOOST1-SW1), |

| (BOOST2-SW2), PGOOD 7V to −0.3V                                           |

| SENSE1+, SENSE2+, SENSE1-,                                                |

| SENSE2 - Voltages (1.1)INTV <sub>CC</sub> to -0.3V                        |

| PLLIN, PLLFLTR, FCB, Voltage INTV <sub>CC</sub> to −0.3V                  |

|                                                                           |

| I <sub>TH1</sub> , I <sub>TH2</sub> , V <sub>OSENSE1</sub> , V <sub>OSENSE2</sub> Voltages<br>Peak Output Current <10μs (TG1, TG2, BG | 2.7V to -0.3V<br>31. BG2) 3A |

|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| INTV <sub>CC</sub> Peak Output Current                                                                                                |                              |

| Operating Temperature Range (Note 7)                                                                                                  |                              |

| LTC3728LC/LTC3728LXC                                                                                                                  | 0°C to 85°C                  |

| LTC3728LE/LTC3728LI                                                                                                                   | -40°C to 85°C                |

| Junction Temperature (Note 2)                                                                                                         | 125°C                        |

| Storage Temperature Range                                                                                                             | 65°C to 125°C                |

| Reflow Peak Body Temperature (UH Packa                                                                                                | age) 260°C                   |

| Lead Temperature (Soldering, 10 sec)                                                                                                  |                              |

| (GN Package)                                                                                                                          | 300°C                        |

|                                                                                                                                       |                              |

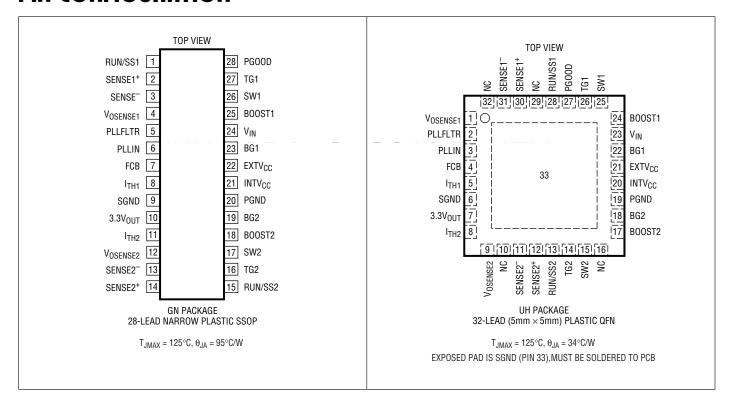

## PIN CONFIGURATION

## **ORDER INFORMATION**

| LEAD FREE FINISH  | TAPE AND REEL      | PART MARKING | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|-------------------|--------------------|--------------|---------------------------------|-------------------|

| LTC3728LCGN#PBF   | LTC3728LCGN#TRPBF  |              | 28-Lead Narrow Plastic SSOP     | 0°C to 85°C       |

| LTC3728LEGN#PBF   | LTC3728LEGN#TRPBF  |              | 28-Lead Narrow Plastic SSOP     | -40°C to 85°C     |

| LTC3728LIGN#PBF   | LTC3728LIGN#TRPBF  |              | 28-Lead Narrow Plastic SSOP     | -40°C to 85°C     |

| LTC3728LCUH#PBF   | LTC3728LCUH#TRPBF  | 3728L        | 32-Lead (5mm × 5mm) Plastic QFN | 0°C to 85°C       |

| LTC3728LEUH#PBF   | LTC3728LEUH#TRPBF  | 3728LE       | 32-Lead (5mm × 5mm) Plastic QFN | -40°C to 85°C     |

| LTC3728LIUH#PBF   | LTC3728LIUH#TRPBF  | 3728LI       | 32-Lead (5mm × 5mm) Plastic QFN | -40°C to 85°C     |

| LTC3728LXCUH#PBF  | LTC3728LXCUH#TRPBF | 3728LX       | 32-Lead (5mm × 5mm) Plastic QFN | 0°C to 85°C       |

| LEAD BASED FINISH | TAPE AND REEL      | PART MARKING | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

| LTC3728LCGN       | LTC3728LCGN#TR     |              | 28-Lead Narrow Plastic SSOP     | 0°C to 85°C       |

| LTC3728LEGN       | LTC3728LEGN#TR     |              | 28-Lead Narrow Plastic SSOP     | -40°C to 85°C     |

| LTC3728LIGN       | LTC3728LIGN#TR     |              | 28-Lead Narrow Plastic SSOP     | -40°C to 85°C     |

| LTC3728LCUH       | LTC3728LCUH#TR     | 3728L        | 32-Lead (5mm × 5mm) Plastic QFN | 0°C to 85°C       |

| LTC3728LEUH       | LTC3728LEUH#TR     | 3728LE       | 32-Lead (5mm × 5mm) Plastic QFN | -40°C to 85°C     |

| LTC3728LIUH       | LTC3728LIUH#TR     | 3728LI       | 32-Lead (5mm × 5mm) Plastic QFN | -40°C to 85°C     |

| LTC3728LXCUH      | LTC3728LXCUH#TR    | 3728LX       | 32-Lead (5mm × 5mm) Plastic QFN | 0°C to 85°C       |

Consult LTC Marketing for parts specified with wider operating temperature ranges.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The ullet denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{IN} = 15V$ , $V_{RUN/SS1,\ 2} = 5V$ unless otherwise noted.

| SYMBOL                                         | PARAMETER                                                                | CONDITIONS                                                                                                                                  |   | MIN            | TYP            | MAX            | UNITS    |

|------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---|----------------|----------------|----------------|----------|

| Main Control L                                 | oops                                                                     |                                                                                                                                             |   |                |                |                |          |

| V <sub>OSENSE1, 2</sub>                        | Regulated Feedback Voltage                                               | (Note 3); I <sub>TH1, 2</sub> Voltage = 1.2V (LTC3728LC)<br>(Note 3); I <sub>TH1, 2</sub> Voltage = 1.2V<br>(LTC3728LE/LTC3728LX/LTC3728LI) | • | 0.792<br>0.788 | 0.800<br>0.800 | 0.808<br>0.812 | V        |

| I <sub>VOSENSE1, 2</sub>                       | Feedback Current                                                         | (Note 3)                                                                                                                                    |   |                | -5             | -50            | nA       |

| V <sub>REFLNREG</sub>                          | Reference Voltage Line Regulation                                        | V <sub>IN</sub> = 3.6V to 30V (Note 3)                                                                                                      |   |                | 0.002          | 0.02           | %/V      |

| V <sub>LOADREG</sub>                           | Output Voltage Load Regulation                                           | (Note 3) Measured in Servo Loop; $\Delta I_{TH}$ Voltage = 1.2V to 0.7V Measured in Servo Loop; $\Delta I_{TH}$ Voltage = 1.2V to 2.0V      | • |                | 0.1<br>-0.1    | 0.5<br>-0.5    | %<br>%   |

| 9 <sub>m1, 2</sub>                             | Transconductance Amplifier g <sub>m</sub>                                | I <sub>TH1, 2</sub> = 1.2V; Sink/Source 5uA; (Note 3)                                                                                       |   |                | 1.3            |                | mmho     |

| 9mGBW1, 2                                      | Transconductance Amplifier GBW                                           | I <sub>TH1, 2</sub> = 1.2V; (Note 3)                                                                                                        |   |                | 3              |                | MHz      |

| IQ                                             | Input DC Supply Current<br>Normal Mode<br>Shutdown                       | (Note 4) V <sub>IN</sub> = 15V; EXTV <sub>CC</sub> Tied to V <sub>OUT1</sub> ; V <sub>OUT1</sub> = 5V V <sub>RUN/SS1, 2</sub> = 0V          |   |                | 450<br>20      | 35             | μA<br>μA |

| V <sub>FCB</sub>                               | Forced Continuous Threshold                                              |                                                                                                                                             | • | 0.76           | 0.800          | 0.84           | V        |

| I <sub>FCB</sub>                               | Forced Continuous Pin Current                                            | V <sub>FCB</sub> = 0.85V                                                                                                                    |   | -0.50          | -0.18          | -0.1           | μА       |

| V <sub>BINHIBIT</sub>                          | Burst Inhibit (Constant Frequency)<br>Threshold                          | Measured at FCB pin                                                                                                                         |   |                | 4.3            | 4.8            | V        |

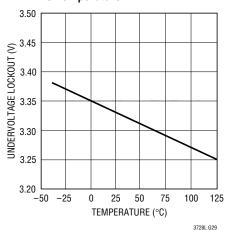

| UVLO                                           | Undervoltage Lockout                                                     | V <sub>IN</sub> Ramping Down                                                                                                                | • |                | 3.5            | 4              | V        |

| $V_{OVL}$                                      | Feedback Overvoltage Lockout                                             | Measured at V <sub>OSENSE1, 2</sub>                                                                                                         | • | 0.84           | 0.86           | 0.88           | V        |

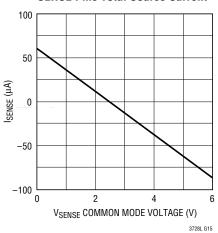

| I <sub>SENSE</sub>                             | Sense Pins Total Source Current                                          | (Each Channel); $V_{SENSE1-, 2} = V_{SENSE1+, 2} = 0V$                                                                                      |   | -90            | -60            |                | μА       |

| DF <sub>MAX</sub>                              | Maximum Duty Factor                                                      | In Dropout                                                                                                                                  |   | 98             | 99.4           |                | %        |

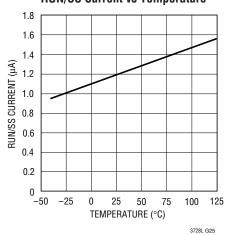

| I <sub>RUN/SS1, 2</sub>                        | Soft-Start Charge Current                                                | V <sub>RUN/SS1, 2</sub> = 1.9V                                                                                                              |   | 0.5            | 1.2            |                | μА       |

| V <sub>RUN/SS1, 2</sub> ON                     | RUN/SS Pin ON Threshold                                                  | V <sub>RUN/SS1</sub> , V <sub>RUN/SS2</sub> Rising                                                                                          |   | 1.0            | 1.5            | 2.0            | V        |

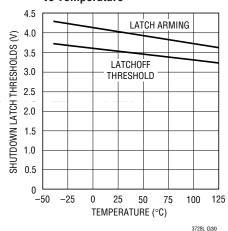

| V <sub>RUN/SS1, 2</sub> LT                     | RUN/SS Pin Latchoff Arming Threshold                                     | V <sub>RUN/SS1</sub> , V <sub>RUN/SS2</sub> Rising from 3V                                                                                  |   |                | 4.1            | 4.75           | V        |

| I <sub>SCL1, 2</sub>                           | RUN/SS Discharge Current                                                 | Soft Short Condition V <sub>OSENSE1, 2</sub> = 0.5V;<br>V <sub>RUN/SS1, 2</sub> = 4.5V                                                      |   | 0.5            | 2              | 4              | μА       |

| I <sub>SDLHO</sub>                             | Shutdown Latch Disable Current                                           | V <sub>OSENSE1, 2</sub> = 0.5V                                                                                                              |   |                | 1.6            | 5              | μΑ       |

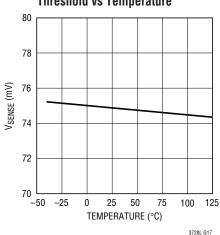

| V <sub>SENSE(MAX)</sub>                        | Maximum Current Sense Threshold                                          | V <sub>OSENSE1, 2</sub> = 0.7V,V <sub>SENSE1</sub> -, 2- = 5V<br>V <sub>OSENSE1, 2</sub> = 0.7V,V <sub>SENSE1</sub> -, 2- = 5V              | • | 65<br>62       | 75<br>75       | 85<br>88       | mV<br>mV |

| TG1, 2 t <sub>r</sub><br>TG1, 2 t <sub>f</sub> | TG Transition Time:<br>Rise Time<br>Fall Time                            | (Note 5)<br>C <sub>LOAD</sub> = 3300pF<br>C <sub>LOAD</sub> = 3300pF                                                                        |   |                | 55<br>55       | 100<br>100     | ns<br>ns |

| BG1, 2 t <sub>r</sub><br>BG1, 2 t <sub>f</sub> | BG Transition Time:<br>Rise Time<br>Fall Time                            | (Note 5)<br>C <sub>LOAD</sub> = 3300pF<br>C <sub>LOAD</sub> = 3300pF                                                                        |   |                | 45<br>45       | 100<br>90      | ns<br>ns |

| TG/BG t <sub>1D</sub>                          | Top Gate Off to Bottom Gate On Delay<br>Synchronous Switch-On Delay Time | C <sub>LOAD</sub> = 3300pF Each Driver                                                                                                      |   |                | 80             |                | ns       |

| BG/TG t <sub>2D</sub>                          | Bottom Gate Off to Top Gate On Delay<br>Top Switch-On Delay Time         | C <sub>LOAD</sub> = 3300pF Each Driver                                                                                                      |   |                | 80             |                | ns       |

| t <sub>ON(MIN)</sub>                           | Minimum On-Time                                                          | Tested with a Square Wave (Note 6)                                                                                                          |   |                | 100            |                | ns       |

|                                                |                                                                          | · ·                                                                                                                                         |   |                |                |                |          |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{IN} = 15V$ , $V_{RUN/SS1,\ 2} = 5V$ unless otherwise noted.

| SYMBOL                  | PARAMETER                                                                  | CONDITIONS                                                                                                                             |   | MIN     | TYP         | MAX         | UNITS    |

|-------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---|---------|-------------|-------------|----------|

| INTV <sub>CC</sub> Line | ar Regulator                                                               |                                                                                                                                        |   |         |             |             |          |

| V <sub>INTVCC</sub>     | Internal V <sub>CC</sub> Voltage                                           | 6V < V <sub>IN</sub> < 30V, V <sub>EXTVCC</sub> = 4V                                                                                   |   | 4.8     | 5.0         | 5.2         | V        |

| V <sub>LDO</sub> INT    | INTV <sub>CC</sub> Load Regulation                                         | I <sub>CC</sub> = 0 to 20mA, V <sub>EXTVCC</sub> = 4V                                                                                  |   |         | 0.2         | 2.0         | %        |

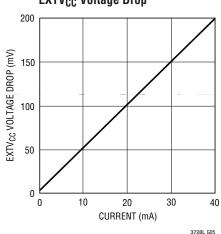

| V <sub>LD0</sub> EXT    | EXTV <sub>CC</sub> Voltage Drop                                            | I <sub>CC</sub> = 20mA, V <sub>EXTVCC</sub> = 5V                                                                                       |   |         | 100         | 200         | mV       |

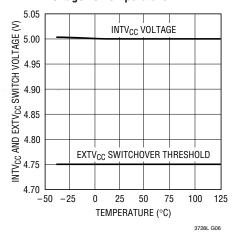

| V <sub>EXTVCC</sub>     | EXTV <sub>CC</sub> Switchover Voltage                                      | I <sub>CC</sub> = 20mA, EXTV <sub>CC</sub> Ramping Positive                                                                            | • | 4.5     | 4.7         |             | V        |

| V <sub>LDOHYS</sub>     | EXTV <sub>CC</sub> Hysteresis                                              |                                                                                                                                        |   |         | 0.2         |             | V        |

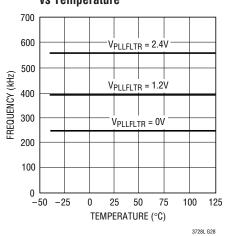

| Oscillator an           | d Phase-Locked Loop                                                        |                                                                                                                                        | • |         |             |             |          |

| f <sub>NOM</sub>        | Nominal Frequency                                                          | V <sub>PLLFLTR</sub> = 1.2V                                                                                                            |   | 360     | 400         | 440         | kHz      |

| $f_{LOW}$               | Lowest Frequency                                                           | V <sub>PLLFLTR</sub> = 0V                                                                                                              |   | 230     | 260         | 290         | kHz      |

| f <sub>HIGH</sub>       | Highest Frequency                                                          | $V_{PLLFLTR} \ge 2.4V$                                                                                                                 |   | 480     | 550         | 590         | kHz      |

| R <sub>PLLIN</sub>      | PLLIN Input Resistance                                                     |                                                                                                                                        |   |         | 50          |             | kΩ       |

| I <sub>PLLFLTR</sub>    | Phase Detector Output Current<br>Sinking Capability<br>Sourcing Capability | f <sub>PLLIN</sub> < f <sub>OSC</sub><br>f <sub>PLLIN</sub> > f <sub>OSC</sub>                                                         |   |         | -15<br>15   |             | μA<br>μA |

| 3.3V Linear             | Regulator                                                                  |                                                                                                                                        | ' |         |             |             |          |

| V <sub>3.30UT</sub>     | 3.3V Regulator Output Voltage                                              | No Load                                                                                                                                | • | 3.2     | 3.35        | 3.45        | V        |

| V <sub>3.3IL</sub>      | 3.3V Regulator Load Regulation                                             | I <sub>3.3</sub> = 0 to 10mA                                                                                                           |   |         | 0.5         | 2           | %        |

| V <sub>3.3VL</sub>      | 3.3V Regulator Line Regulation                                             | 6V < V <sub>IN</sub> < 30V                                                                                                             |   |         | 0.05        | 0.2         | %        |

| PGOOD Outp              | ut                                                                         |                                                                                                                                        |   |         |             |             |          |

| $V_{PGL}$               | PGOOD Voltage Low                                                          | I <sub>PGOOD</sub> = 2mA                                                                                                               |   |         | 0.1         | 0.3         | V        |

| I <sub>PGOOD</sub>      | PGOOD Leakage Current                                                      | V <sub>PG00D</sub> = 5V-                                                                                                               |   | -       |             | ±1          | μА       |

| V <sub>PG</sub>         | PGOOD Trip Level, Either Controller                                        | V <sub>OSENSE</sub> with Respect to Set Output Voltage<br>V <sub>OSENSE</sub> Ramping Negative<br>V <sub>OSENSE</sub> Ramping Positive |   | -6<br>6 | -7.5<br>7.5 | -9.5<br>9.5 | %<br>%   |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:**  $T_J$  is calculated from the ambient temperature  $T_A$  and power dissipation  $P_D$  according to the following formulas:

LTC3728LUH/LTC3728LXUH:  $T_J = T_A + (P_D \cdot 34^{\circ}C/W)$

LTC3728LGN:  $T_J = T_A + (P_D \bullet 95^{\circ}C/W)$

**Note 3:** The IC is tested in a feedback loop that servos  $V_{ITH1,\,2}$  to a specified voltage and measures the resultant  $V_{OSENSE1,\,2}$ .

**Note 4:** Dynamic supply current is higher due to the gate charge being delivered at the switching frequency. See Applications Information.

**Note 5:** Rise and fall times are measured using 10% and 90% levels. Delay times are measured using 50% levels.

**Note 6:** The minimum on-time is tested under an ideal condition without external power FETs. It can be larger when the IC is operating in an actual circuit. See Minimum On-Time Considerations in the Applications Information section.

**Note 7:** The LTC3728LC/LTC3728LXC are guaranteed to meet performance specifications from 0°C to 85°C. The LTC3728LE is guaranteed to meet performance specifications over the –40°C to 85°C operating temperature range as assured by design, characterization and correlation with statistical process controls. The LTC3728LI is guaranteed to meet performance specifications over the –40°C to 85°C operating temperature range.

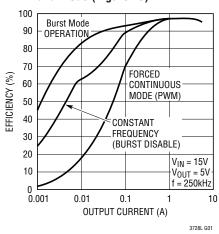

## Efficiency vs Output Current and Mode (Figure 13)

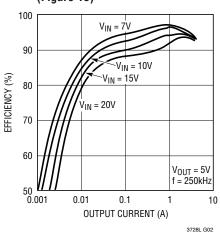

## Efficiency vs Output Current (Figure 13)

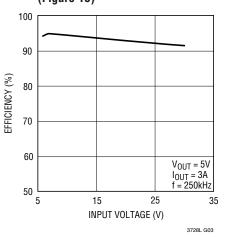

## Efficiency vs Input Voltage (Figure 13)

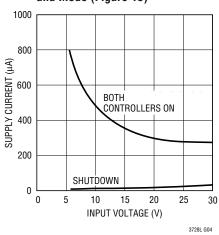

Supply Current vs Input Voltage and Mode (Figure 13)

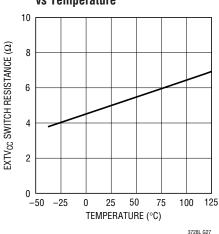

EXTV<sub>CC</sub> Voltage Drop

INTV<sub>CC</sub> and EXTV<sub>CC</sub> Switch Voltage vs Temperature

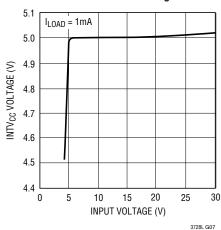

**Internal 5V LDO Line Regulation**

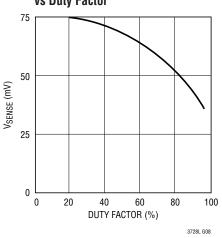

Maximum Current Sense Threshold vs Duty Factor

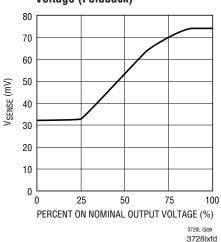

Maximum Current Sense Threshold vs Percent of Nominal Output Voltage (Foldback)

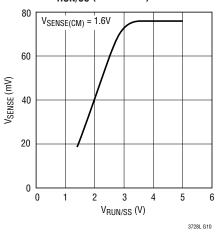

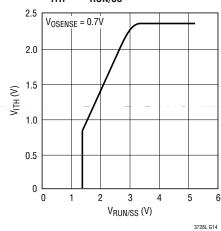

## Maximum Current Sense Threshold vs V<sub>RUN/SS</sub> (Soft-Start)

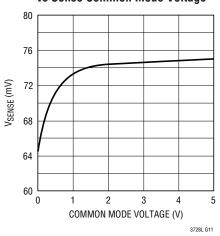

## Maximum Current Sense Threshold vs Sense Common Mode Voltage

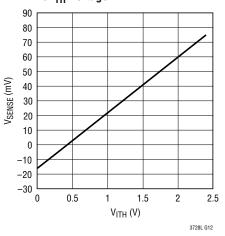

## Current Sense Threshold vs I<sub>TH</sub> Voltage

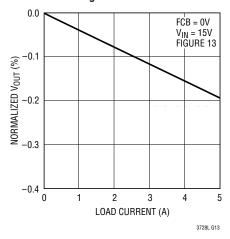

Load Regulation

V<sub>ITH</sub> vs V<sub>RUN/SS</sub>

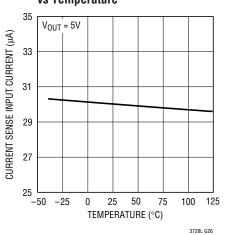

**SENSE Pins Total Source Current**

Maximum Current Sense Threshold vs Temperature

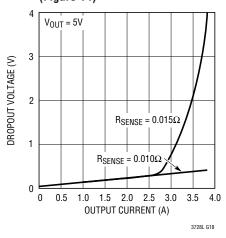

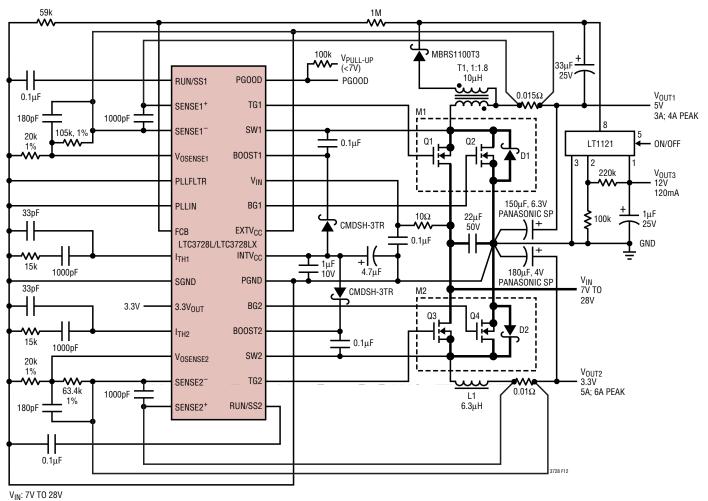

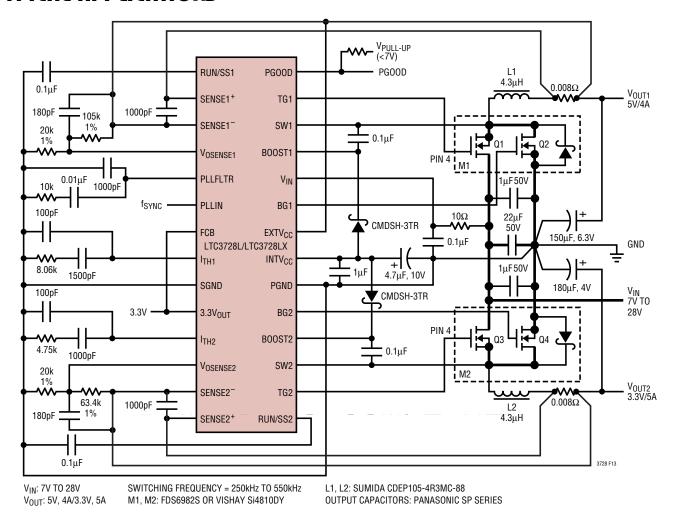

Dropout Voltage vs Output Current (Figure 14)

**RUN/SS Current vs Temperature**

$V_{OUT} = 5V$

$I_{OUT5} = I_{OUT3.3} = 2A$

## $\mathsf{EXTV}_\mathsf{CC}$ Switch Resistance vs Temperature

#### **Oscillator Frequency** vs Temperature

#### **Undervoltage Lockout** vs Temperature

#### **Shutdown Latch Thresholds** vs Temperature

## PIN FUNCTIONS

**V**<sub>OSENSE1</sub>, **V**<sub>OSENSE2</sub>: Error Amplifier Feedback Input. Receives the remotely-sensed feedback voltage for each controller from an external resistive divider across the output.

**PLLFLTR:** Filter Connection for Phase-Locked Loop. Alternatively, this pin can be driven with an AC or DC voltage source to vary the frequency of the internal oscillator.

**PLLIN:** External Synchronization Input to Phase Detector. This pin is internally terminated to SGND with  $50k\Omega$ . The phase-locked loop will force the rising top gate signal of controller 1 to be synchronized with the rising edge of the PLLIN signal.

**FCB:** Forced Continuous Control Input. This input acts on both controllers and is normally used to regulate a secondary winding. Pulling this pin below 0.8V will force continuous synchronous operation.

I<sub>TH1</sub>, I<sub>TH2</sub>: Error Amplifier Output and Switching Regulator Compensation Point. Each associated channels' current comparator trip point increases with this control voltage.

**SGND:** Small Signal Ground. Common to both controllers, this pin must be routed separately from high current grounds to the common (-) terminals of the  $C_{OUT}$  capacitors.

**3.3V<sub>OUT</sub>:** Lnear Regulator Output. Capable of supplying 10mA DC with peak currents as high as 50mA.

NC: No Connect.

**SENSE2**<sup>-</sup>, **SENSE1**<sup>-</sup>: The (-) Input to the Differential Current Comparators.

**SENSE2+**, **SENSE1+**: The (+) Input to the Differential Current Comparators. The I<sub>TH</sub> pin voltage and controlled offsets between the SENSE<sup>-</sup> and SENSE<sup>+</sup> pins in conjunction with R<sub>SENSE</sub> set the current trip threshold.

**RUN/SS2**, **RUN/SS1**: Combination of soft-start, run control inputs and short-circuit detection timers. A capacitor to ground at each of these pins sets the ramp time to full output current. Forcing either of these pins back below 1.0V causes the IC to shut down the circuitry required for that particular controller. Latchoff overcurrent protection

is also invoked via this pin as described in the Applications Information section.

**TG2, TG1:** High Current Gate Drives for Top N-Channel MOSFETs. These are the outputs of floating drivers with a voltage swing equal to  $INTV_{CC} - 0.5V$  superimposed on the switch node voltage SW.

**SW2**, **SW1**: Switch Node Connections to Inductors. Voltage swing at these pins is from a Schottky diode (external) voltage drop below ground to  $V_{IN}$ .

**BOOST2**, **BOOST1**: Bootstrapped Supplies to the Top Side Floating Drivers. Capacitors are connected between the boost and switch pins and Schottky diodes are tied between the boost and  $INTV_{CC}$  pins. Voltage swing at the boost pins is from  $INTV_{CC}$  to  $(V_{IN} + INTV_{CC})$ .

**BG2**, **BG1**: High Current Gate Drives for Bottom (Synchronous) N-Channel MOSFETs. Voltage swing at these pins is from ground to  $INTV_{CC}$ .

**PGND:** Driver Power Ground. Connects to the sources of bottom (synchronous) N-channel MOSFETs, anodes of the Schottky rectifiers and the (-) terminal(s) of  $C_{IN}$ .

**INTV**<sub>CC</sub>: Output of the Internal 5V Linear Low Dropout Regulator and the EXTV<sub>CC</sub> Switch. The driver and control circuits are powered from this voltage source. Must be decoupled to power ground with a minimum of  $4.7\mu F$  tantalum or other low ESR capacitor.

**EXTV**<sub>CC</sub>: External Power Input to an Internal Switch Connected to INTV<sub>CC</sub>. This switch closes and supplies  $V_{CC}$  power, bypassing the internal low dropout regulator, whenever EXTV<sub>CC</sub> is higher than 4.7V. See EXTV<sub>CC</sub> connection in Applications section. Do not exceed 7V on this pin.

**V**<sub>IN</sub>: Main Supply Pin. A bypass capacitor should be tied between this pin and the signal ground pin.

**PG00D:** Open-Drain Logic Output. PG00D is pulled to ground when the voltage on either  $V_{OSENSE}$  pin is not within  $\pm 7.5\%$  of its set point.

**Exposed Pad (UH Package Only)**: Signal Ground. Must be soldered to the PCB, providing a local ground for the control components of the IC, and be tied to the PGND pin under the IC.

LINEAR

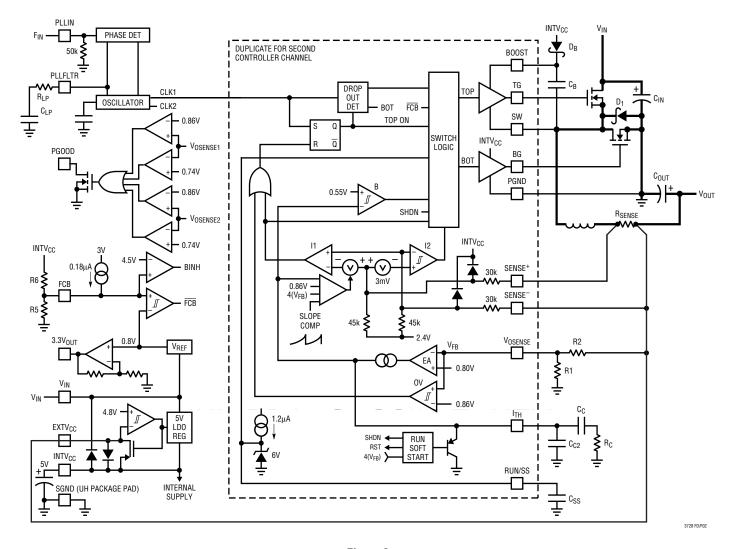

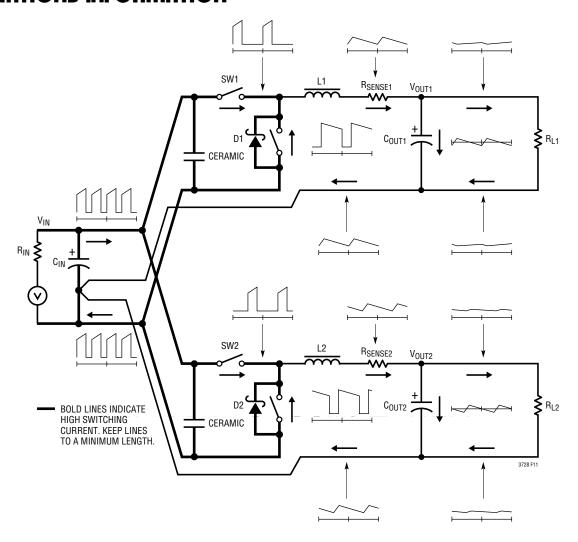

## **FUNCTIONAL DIAGRAM**

Figure 2

#### **Main Control Loop**

The IC uses a constant frequency, current mode stepdown architecture with the two controller channels operating 180 degrees out of phase. During normal operation, each top MOSFET is turned on when the clock for that channel sets the RS latch, and turned off when the main current comparator, I<sub>1</sub>, resets the RS latch. The peak inductor current at which I<sub>1</sub> resets the RS latch is controlled by the voltage on the  $I_{TH}$  pin, which is the output of each error amplifier EA. The V<sub>OSENSE</sub> pin receives the voltage feedback signal, which is compared to the internal reference voltage by the EA. When the load current increases, it causes a slight decrease in V<sub>OSENSE</sub> relative to the 0.8V reference, which in turn causes the  $I_{TH}$  voltage to increase until the average inductor current matches the new load current. After the top MOSFET has turned off, the bottom MOSFET is turned on until either the inductor current starts to reverse, as indicated by current comparator  $I_2$ , or the beginning of the next cycle.

The top MOSFET drivers are biased from floating bootstrap capacitor  $C_B$ , which normally is recharged during each off cycle through an external diode when the top MOSFET turns off. As  $V_{IN}$  decreases to a voltage close to  $V_{OUT}$ , the loop may enter dropout and attempt to turn on the top MOSFET continuously. The dropout detector detects this and forces the top MOSFET off for about 400ns every tenth cycle to allow  $C_B$  to recharge.

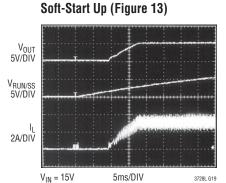

The main control loop is shut down by pulling the RUN/SS pin low. Releasing RUN/SS allows an internal 1.2 $\mu$ A current source to charge soft-start capacitor C<sub>SS</sub>. When C<sub>SS</sub> reaches 1.5V, the main control loop is enabled with the I<sub>TH</sub> voltage clamped at approximately 30% of its maximum value. As C<sub>SS</sub> continues to charge, the I<sub>TH</sub> pin voltage is gradually released allowing normal, full-current operation. When both RUN/SS1 and RUN/SS2 are low, all controller functions are shut down, including the 5V and 3.3V regulators.

#### **Low Current Operation**

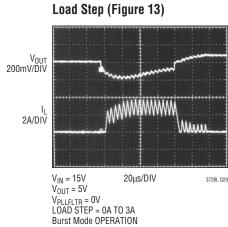

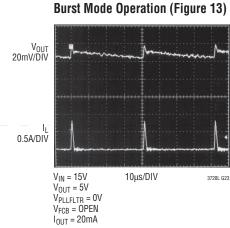

The FCB pin is a multifunction pin providing two functions: 1) to provide regulation for a secondary winding by temporarily forcing continuous PWM operation on both controllers; and 2) to select between two modes of low current operation. When the FCB pin voltage is below 0.8V, the controller forces continuous PWM current mode operation. In this mode, the top and bottom MOSFETs are alternately turned on to maintain the output voltage independent of direction of inductor current. When the FCB pin is below V<sub>INTVCC</sub> – 2V but greater than 0.8V, the controller enters Burst Mode operation. Burst Mode operation sets a minimum output current level before inhibiting the top switch and turns off the synchronous MOSFET(s) when the inductor current goes negative. This combination of requirements will, at low currents, force the I<sub>TH</sub> pin below a voltage threshold that will temporarily inhibit turn-on of both output MOSFETs until the output voltage drops. There is 60mV of hysteresis in the burst comparator B tied to the  $I_{TH}$  pin. This hysteresis produces output signals to the MOSFETs that turn them on for several cycles, followed by a variable "sleep" interval depending upon the load current. The resultant output voltage ripple is held to a very small value by having the hysteretic comparator after the error amplifier gain block.

#### **Frequency Synchronization**

The phase-locked loop allows the internal oscillator to be synchronized to an external source via the PLLIN pin. The output of the phase detector at the PLLFLTR pin is also the DC frequency control input of the oscillator that operates over a 260kHz to 550kHz range corresponding to a DC voltage input from 0V to 2.4V. When locked, the PLL aligns the turn on of the top MOSFET to the rising edge of the synchronizing signal. When PLLIN is left open, the PLLFLTR pin goes low, forcing the oscillator to minimum frequency.

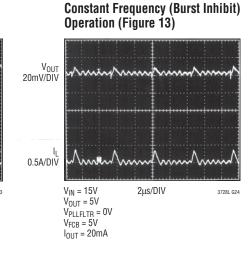

#### **Constant Frequency Operation**

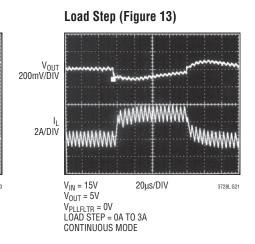

When the FCB pin is tied to INTV<sub>CC</sub>, Burst Mode operation is disabled and the forced minimum output current requirement is removed. This provides constant frequency, discontinuous current (preventing reverse inductor current) operation over the widest possible output current range. This constant frequency operation is not as efficient as Burst Mode operation, but does provide a lower noise, constant frequency operating mode down to approximately 1% of the designed maximum output current.

#### **Continuous Current (PWM) Operation**

Tying the FCB pin to ground will force continuous current operation. This is the least efficient operating mode, but may be desirable in certain applications. The output can source or sink current in this mode. When sinking current while in forced continuous operation, current will be forced back into the main power supply potentially boosting the input supply to dangerous voltage levels—BEWARE!

### INTV<sub>CC</sub>/EXTV<sub>CC</sub> Power

Power for the top and bottom MOSFET drivers and most other internal circuitry is derived from the  $INTV_{CC}$  pin. When the  $EXTV_{CC}$  pin is left open, an internal 5V low dropout linear regulator supplies  $INTV_{CC}$  power. If  $EXTV_{CC}$  is taken above 4.7V, the 5V regulator is turned off and an internal switch is turned on connecting  $EXTV_{CC}$  to  $INTV_{CC}$ . This allows the  $INTV_{CC}$  power to be derived from a high efficiency external source such as the output of the regulator itself or a secondary winding, as described in the Applications Information section.

#### **Output Overvoltage Protection**

An overvoltage comparator, OV, guards against transient overshoots (>7.5%) as well as other more serious conditions that may overvoltage the output. In this case, the top MOSFET is turned off and the bottom MOSFET is turned on until the overvoltage condition is cleared.

#### Power Good (PGOOD) Pin

The PGOOD pin is connected to an open drain of an internal MOSFET. The MOSFET turns on and pulls the pin low when either output is not within  $\pm 7.5\%$  of the nominal output level as determined by the resistive feedback divider. When both outputs meet the  $\pm 7.5\%$  requirement, the MOSFET is turned off within  $10\mu s$  and the pin is allowed to be pulled up by an external resistor to a source of up to 7V.

## Foldback Current, Short-Circuit Detection and Short-Circuit Latchoff

The RUN/SS capacitors are used initially to limit the inrush current of each switching regulator. After the controller has been started and been given adequate time to charge up the output capacitors and provide full load current, the RUN/SS capacitor is used in a short-circuit time-out circuit. If the output voltage falls to less than 70% of its nominal output voltage, the RUN/SS capacitor begins discharging on the assumption that the output is in an overcurrent and/or short-circuit condition. If the condition lasts for a long enough period as determined by the size of the RUN/SS capacitor, the controller will be shut down until the RUN/SS pin(s) voltage(s) are recycled. This built-in latchoff can be overridden by providing a >5µA pull-up at a compliance of 5V to the RUN/SS pin(s).

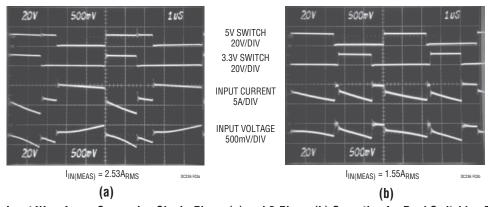

Figure 3. Input Waveforms Comparing Single-Phase (a) and 2-Phase (b) Operation for Dual Switching Regulators Converting 12V to 5V and 3.3V at 3A Each. The Reduced Input Ripple with the LTC1628 2-Phase Regulator Allows Less Expensive Input Capacitors, Reduces Shielding Requirements for EMI and Improves Efficiency

This current shortens the soft start period but also prevents net discharge of the RUN/SS capacitor(s) during an overcurrent and/or short-circuit condition. Foldback current limiting is also activated when the output voltage falls below 70% of its nominal level whether or not the short-circuit latchoff circuit is enabled. Even if a short is present and the short-circuit latchoff is not enabled, a safe, low output current is provided due to internal current foldback and actual power wasted is low due to the efficient nature of the current mode switching regulator.

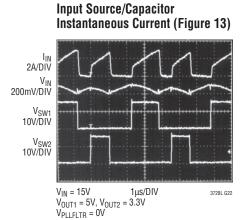

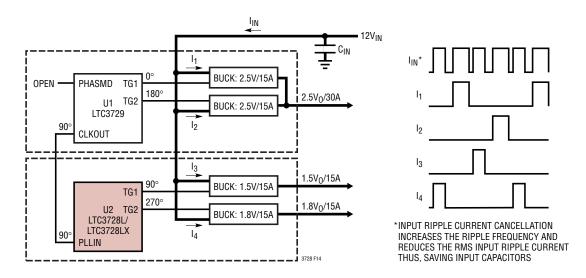

#### THEORY AND BENEFITS OF 2-PHASE OPERATION

The LTC1628 and the LTC3728L family of dual high efficiency DC/DC controllers brings the considerable benefits of 2-phase operation to portable applications for the first time. Notebook computers, PDAs, handheld terminals and automotive electronics will all benefit from the lower input filtering requirement, reduced electromagnetic interference (EMI) and increased efficiency associated with 2-phase operation.

Why the need for 2-phase operation? Up until the 2-phase family, constant-frequency dual switching regulators operated both channels in phase (i.e., single-phase operation). This means that both switches turned on at the same time, causing current pulses of up to twice the amplitude of those for one regulator to be drawn from the input capacitor and battery. These large amplitude current pulses

increased the total RMS current flowing from the input capacitor, requiring the use of more expensive input capacitors and increasing both EMI and losses in the input capacitor and battery.

With 2-phase operation, the two channels of the dual-switching regulator are operated 180 degrees out of phase. This\_effectively\_interleaves the current pulses drawn by the switches, greatly reducing the overlap time where they add together. The result is a significant reduction in total RMS input current, which in turn allows less expensive input capacitors to be used, reduces shielding requirements for EMI and improves real world operating efficiency.

Figure 3 compares the input waveforms for a representative single-phase dual switching regulator to the LTC1628 2-phase dual switching regulator. An actual measurement of the RMS input current under these conditions shows that 2-phase operation dropped the input current from  $2.53A_{RMS}$  to  $1.55A_{RMS}$ . While this is an impressive reduction in itself, remember that the power losses are proportional to  $I_{RMS}^2$ , meaning that the actual power wasted is reduced by a factor of 2.66. The reduced input ripple voltage also means less power is lost in the input power path, which could include batteries, switches, trace/connector resistances and protection circuitry. Improvements in both conducted and radiated EMI also directly accrue as a result of the reduced RMS input current and voltage.

LINEAD TECHNOLOGY

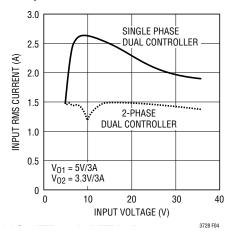

Of course, the improvement afforded by 2-phase operation is a function of the dual switching regulator's relative duty cycles which, in turn, are dependent upon the input voltage  $V_{IN}$  (Duty Cycle =  $V_{OUT}/V_{IN}$ ). Figure 4 shows how the RMS input current varies for single-phase and 2-phase operation for 3.3V and 5V regulators over a wide input voltage range.

It can readily be seen that the advantages of 2-phase operation are not just limited to a narrow operating range, but in fact extend over a wide region. A good rule of thumb for most applications is that 2-phase operation will reduce the input capacitor requirement to that for just one channel operating at maximum current and 50% duty cycle.

A final question: If 2-phase operation offers such an advantage over single-phase operation for dual switching regulators, why hasn't it been done before? The answer is that, while simple in concept, it is hard to implement. Constant-frequency current mode switching regulators require an oscillator derived "slope compensation" signal to allow stable operation of each regulator at over 50% duty cycle. This signal is relatively easy to derive in single-phase dual switching regulators, but required the develop-

ment of a new and proprietary technique to allow 2-phase operation. In addition, isolation between the two channels becomes more critical with 2-phase operation because switch transitions in one channel could potentially disrupt the operation of the other channel.

These 2-phase parts are proof that these hurdles have been surmounted. They offer unique advantages for the ever-expanding number of high efficiency power supplies required in portable electronics.

Figure 4. RMS Input Current Comparison

Figure 1 on the first page is a basic LTC3728L/LTC3728LX application circuit. External component selection is driven by the load requirement, and begins with the selection of  $R_{\text{SENSE}}$  and the inductor value. Next, the power MOSFETs and D1 are selected. Finally,  $C_{\text{IN}}$  and  $C_{\text{OUT}}$  are selected. The circuit shown in Figure 1 can be configured for operation up to an input voltage of 28V (limited by the external MOSFETs).

#### **RSENSE Selection For Output Current**

R<sub>SENSE</sub> is chosen based on the required output current. The current comparator has a maximum threshold of 75mV/R<sub>SENSE</sub> and an input common mode range of SGND to 1.1(INTV<sub>CC</sub>). The current comparator threshold sets the peak of the inductor current, yielding a maximum average output current  $I_{MAX}$  equal to the peak value less half the peak-to-peak ripple current,  $\Delta I_L$ .

Allowing a margin for variations in the IC and external component values yields:

$$R_{SENSE} = \frac{50mV}{I_{MAX}}$$

Because of possible PCB layout-induced noise in the current sensing loop, the AC current sensing ripple of  $\Delta V_{SENSE} = \Delta I \bullet R_{SENSE}$  also needs to be checked in the design to get good signal-to-noise ratio. In general, for a reasonably good PCB layout, a 15mV  $\Delta V_{SENSE}$  voltage is recommended as a conservative design starting point. When using the controller in very low dropout conditions, the maximum output current level will be reduced due to the internal compensation required to meet stability criterion for buck regulators operating at greater than 50% duty factor. A curve is provided to estimate this reduction in peak output current level depending upon the operating duty factor.

#### **Operating Frequency**

The IC uses a constant frequency phase-lockable architecture with the frequency determined by an internal capacitor. This capacitor is charged by a fixed current plus an additional current which is proportional to the voltage applied to the PLLFLTR pin. Refer to Phase-Locked Loop

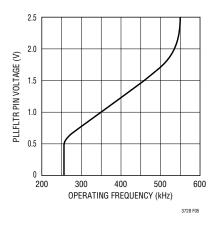

Figure 5. PLLFLTR Pin Voltage vs Frequency

and Frequency Synchronization in the Applications Information section for additional information.

A graph for the voltage applied to the PLLFLTR pin vs frequency is given in Figure 5. As the operating frequency is increased the gate charge losses will be higher, reducing efficiency (see Efficiency Considerations). The maximum switching frequency is approximately 550kHz.

#### -Inductor-Value Calculation

The operating frequency and inductor selection are interrelated in that higher operating frequencies allow the use of smaller inductor and capacitor values. So why would anyone ever choose to operate at lower frequencies with larger components? The answer is efficiency. A higher frequency generally results in lower efficiency because of MOSFET gate charge losses. In addition to this basic trade-off, the effect of inductor value on ripple current and low current operation must also be considered.

The inductor value has a direct effect on ripple current. The inductor ripple current  $\Delta I_L$  decreases with higher inductance or frequency and increases with higher  $V_{IN}$ :

$$\Delta I_{L} = \frac{1}{(f)(L)} V_{OUT} \left( 1 - \frac{V_{OUT}}{V_{IN}} \right)$$

Accepting larger values of  $\Delta I_L$  allows the use of low inductances, but results in higher output voltage ripple and greater core losses. A reasonable starting point for setting ripple current is  $\Delta I = 30\%$  of maximum output current or higher for good load transient response and sufficient ripple current signal in the current loop.

The inductor value also has secondary effects. The transition to Burst Mode operation begins when the average inductor current required results in a peak current below 25% of the current limit determined by  $R_{SENSE}$ . Lower inductor values (higher  $\Delta l_L$ ) will cause this to occur at lower load currents, which can cause a dip in efficiency in the upper range of low current operation. In Burst Mode operation, lower inductance values will cause the burst frequency to decrease.

#### **Inductor Core Selection**

Once the value for L is known, the type of inductor must be selected. High efficiency converters generally cannot afford the core loss found in low cost powdered iron cores, forcing the use of more expensive ferrite, molypermalloy, or Kool  $M\mu^{\tiny{\textcircled{@}}}$  cores. Actual core loss is independent of core size for a fixed inductor value, but it is very dependent on inductance selected. As inductance increases, core losses go down. Unfortunately, increased inductance requires more turns of wire and therefore copper losses will increase.

Ferrite designs have very low core loss and are preferred at high switching frequencies, so design goals can concentrate on copper loss and preventing saturation. Ferrite core material saturates "hard," which means that inductance collapses abruptly when the peak design current is exceeded. This results in an abrupt increase in inductor ripple current and consequent output voltage ripple. Do not allow the core to saturate!

Molypermalloy (from Magnetics, Inc.) is a very good, low loss core material for toroids, but it is more expensive than ferrite. A reasonable compromise from the same manufacturer is Kool M $\mu$ . Toroids are very space efficient, especially when you can use several layers of wire. Because they generally lack a bobbin, mounting is more difficult. However, designs for surface mount are available that do not increase the height significantly.

#### **Power MOSFET and D1 Selection**

Two external power MOSFETs must be selected for each controller in the LTC3728L/LTC3728LX: One N-channel MOSFET for the top (main) switch, and one N-channel MOSFET for the bottom (synchronous) switch.

The peak-to-peak drive levels are set by the INTV<sub>CC</sub> voltage. This voltage is typically 5V during start-up (see EXTV<sub>CC</sub> Pin Connection). Consequently, logic-level threshold MOSFETs must be used in most applications. The only exception is if low input voltage is expected (V<sub>IN</sub> < 5V); then, sub-logic level threshold MOSFETs (V<sub>GS(TH)</sub> < 3V) should be used. Pay close attention to the BV<sub>DSS</sub> specification for the MOSFETs as well; most of the logic level MOSFETs are limited to 30V or less.

Selection criteria for the power MOSFETs include the "ON" resistance  $R_{DS(ON)}$ , Miller capacitance  $C_{MILLER}$ , input voltage and maximum output current. Miller capacitance,  $C_{MILLER}$ , can be approximated from the gate charge curve usually provided on the MOSFET manufacturers' data sheet.  $C_{MILLER}$  is equal to the increase in gate charge along the horizontal axis while the curve is approximately flat divided by the specified change in  $V_{DS}$ . This result is then multiplied by the ratio of the application applied  $V_{DS}$  to the Gate charge curve specified  $V_{DS}$ . When the IC is operating in continuous mode the duty cycles for the top and bottom MOSFETs are given by:

$$Main Switch Duty Cycle = \frac{V_{OUT}}{V_{IN}}$$

Synchronous Switch Duty Cycle =

$$\frac{V_{IN} - V_{OUT}}{V_{IN}}$$

The MOSFET power dissipations at maximum output current are given by:

$$\begin{split} P_{MAIN} &= \frac{V_{OUT}}{V_{IN}} \Big(I_{MAX}\Big)^2 \Big(1 + \delta\Big) R_{DS(ON)} + \\ & \Big(V_{IN}\Big)^2 \bigg(\frac{I_{MAX}}{2}\bigg) \Big(R_{DR}\Big) \Big(C_{MILLER}\Big) \bullet \\ & \left[\frac{1}{V_{INTVCC} - V_{THMIN}} + \frac{1}{V_{THMIN}}\right] \Big(f\Big) \end{split}$$

$$P_{SYNC} = \frac{V_{IN} - V_{OUT}}{V_{IN}} \Big(I_{MAX}\Big)^2 \Big(1 + \delta\Big) R_{DS(ON)}$$

where  $\delta$  is the temperature dependency of  $R_{DS(0N)}$  and  $R_{DR}$  (approximately  $4\Omega)$  is the effective driver resistance at the MOSFET's Miller threshold voltage.  $V_{THMIN}$  is the typical MOSFET minimum threshold voltage.

Both MOSFETs have I $^2$ R losses while the topside N-channel equation includes an additional term for transition losses, which are highest at high input voltages. For V $_{IN}$  < 20V the high current efficiency generally improves with larger MOSFETs, while for V $_{IN}$  > 20V the transition losses rapidly increase to the point that the use of a higher R $_{DS(ON)}$  device with lower C $_{MILLER}$  actually provides higher efficiency. The synchronous MOSFET losses are greatest at high input voltage when the top switch duty factor is low or during a short-circuit when the synchronous switch is on close to 100% of the period.

The term  $(1+\delta)$  is generally given for a MOSFET in the form of a normalized  $R_{DS(ON)}$  vs Temperature curve, but  $\delta$  = 0.005/°C can be used as an approximation for low voltage MOSFETs.

The Schottky diode D1 shown in Figure 1 conducts during the dead-time between the conduction of the two power MOSFETs. This prevents the body diode of the bottom MOSFET from turning on, storing charge during the dead-time and requiring a reverse recovery period that could cost as much as 3% in efficiency at high  $V_{IN}$ . A 1A to 3A Schottky is generally a good compromise for both regions of operation due to the relatively small average current. Larger diodes result in additional transition losses due to their larger junction capacitance.

#### CIN and COLIT Selection

The selection of  $C_{\text{IN}}$  is simplified by the multiphase architecture and its impact on the worst-case RMS current drawn through the input network (battery/fuse/capacitor). It can be shown that the worst case RMS current occurs when only one controller is operating. The controller with the highest ( $V_{\text{OUT}}$ )( $I_{\text{OUT}}$ ) product needs to be used in the formula below to determine the maximum RMS current requirement. Increasing the output current, drawn from the other out-of-phase controller, will actually decrease the input RMS ripple current from this maximum value (see Figure 4). The out-of-phase technique typically reduces the input capacitor's RMS ripple current by a factor

of 30% to 70% when compared to a single phase power supply solution.

The type of input capacitor, value and ESR rating have efficiency effects that need to be considered in the selection process. The capacitance value chosen should be sufficient to store adequate charge to keep high peak battery currents down.  $20\mu F$  to  $40\mu F$  is usually sufficient for a 25W output supply operating at 200kHz. The ESR of the capacitor is important for capacitor power dissipation as well as overall battery efficiency. All of the power (RMS ripple current • ESR) not only heats up the capacitor but wastes power from the battery.

Medium voltage (20V to 35V) ceramic, tantalum, OS-CON and switcher-rated electrolytic capacitors can be used as input capacitors, but each has drawbacks: ceramic voltage coefficients are very high and may have audible piezoelectric effects; tantalums need to be surge-rated; OS-CONs suffer from higher inductance, larger case size and limited surface-mount applicability; electrolytics' higher ESR and dryout possibility require several to be used. Multiphase systems allow the lowest amount of capacitance overall. As little as one 22µF or two to three 10µF ceramic capacitors are an ideal choice in a 20W to 35W power supply due to their extremely low ESR. Even though the capacitance at 20V is substantially below their rating at zero-bias, very low ESR loss makes ceramics an ideal candidate for highest efficiency battery operated systems. Also consider parallel ceramic and high quality electrolytic capacitors as an effective means of achieving ESR and bulk capacitance goals.

In continuous mode, the source current of the top N-channel MOSFET is a square wave of duty cycle  $V_{OUT}/V_{IN}$ . To prevent large voltage transients, a low ESR input capacitor sized for the maximum RMS current of one channel must be used. The maximum RMS capacitor current is given by:

$$C_{IN}$$

Required  $I_{RMS} \approx I_{MAX} \frac{\left[V_{OUT}(V_{IN} - V_{OUT})\right]^{1/2}}{V_{IN}}$

This formula has a maximum at  $V_{IN} = 2V_{OUT}$ , where  $I_{RMS} = I_{OUT}/2$ . This simple worst case condition is commonly used for design because even significant deviations do not offer much relief. Note that capacitor manufacturer's

**Y LINEAR**

ripple current ratings are often based on only 2000 hours of life. This makes it advisable to further derate the capacitor, or to choose a capacitor rated at a higher temperature than required. Several capacitors may also be paralleled to meet size or height requirements in the design. Always consult the manufacturer if there is any question.

The benefit of the LTC3728L/LTC3728LX multiphase clocking can be calculated by using the equation above for the higher power controller and then calculating the loss that would have resulted if both controller channels switched on at the same time. The total RMS power lost is lower when both controllers are operating due to the interleaving of current pulses through the input capacitor's ESR. This is why the input capacitor's requirement calculated above for the worst-case controller is adequate for the dual controller design. Remember that input protection fuse resistance, battery resistance and PC board trace resistance losses are also reduced due to the reduced peak currents in a multiphase system. The overall benefit of a multiphase design will only be fully realized when the source impedance of the power supply/battery is included in the efficiency testing. The drains of the two top MOSFETS should be placed within 1cm of each other and share a common C<sub>IN</sub>(s). Separating the drains and C<sub>IN</sub> may produce undesirable voltage and current resonances at V<sub>IN</sub>.

The selection of  $C_{OUT}$  is driven by the required effective series resistance (ESR). Typically once the ESR requirement is satisfied the capacitance is adequate for filtering. The output ripple ( $\Delta V_{OUT}$ ) is determined by:

$$\Delta V_{OUT} \approx \Delta I_L \Biggl( ESR + \frac{1}{8fC_{OUT}} \Biggr)$$

Where f = operating frequency,  $C_{OUT}$  = output capacitance, and  $\Delta I_L$  = ripple current in the inductor. The output ripple is highest at maximum input voltage since  $\Delta I_L$  increases with input voltage. With  $\Delta I_L$  =  $0.3I_{OUT(MAX)}$  the output ripple will typically be less than 50mV at the maximum  $V_{IN}$  assuming:

$C_{OUT}$  Recommended ESR < 2 R<sub>SENSE</sub> and  $C_{OUT}$  > 1/(8fR<sub>SENSE</sub>)

The first condition relates to the ripple current into the ESR of the output capacitance while the second term guarantees that the output capacitance does not significantly discharge during the operating frequency period due to ripple current. The choice of using smaller output capacitance increases the ripple voltage due to the discharging term but can be compensated for by using capacitors of very low ESR to maintain the ripple voltage at or below 50mV. The  $I_{TH}$  pin OPTI-LOOP compensation components can be optimized to provide stable, high performance transient response regardless of the output capacitors selected.

Manufacturers such as Nichicon, United Chemi-Con and Sanyo can be considered for high performance throughhole capacitors. The OS-CON semiconductor dielectric capacitor available from Sanyo has the lowest (ESR)(size) product of any aluminum electrolytic at a somewhat higher price. An additional ceramic capacitor in parallel with OS-CON capacitors is recommended to reduce the inductance effects.

In surface mount applications multiple capacitors may need to be used in parallel to meet ESR, RMS current handling and load step requirements. Aluminum electrolytic, dry tantalum and special polymer capacitors are available in surface mount packages. Special polymer surface mount capacitors offer very low ESR but have lower storage capacity per unit volume than other capacitor types. These capacitors offer a very cost-effective output capacitor solution and are an ideal choice when combined with a controller having high loop bandwidth. Tantalum capacitors offer the highest capacitance density and are often used as output capacitors for switching regulators having controlled soft-start. Several excellent surge-tested choices are the AVX TPS, AVX TPSV or the KEMET T510 series of surface mount tantalums, available in case heights ranging from 2mm to 4mm. Aluminum electrolytic capacitors can be used in cost-driven applications providing that consideration is given to ripple current ratings, temperature and long term reliability. A typical application will require several to many aluminum electrolytic capacitors in parallel. A combination of the above mentioned capacitors will often result in maximizing performance and minimizing overall cost. Other capacitor types include Nichicon PL series, Panasonic SP,

NEC Neocap, Cornell Dubilier ESRE and Sprague 595D series. Consult manufacturers for other specific recommendations.

#### INTV<sub>CC</sub> Regulator

An internal P-channel low dropout regulator produces 5V at the INTV $_{CC}$  pin from the V $_{IN}$  supply pin. INTV $_{CC}$  powers the drivers and internal circuitry within the IC. The INTV $_{CC}$  pin regulator can supply a peak current of 50mA and must be bypassed to ground with a minimum of 4.7 $\mu$ F tantalum, 10 $\mu$ F special polymer, or low ESR type electrolytic capacitor. A 1 $\mu$ F ceramic capacitor placed directly adjacent to the INTV $_{CC}$  and PGND IC pins is highly recommended. Good bypassing is necessary to supply the high transient currents required by the MOSFET gate drivers and to prevent interaction between channels.

Higher input voltage applications in which large MOSFETs are being driven at high frequencies may cause the maximum junction temperature rating for the IC to be exceeded. The system supply current is normally dominated by the gate charge current. Additional external loading of the INTV<sub>CC</sub> and 3.3V linear regulators also needs to be taken into account for the power dissipation calculations. The total INTV<sub>CC</sub> current can be supplied by either the 5V internal linear regulator or by the EXTV<sub>CC</sub> input pin. When the voltage applied to the EXTV<sub>CC</sub> pin is less than 4.7V, all of the  $INTV_{CC}$  current is supplied by the internal 5V linear regulator. Power dissipation for the IC in this case is highest:  $(V_{IN})(I_{INTVCC})$ , and overall efficiency is lowered. The gate charge current is dependent on operating frequency as discussed in the Efficiency Considerations section. The junction temperature can be estimated by using the equations given in Note 2 of the Electrical Characteristics. For example, the IC  $V_{\mbox{\scriptsize IN}}$  current is thermally limited to less than 67mA from a 24V supply when not using the EXTV<sub>CC</sub> pin as follows:

$$T_J = 70^{\circ}C + (67\text{mA})(24\text{V})(34^{\circ}C/\text{W}) = 125^{\circ}C$$

Use of the  $\mathsf{EXTV}_\mathsf{CC}$  input pin reduces the junction temperature to:

$$T_J = 70^{\circ}C + (67\text{mA})(5\text{V})(34^{\circ}C/\text{W}) = 81^{\circ}C$$

The absolute maximum rating for the INTV  $_{\mbox{\footnotesize CC}}$  Pin is 40mA. Dissipation should be calculated to also include any added

current drawn from the internal 3.3V linear regulator. To prevent maximum junction temperature from being exceeded, the input supply current must be checked operating in continuous mode at maximum  $V_{\text{IN}}$ .

#### **EXTV<sub>CC</sub> Connection**

The IC contains an internal P-channel MOSFET switch connected between the EXTV $_{CC}$  and INTV $_{CC}$  pins. When the voltage applied to EXTV $_{CC}$  rises above 4.7V, the internal regulator is turned off and the switch closes, connecting the EXTV $_{CC}$  pin to the INTV $_{CC}$  pin thereby supplying internal power. The switch remains closed as long as the voltage applied to EXTV $_{CC}$  remains above 4.5V. This allows the MOSFET driver and control power to be derived from the output during normal operation (4.7V < V $_{OUT}$  < 7V) and from the internal regulator when the output is out of regulation (start-up, short-circuit). If more current is required through the EXTV $_{CC}$  switch than is specified, an external Schottky diode can be added between the EXTV $_{CC}$  and INTV $_{CC}$  pins. Do not apply greater than 7V to the EXTV $_{CC}$  pin and ensure that EXTV $_{CC} \le V_{IN}$ .

Significant efficiency gains can be realized by powering INTV $_{CC}$  from the output, since the  $V_{IN}$  current resulting from the driver and control currents will be scaled by a factor of (Duty Cycle)/(Efficiency). For 5V regulators this supply means connecting the EXTV $_{CC}$  pin directly to  $V_{OUT}$ . However, for 3.3V and other lower voltage regulators, additional circuitry is required to derive INTV $_{CC}$  power from the output.

The following list summarizes the four possible connections for  $\mathsf{EXTV}_{\mathsf{CC}}$ :

- 1. EXTV<sub>CC</sub> Left Open (or Grounded). This will cause INTV<sub>CC</sub> to be powered from the internal 5V regulator resulting in an efficiency penalty of up to 10% at high input voltages.

- 2. EXTV $_{\rm CC}$  Connected directly to V $_{\rm OUT}$ . This is the normal connection for a 5V regulator and provides the highest efficiency.

- 3. EXTV<sub>CC</sub> Connected to an External supply. If an external supply is available in the 5V to 7V range, it may be used to power EXTV<sub>CC</sub> providing it is compatible with the MOSFET gate drive requirements.

LINEAR

4. EXTV $_{\rm CC}$  Connected to an Output-Derived Boost Network. For 3.3V and other low voltage regulators, efficiency gains can still be realized by connecting EXTV $_{\rm CC}$  to an output-derived voltage that has been boosted to greater than 4.7V. This can be done with either the inductive boost winding as shown in Figure 6a or the capacitive charge pump shown in Figure 6b. The charge pump has the advantage of simple magnetics.

#### Topside MOSFET Driver Supply $(C_B, D_B)$

External bootstrap capacitors C<sub>B</sub> connected to the BOOST pins supply the gate drive voltages for the topside MOSFETs. Capacitor C<sub>B</sub> in the functional diagram is charged though external diode D<sub>B</sub> from INTV<sub>CC</sub> when the SW pin is low. When one of the topside MOSFETs is to be turned on, the driver places the C<sub>B</sub> voltage across the gate-source of the desired MOSFET. This enhances the MOSFET and turns on the topside switch. The switch node voltage, SW, rises to V<sub>IN</sub> and the BOOST pin follows. With the topside MOSFET on, the boost voltage is above the input supply:  $V_{BOOST}$  =  $V_{INI} + V_{INTVCC}$ . The value of the boost capacitor  $C_B$  needs to be 100 times that of the total input capacitance of the topside MOSFET(s). The reverse breakdown of the external Schottky diode must be greater than  $V_{IN(MAX)}$ . When adjusting the gate drive level, the final arbiter is the total input current for the regulator. If a change is made and the input current decreases, then the efficiency has improved. If there is no change in input current, then there is no change in efficiency.

Figure 6a. Secondary Output Loop & EXTV<sub>CC</sub> Connection

#### **Output Voltage**

The output voltages are each set by an external feedback resistive divider carefully placed across the output capacitor. The resultant feedback signal is compared with the internal precision 0.800V voltage reference by the error amplifier. The output voltage is given by the equation:

$$V_{OUT} = 0.8V \left(1 + \frac{R2}{R1}\right)$$

where R1 and R2 are defined in Figure 2.

#### SENSE+/SENSE- Pins

The common mode input range of the current comparator sense pins is from 0V to (1.1)INTV $_{CC}$ . Continuous linear operation is guaranteed throughout this range allowing output voltage setting from 0.8V to 7.7V, depending upon the voltage applied to EXTV $_{CC}$ . A differential NPN input stage is biased with internal resistors from an internal 2.4V source as shown in the Functional Diagram. This requires that current either be sourced or sunk from the SENSE pins depending on the output voltage. If the output voltage is below 2.4V current will flow out of both SENSE pins to the main output. The output can be easily preloaded by the  $V_{OUT}$  resistive divider to compensate for the current comparator's negative input bias current. The maximum current flowing out of each pair of SENSE pins is:

$$I_{SENSE}^{+} + I_{SENSE}^{-} = (2.4V - V_{OUT})/24k$$

Figure 6b. Capacitive Charge Pump for EXTV<sub>CC</sub>

Since  $V_{OSENSE}$  is servoed to the 0.8V reference voltage, we can choose R1 in Figure 2 to have a maximum value to absorb this current.

R1<sub>(MAX)</sub> =

$$24k \left( \frac{0.8V}{2.4V - V_{OUT}} \right)$$

Regulating an output voltage of 1.8V, the maximum value of R1 should be 32k. Note that for an output voltage above 2.4V, R1 has no maximum value necessary to absorb the sense currents; however, R1 is still bounded by the  $V_{OSENSE}$  feedback current.

#### **Soft-Start/Run Function**

The RUN/SS1 and RUN/SS2 pins are multipurpose pins that provide a soft-start function and a means to shut down the LTC3728L/LTC3728LX. Soft-start reduces the input power source's surge currents by gradually increasing the controller's current limit (proportional to  $V_{\rm ITH}$ ). This pin can also be used for power supply sequencing.

An internal 1.2 $\mu$ A current source charges up the C<sub>SS</sub> capacitor. When the voltage on RUN/SS1 (RUN/SS2) reaches 1.5V, the particular controller is permitted to start operating. As the voltage on RUN/SS increases from 1.5V to 3.0V, the internal current limit is increased from 25mV/R<sub>SENSE</sub> to 75mV/R<sub>SENSE</sub>. The output current limit ramps up slowly, taking an additional 1.25s/ $\mu$ F to reach full current. The output current thus ramps up slowly, reducing the starting surge current required from the input power supply. If RUN/SS has been pulled all the way to ground there is a delay before starting of approximately:

$$t_{DELAY} = \frac{1.5V}{1.2\mu A} C_{SS} = (1.25s/\mu F) C_{SS}$$

$$t_{IRAMP} = \frac{3V - 1.5V}{1.2\mu A} C_{SS} = (1.25s/\mu F) C_{SS}$$

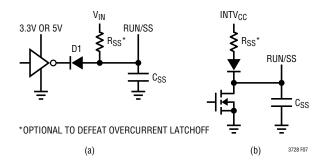

By pulling both RUN/SS pins below 1V, the IC is put into low current shutdown ( $I_Q = 20\mu A$ ). The RUN/SS pins can be driven directly from logic as shown in Figure 7. Diode D1 in Figure 7 reduces the start delay but allows  $C_{SS}$  to

Figure 7. RUN/SS Pin Interfacing

ramp up slowly providing the soft-start function. Each RUN/SS pin has an internal 6V zener clamp (See Functional Diagram).

#### **Fault Conditions: Overcurrent Latchoff**

The RUN/SS pins also provide the ability to latch off the controller(s) when an overcurrent condition is detected. The RUN/SS capacitor,  $C_{SS}$ , is used initially to turn on and limit the inrush current. After the controller has been started and been given adequate time to charge up the output capacitor and provide full load current, the RUN/SS capacitor is used for a short-circuit timer. If the regulator's output voltage falls to less than 70% of its nominal value after  $C_{SS}$  reaches 4.1V,  $C_{SS}$  begins discharging on the assumption that the output is in an overcurrent condition. If the condition lasts for a long enough period as determined by the size of the  $C_{SS}$  and the specified discharge current, the controller will be shut down until the RUN/SS pin voltage is recycled. If the overload occurs during startup, the time can be approximated by:

$$t_{L01} \approx [C_{SS}(4.1 - 1.5 + 4.1 - 3.5)]/(1.2\mu\text{A})$$

= 2.7 • 10<sup>6</sup> (C<sub>SS</sub>)

If the overload occurs after start-up the voltage on  $C_{SS}$  will begin discharging from the zener clamp voltage:

$$t_{LO2} \approx [C_{SS} (6 - 3.5)]/(1.2 \mu A) = 2.1 \cdot 10^6 (C_{SS})$$

This built-in overcurrent latchoff can be overridden by providing a pull-up resistor to the RUN/SS pin as shown in Figure 7. This resistance shortens the soft-start period and prevents the discharge of the RUN/SS capacitor during an over current condition. Tying this pull-up resistor to  $V_{\rm IN}$ , as in Figure 7a, defeats overcurrent latchoff.

Diode-connecting this pull-up resistor to INTV $_{CC}$ , as in Figure 7b, eliminates any extra supply current during controller shutdown while eliminating the INTV $_{CC}$  loading from preventing controller start-up.

Why should you defeat overcurrent latchoff? During the prototyping stage of a design, there may be a problem with noise pickup or poor layout causing the protection circuit to latch off. Defeating this feature will easily allow troubleshooting of the circuit and PC layout. The internal short-circuit and foldback current limiting still remains active, thereby protecting the power supply system from failure. After the design is complete, a decision can be made whether to enable the latchoff feature.

The value of the soft-start capacitor  $C_{SS}$  may need to be scaled with output voltage, output capacitance and load current characteristics. The minimum soft-start capacitance is given by:

$$C_{SS} > (C_{OUT})(V_{OUT}) (10^{-4}) (R_{SENSE})$$

The minimum recommended soft-start capacitor of  $C_{SS} = 0.1 \mu F$  will be sufficient for most applications.

#### Fault Conditions: Current Limit and Current Foldback

The current comparators have a maximum sense voltage of 75mV resulting in a maximum MOSFET current of 75mV/R<sub>SENSE</sub>. The maximum value of current limit generally occurs with the largest  $V_{IN}$  at the highest ambient temperature, conditions that cause the highest power dissipation in the top MOSFET.

Each controller includes current foldback to help further limit load current when the output is shorted to ground. The foldback circuit is active even when the overload shutdown latch described above is overridden. If the output falls below 70% of its nominal output level, then the maximum sense voltage is progressively lowered from 75mV to 25mV. Under short-circuit conditions with very low duty cycles, the controller will begin cycle skipping in order to limit the short-circuit current. In this situation the bottom MOSFET will be dissipating most of the power but less than in normal operation. The short-circuit ripple current is determined by the minimum on-time ton(MIN) of each controller (typically 100ns), the input voltage and inductor value:

$$\Delta I_{L(SC)} = t_{ON(MIN)} (V_{IN}/L)$$

The resulting short-circuit current is:

$$I_{SC} = \frac{25mV}{R_{SENSE}} - \frac{1}{2}\Delta I_{L(SC)}$$

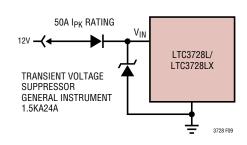

#### Fault Conditions: Overvoltage Protection (Crowbar)

The overvoltage crowbar is designed to blow a system input fuse when the output voltage of the regulator rises much higher than nominal levels. The crowbar causes huge currents to flow, that blow the fuse to protect against a shorted top MOSFET if the short occurs while the controller is operating.

A comparator monitors the output for overvoltage conditions. The comparator (OV) detects overvoltage faults greater than 7.5% above the nominal output voltage. When this condition is sensed, the top MOSFET is turned off and the bottom MOSFET is turned on until the overvoltage condition is cleared. The output of this comparator is only latched by the overvoltage condition itself and will therefore allow a switching regulator system having a poor PC layout to function while the design is being debugged. The bottom MOSFET remains on continuously for as long as the OV condition persists; if  $V_{OUT}$  returns to a safe level, normal operation automatically resumes. A shorted top MOSFET will result in a high current condition which will open the system fuse. The switching regulator will regulate properly with a leaky top MOSFET by altering the duty cycle to accommodate the leakage.

#### **Phase-Locked Loop and Frequency Synchronization**

The IC has a phase-locked loop comprised of an internal voltage controlled oscillator and phase detector. This allows the top MOSFET turn-on to be locked to the rising edge of an external source. The frequency range of the voltage controlled oscillator is  $\pm 50\%$  around the center frequency  $f_0$ . A voltage applied to the PLLFLTR pin of 1.2V corresponds to a frequency of approximately 400kHz. The nominal operating frequency range of the IC is 260kHz to 550kHz.

The phase detector used is an edge sensitive digital type which provides zero degrees phase shift between the external and internal oscillators. This type of phase detector will not lock up on input frequencies close to the harmonics of the VCO center frequency. The PLL hold-in range,  $\Delta f_{H}$ , is equal to the capture range,  $\Delta f_{C}$ :

$$\Delta f_H = \Delta f_C = \pm 0.5 f_O (260 \text{kHz} - 550 \text{kHz})$$

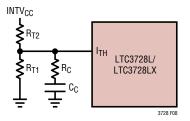

The output of the phase detector is a complementary pair of current sources charging or discharging the external filter network on the PLLFLTR pin. A simplified block diagram is shown in Figure 7.

If the external frequency (f<sub>PLLIN</sub>) is greater than the oscillator frequency f<sub>OSC</sub>, current is sourced continuously, pulling up the PLLFLTR pin. When the external frequency is less than f<sub>OSC</sub>, current is sunk continuously, pulling down the PLLFLTR pin. If the external and internal frequencies are the same but exhibit a phase difference, the current sources turn on for an amount of time corresponding to the phase difference. Thus the voltage on the PLLFLTR pin is adjusted until the phase and frequency of the external and internal oscillators are identical. At this stable operating point the phase comparator output is open and the filter capacitor  $C_{IP}$  holds the voltage. The IC's PLLIN pin must be driven from a low impedance source such as a logic gate located close to the pin. When using multiple ICs for a phase-locked system, the PLLFLTR pin of the master oscillator should be biased at a voltage that will guarantee the slave oscillator(s) ability to lock onto the master's frequency. A DC voltage of 0.7V to 1.7V applied to the master oscillator's PLLFLTR pin is recommended in order to meet this requirement. The resultant operating frequency can range from 300kHz to 500kHz.