### Virtex-6 FPGA CX75T, CX130T, CX195T, and CX240T Production Errata

EN149 (v1.2) January 17, 2011

**Errata Notification**

## Introduction

Thank you for designing with the Xilinx Virtex®-6 family of devices. Although Xilinx has made every effort to ensure the highest possible quality, the devices listed in Table 1 are subject to the limitations described in the following errata.

# **Devices**

These errata apply to the devices shown in Table 1.

#### Table 1: Devices Affected by These Errata

| Devices      | XC6VCX75T  | JTAG ID (Revision Code): 2 |

|--------------|------------|----------------------------|

|              | XC6VCX130T | JTAG ID (Revision Code): 2 |

|              | XC6VCX195T | JTAG ID (Revision Code): 2 |

|              | XC6VCX240T | JTAG ID (Revision Code): 2 |

| Packages     | All        |                            |

| Speed Grades | All        |                            |

## Hardware Errata Details

This section provides a detailed description of each hardware issue known at the release time of this document.

### ММСМ

### Restriction of Frequency Range for Bandwidth = HIGH or OPTIMIZED

When the Phase Frequency Detector (PFD) frequency (FIN/D) is lower than 135 MHz and the BANDWIDTH attribute of the MMCM is set to HIGH or OPTIMIZED, a phase error between MMCM output clocks can occur, making the output clock signals invalid. This condition can also cause the fractional output counter to fail.

The ISE® software v12.4 and later provides appropriate warnings for possible violations of this restriction.

The ISE software v12.4 and later correctly handles designs set to OPTIMIZED bandwidth for all valid PFD frequencies.

This issue will not be fixed in the devices listed in Table 1.

#### Work-around

PFD frequencies lower than 135 MHz must use LOW bandwidth mode to ensure correct operation. See <u>Answer Record 38132</u> for more information.

### **Restriction of Clock Divider Values**

The input clock divider (DIVCLK\_DIVIDE) cannot have a value of 3 or 4 when the input clock frequency ( $F_{IN}$ ) of the MMCM is above 315 MHz.

The ISE software v12.4 and later provides appropriate warnings for possible violations of this restriction.

This issue will not be fixed in the devices listed in Table 1.

#### Work-around

In all designs in which F<sub>IN</sub> is above 315 MHz and DIVCLK\_DIVIDE is set to 3 or 4, double the CLKFBOUT\_MULT\_F and DIVCLK\_DIVIDE values. See <u>Answer Record 38133</u> for more information.

© Copyright 2010–2011 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI, PCIe and PCI Express are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

## **Block RAM**

### Dual Port Block RAM Address Overlap in READ\_FIRST and Simple Dual Port Mode

When using the block RAM in True Dual Port (TDP) Read\_First mode, Simple Dual Port (SDP) mode, or ECC mode with different clocks on ports A and B, the user must ensure certain addresses do not occur simultaneously on both ports when both ports are enabled and one port is being written to. Failure to observe this restriction can result in read and/or memory array corruption.

The description is found in the Conflict Avoidance section in v1.3.1 (or later) of UG363, Virtex-6 FPGA Memory Resources User Guide.

This description was originally added in UG363 (v1.1), published 9/16/09. This errata is being provided to highlight this change and ensure that all users are aware of this design restriction. The ISE v12.1 software provides appropriate warnings for possible violations of these restrictions.

This issue will not be fixed in the devices listed in Table 1.

#### Work-around

See Answer Record 34859.

## GTX Transceivers

### GTX Transceiver Initialization for Proper TXOUTCLK Functionality

TXOUTCLK can operate at an incorrect frequency or can remain in a static state when the TXPLL\_DIVSEL\_OUT attribute is set to 2 or 4 and the TXOUTCLK\_CTRL attribute is set to "TXOUTCLKPCS", "TXOUTCLKPMA\_DIV1", or "TXOUTCLKPMA\_DIV2".

An updated reset sequence that ensures proper functionality is documented in version 2.4 of <u>UG366</u>, Virtex-6 *FPGA GTX Transceiver User Guide*. Also see <u>Answer Record 35681</u> for more information.

### **RXRECCLK Static Operating Behavior**

The RXRECCLK output port might operate at reduced frequency in buffer bypass mode if conditions (1) and (2) persist for more than 15,000 cumulative hours at 65°C Tj, 2,500 cumulative hours at 85°C Tj, or 800 cumulative hours at 100°C Tj:

- 1. Power has been applied to V<sub>CCINT</sub>.

- 2. The device is in one of the following states:

- a. The FPGA is not configured

- b. The FPGA is configured, but the transceiver is uninstantiated

- c. The transceiver is instantiated, but no reference clock is toggling

- d. The transceiver is instantiated, but is held in reset or power-down

#### Work-around

#### Transceivers Uninstantiated in User Design but are Planned to be Used in the Future

For transceivers that are not instantiated in the user design but are planned to be used in the future, power must be applied to MGTAVCC, and the user design must be implemented using ISE v12.1 (or later) software for automatic insertion of the work-around circuit.

#### Transceivers Uninstantiated in User Design but are Not Planned to be Used in the Future

Automatic insertion of the work-around circuit can be disabled for uninstantiated transceivers that will not be used.

#### Transceivers Instantiated in User Design

Transceivers instantiated in user design do not require a work-around circuit if the reference clock is toggling and the transceiver is not held in reset or power-down.

See <u>Answer Record 35055</u> for more information.

### GTX Transceiver Delay Aligner

The GTX Transceiver Delay Aligner circuit is used when the TX Buffer and/or RX Elastic Buffer are bypassed.

The Transmitter Delay Aligner is no longer supported; additionally, the use model of the Receiver Delay Aligner must be changed.

Applications that use the TX Buffer and RX Elastic Buffer are not affected by this errata item.

Applications currently bypassing the TX Buffer and/or RX Elastic Buffer, including XAUI, RXAUI, CPRI, OBSAI, and PLBv46 RC/EP Bridge for PCI Express® IP cores and the Integrated Block for PCIe, must implement the following work-around.

#### Work-around

The TX Buffer and RX Elastic Buffer can still be bypassed using work-arounds described in <u>Answer Record 39430</u> to maximize system margin.

# **Operational Guidelines**

### Design Software Requirements

The devices listed in Table 1, unless otherwise specified, require the following Xilinx development software installations.

- Xilinx ISE Design Suite 12.1 (or later).

- See Known Issues in Answer Record 32929.

# Traceability

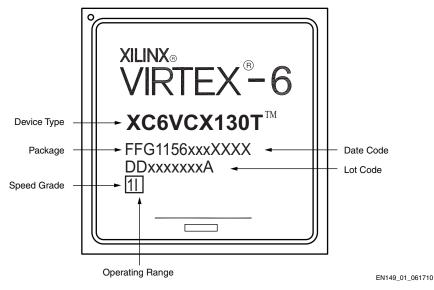

The XC6VCX130T is marked as shown in Figure 1. The other devices listed in Table 1 are marked similarly.

Figure 1: Example Device Top Mark

# **Additional Questions or Clarifications**

For additional questions regarding these errata, contact Xilinx Technical Support: <u>http://www.xilinx.com/support/clearexpress/websupport.htm</u> or your Xilinx Sales Representative: <u>http://www.xilinx.com/company/contact.htm</u>.

## **Revision History**

| Date     | Version | Description                                                                                                                                                                                                                                                                                                                                                          |  |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 06/18/10 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                                                                                                              |  |

| 07/01/10 | 1.1     | Added CX75T and CX195T devices. Removed System Monitor errata; it does not apply to the devices listed in Table 1.                                                                                                                                                                                                                                                   |  |

| 01/17/11 | 1.2     | Added Restriction of Frequency Range for Bandwidth = HIGH or OPTIMIZED and Restriction of Clock<br>Divider Values. Updated TXOUTCLK and RXRECCLK Static Operating Behavior; no longer applicable to<br>TXOUTCLK. Added GTX Transceiver Initialization for Proper TXOUTCLK Functionality. Added GTX<br>Transceiver Delay Aligner per Xilinx Customer Notice XCN11009. |  |

# **Notice of Disclaimer**

THE XILINX HARDWARE FPGA AND CPLD DEVICES REFERRED TO HEREIN ("PRODUCTS") ARE SUBJECT TO THE TERMS AND CONDITIONS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED ON THE XILINX DATA SHEET. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES THE POTENTIAL RISKS OF DEATH, PERSONAL INJURY OR PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT THE SOLE RISK OF CUSTOMER, SUBJECT TO APPLICABLE LAWS AND REGULATIONS. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE.