# Virtex-4 XC4VLX100CES Errata

EN004 (v1.2) February 15, 2006

**Errata Notification**

## Introduction

Thank you for participating in the Xilinx Virtex<sup>™</sup>-4 Engineering Sample Program. As part of this program, we are pleased to provide to you engineering samples of the Virtex-4 XC4VLX100 FPGA. Although Xilinx has made every effort to ensure the highest possible quality, these devices are subject to the limitations described in the following errata.

## **Devices**

These errata apply to the XC4VLX100 devices as shown in Table 1.

#### Table 1: XC4VLX100 FPGA Devices Affected by These Errata

| Devices      | XC4VLX100CES | JTAG ID (Revision Code): 2, 3, 0 |

|--------------|--------------|----------------------------------|

| Packages     | All          |                                  |

| Speed Grades | All          |                                  |

## Hardware Errata Details (JTAG ID = 2, 3)

This section provides a detailed description of each hardware issue known at the release time of this document for devices where JTAG ID = 2, 3.

### FIFO16

The FIFO16 does not correctly generate the ALMOST EMPTY, EMPTY, ALMOST FULL, and FULL flags after the following sequence occurs:

- 1. Read or Write has reached the threshold value of ALMOST EMPTY OFFSET or ALMOST FULL OFFSET.

- 2. A single Read or Write operation is performed, followed by a simultaneous Read or Write operation, when active Read and Write clock edges are very close together.

Unexpected or corrupt data can occur as a result of the flag failures, even if the ALMOST EMPTY or ALMOST FULL flags are not being used.

This issue does not happen in FIFO16 applications where Read and Write never occur simultaneously. Workarounds (downloadable macros) are available for users who are performing simultaneous Read/Writes. Not all workarounds will achieve data sheet performance. See Xilinx answer record 22462 for more details, workaround solutions, and corresponding performance information.

## **Operational Guidelines**

### **Design Software Requirements (JTAG ID = 2, 3)**

The devices covered by these errata, unless otherwise specified, require the following Xilinx development software installations.

Speed specification v1.57 (or later) and Xilinx software ISE 7.1i Service Pack 4 (SP4) or later is required when designing for the devices covered by this errata. Contact Xilinx technical support for SP4 help. Updates are available on the following web page:

http://www.xilinx.com/xlnx/xil\_sw\_updates\_home.jsp

The stepping should be set to "1" in the constraint file (UCF file):

CONFIG STEPPING = "1";

© 2005–2006 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

A summary list of ISE software known issues pertaining to the Virtex-4 features is available at: http://support.xilinx.com/xlnx/xil\_ans\_display.jsp?iLanguageID=1&iCountryID=1&getPagePath=19713

### Notes and Recommendations (JTAG ID = 2, 3)

#### Virtex-II and Virtex-II Pro FPGA Designers

For Virtex-II and Virtex-II Pro designers, the CCLK specification in Virtex-4 devices was changed to LVCMOS 12mA <u>Fast</u> slew rate. Xilinx recommends designing to this new standard.

## Hardware Errata Details (JTAG ID = 0)

This section provides a detailed description of each hardware issue known at the release time of this document.

### FIFO16

The errata for JTAG ID = 0 is the same as the errata for JTAG ID = 2, 3. See FIFO16, page 1.

## Configuration

#### JTAG TDO Output

The JTAG TDO output will 3-state on the rising edge of TCK when the JTAG TAP state machine exits the Shift-DR or Shift-IR states. In the event that the last bit shifted out is a "0," the value might be read as a "1" by the next device in the chain if it has a long hold-time requirement on its TDI pin.

#### Workaround

Provide negative skew on TCK between the Virtex-4 device and the next device in the chain. Refer to answer record 19865.

#### FRAME\_ECC

The FRAME\_ECC logic does not correctly calculate bit failures when readback is performed via JTAG, 8-bit SelectMAP<sup>™</sup> mode, or 8-bit ICAP.

#### Workaround

The FRAME\_ECC block must be used with ICAP32.

#### DSP48

#### CarryIn Input Register

The CarryIn input register from fabric is not supported (that is, the attribute CARRYINREG = 1).

#### Workaround

Use the CLB register to replace the CarryIn input register and set attribute CARRYINREG = 0.

#### Symmetric Rounding Logic

The DSP48 element supports five different modes of symmetric rounding. All four non-pipelined rounding modes are fully supported. Only the pipelined Round (A x B) mode (that is, when CarryInSel[1:0] = 11) is not supported.

#### Workaround

Perform the equivalent logic for carry in a CLB, and connect the carry to the CarryIn input of the DSP48 using CarryInSel[1:0] = 00 (set attribute CARRYINREG = 0).

## DCM

- 1. The DCM attribute CLKOUT\_PHASE\_SHIFT set to the value VARIABLE\_CENTER is not supported.

- If the only clock outputs used from a DCM are CLKFX and/or CLKFX180, and the input clock frequency (CLKIN) is outside of the CLKIN\_FREQ\_DLL\_(HF or LF)\_(MS or MR)\_MIN/MAX range, then use the macro in answer record 20529 to properly generate the LOCKED signal.

- 3. For source-synchronous applications, it is best to use the ChipSync<sup>™</sup> features for the highest performance and lowest skew. If the DCM must be used, follow the guidelines outlined in answer record 20529 to achieve a CLKIN\_CLKFB\_PHASE specification of ±300 ps.

## **Operational Guidelines**

## **Design Software Requirements**

The devices covered by these errata, unless otherwise specified, require the following Xilinx development software installations.

Speed specification v1.57 (or later) and Xilinx software ISE 7.1i Service Pack 4 (SP4) or later is required when designing for the devices covered by this errata. Contact Xilinx technical support for SP4 help. Updates are available on the following web page:

http://www.xilinx.com/xlnx/xil\_sw\_updates\_home.jsp

The Stepping should be set to "ES" in the constraint file (UCF file):

CONFIG STEPPING = "ES";

A summary list of ISE software known issues pertaining to the Virtex-4 features is available at: <u>http://support.xilinx.com/xlnx/xil\_ans\_display.jsp?iLanguageID=1&iCountryID=1&getPagePath=19713</u>

### **Notes and Recommendations**

#### Virtex-II and Virtex-II Pro FPGA Designers

For Virtex-II and Virtex-II Pro designers, the CCLK specification in Virtex-4 devices was changed to LVCMOS 12mA <u>Fast</u> slew rate. Xilinx recommends designing to this new standard.

### **Traceability**

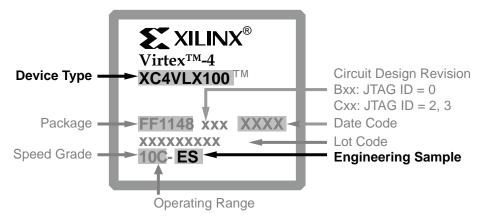

The XC4VLX100 is marked as shown in Figure 1.

Figure 1: Example XC4VLX100CES Package Marking

## **Additional Questions or Clarifications**

All other device functionality and timing meet the data sheet specifications.

For additional questions regarding these errata, please contact your Xilinx Technical Support: <u>http://www.xilinx.com/support/clearexpress/websupport.htm</u> or your Xilinx Sales Representative: <u>http://www.xilinx.com/company/contact.htm</u>.

### **Obtaining the Most Recent Errata Version**

If this document is printed or saved locally in electronic form, check for the most recent release, available to registered users on the Xilinx website at: <u>http://www.xilinx.com/xlnx/xweb/xil\_publications\_index.jsp?category=Errata</u>.

To receive an e-mail alert when this document changes, sign up at: <a href="http://www.xilinx.com/xlnx/xil\_ans\_display.jsp?getPagePath=18815">http://www.xilinx.com/xlnx/xil\_ans\_display.jsp?getPagePath=18815</a>.

These errata apply to the following Virtex-4 documents:

Virtex-4 Overview (http://www.xilinx.com/bvdocs/publications/ds112.pdf)

Virtex-4 Data Sheet (http://www.xilinx.com/bvdocs/publications/ds302.pdf)

Virtex-4 User Guide (http://www.xilinx.com/bvdocs/user guides/ug070.pdf)

XtremeDSP™ Design Guide (<u>http://www.xilinx.com/bvdocs/user guides/ug073.pdf</u>)

Virtex-4 Configuration Guide (http://www.xilinx.com/bvdocs/user guides/ug071.pdf)

Virtex-4 Packaging Guide (http://www.xilinx.com/bvdocs/user guides/ug075.pdf)

## **Revision History**

| Date     | Version | Description                                                                                                                                                                                                                                                                                                                            |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12/09/04 | 1.0     | Initial release.                                                                                                                                                                                                                                                                                                                       |

| 04/13/05 | 1.1     | Added DCM section and revised operational guidelines.                                                                                                                                                                                                                                                                                  |

| 02/15/06 | 1.2     | <ul> <li>Added the FIFO16 section.</li> <li>Updated Design Software Requirements section.</li> <li>Replaced the LVTTL I/O standard with LVCMOS I/O standard in the Notes and Recommendations section.</li> <li>Updated Figure 1.</li> <li>Removed System Monitor errata because it is no longer in the Virtex-4 data sheet.</li> </ul> |