ML410 BSB DDR2

Design

Adding the PLB TEMAC

with SGMII

Using EDK 8.2i SP1

**April 2007**

#### **Overview**

- Hardware Setup

- Software Requirements

- Generate a Bitstream

- Transfer the Bitstream onto the FPGA

- Loading a Bootloop into the Block RAM

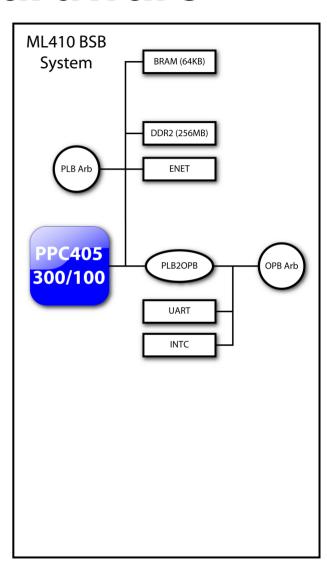

#### **ML410 BSB DDR2 Hardware**

- The ML410 BSB DDR2 design hardware includes:

- 64 KB BRAM

- DDR2 Interface (256 MB)

- UART

- Interrupt Controller

- PLB2OPB Bridge

- PLB and OPB Arbiters

- Networking

## **Additional Setup Details**

- Refer to ml410\_overview\_setup.ppt for details on:

- Software Requirements

- ML410 Board Setup

- Equipment and Cables

- Software

- Network

- Terminal Programs

- This presentation requires the 9600-8-N-1 Baud terminal setup

## **Hardware Setup**

Connect the Xilinx Parallel Cable IV (PC4) to the ML410 board

Connect the RS232 cable to the ML410 board

## **Hardware Setup**

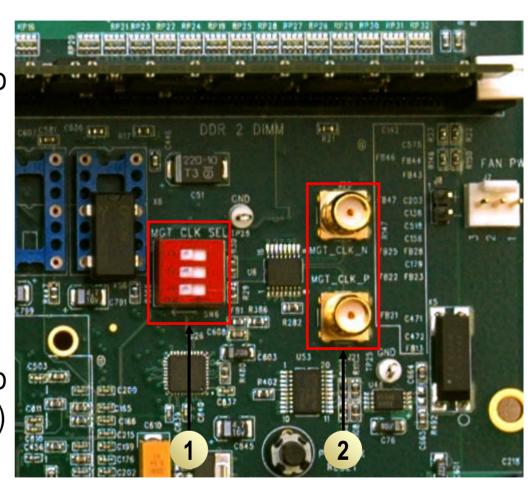

- For Rev D boards only

- Set SW6, MGT\_CLK\_SEL to111 (all switches to the left)(1)

- Connect a 250 MHz

Frequency Clock to

MGT\_CLK\_N/P (2)

- For Rev E boards only

- Set SW6, MGT\_CLK\_SEL to 000 (all switches to the right)

- Rev E boards have an onboard 250 MHz clock

## **Hardware Setup**

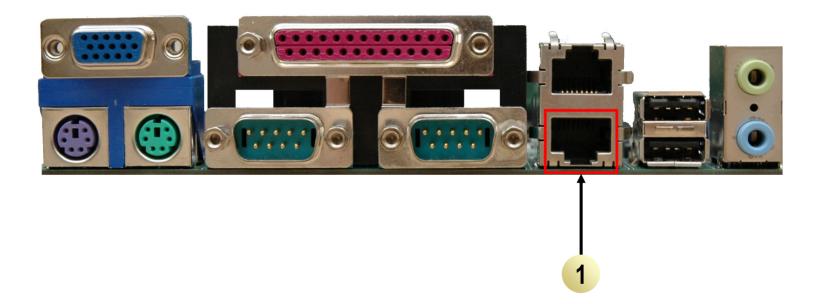

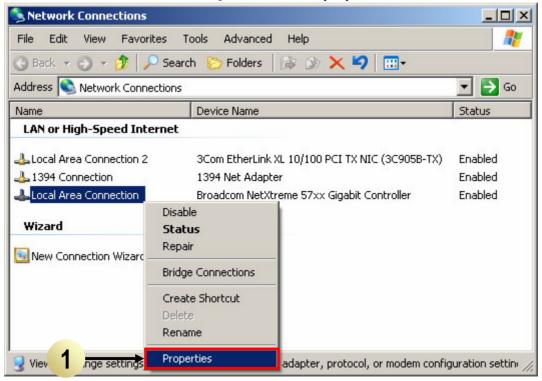

For SGMII, connect an Ethernet crossover cable in the bottom slot (1)

- A Gigabit Ethernet Adapter on your PC is required

- In the Network Connections, right-click on the Ethernet Adapter and select Properties (1)

Set your host (PC) to this IP Address:

| Internet Protocol (TCP/IP) Propertie                                                                                                                                            | s ? ×               |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--|

| General                                                                                                                                                                         |                     |  |

| You can get IP settings assigned automatically if your network supports this capability. Otherwise, you need to ask your network administrator for the appropriate IP settings. |                     |  |

| © <u>O</u> btain an IP address automatical <u>l</u>                                                                                                                             | у                   |  |

| ── Use the following IP address: ——                                                                                                                                             |                     |  |

| <u>I</u> P address:                                                                                                                                                             | 192 . 168 . 0 . 1   |  |

| S <u>u</u> bnet mask:                                                                                                                                                           | 255 . 255 . 255 . 0 |  |

| <u>D</u> efault gateway:                                                                                                                                                        | 192 . 168 . 0 . 254 |  |

| C Obtain DNS server address autom                                                                                                                                               | natically           |  |

| ── Use the following DNS server add                                                                                                                                             | resses:             |  |

| Preferred DNS server:                                                                                                                                                           |                     |  |

| Alternate DNS server:                                                                                                                                                           |                     |  |

|                                                                                                                                                                                 | Ad <u>v</u> anced   |  |

|                                                                                                                                                                                 | OK Cancel           |  |

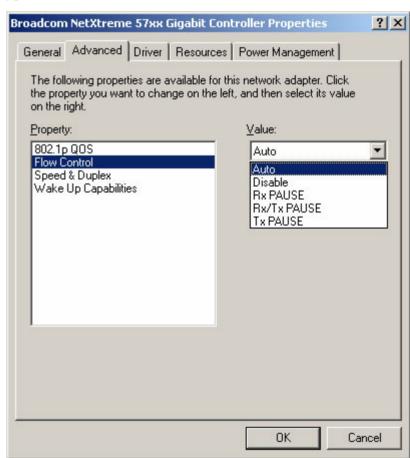

- Click Configure (1)

- Set the Flow Control to Auto

Set Speed & Duplex to Auto

| Broadcom NetXtreme 57xx Gigabit Controller Properties                                                                                                                                                                                                                       | ? ×     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| General Advanced Driver Resources Power Managemen                                                                                                                                                                                                                           | nt      |

| The following properties are available for this network adapter. the property you want to change on the left, and then select its on the right.  Property:  802.1p QOS Flow Control Speed & Duplex Wake Up Capabilities  10 Mb Full 10 Mb Half 100 Mb Full 100 Mb Half Auto | Click   |

| OK                                                                                                                                                                                                                                                                          | Cancel  |

| OK .                                                                                                                                                                                                                                                                        | Caricei |

# ISE Software Requirement

Xilinx ISE 8.2i SP2 software

## **EDK Software Requirement**

Xilinx EDK 8.2i SP1 software

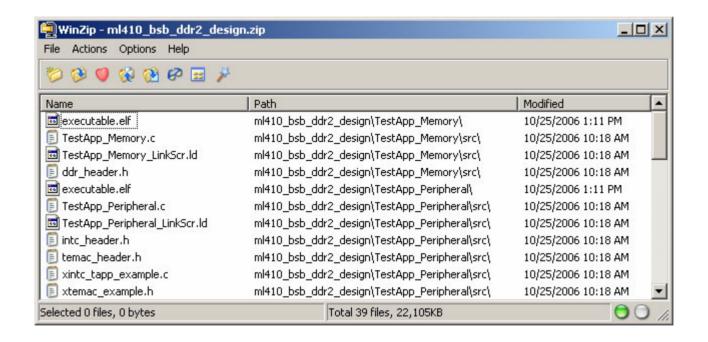

# **Extracting the Design**

- Unzip the ml410\_bsb\_ddr2\_design.zip file

- This creates ISE and EDK project directories

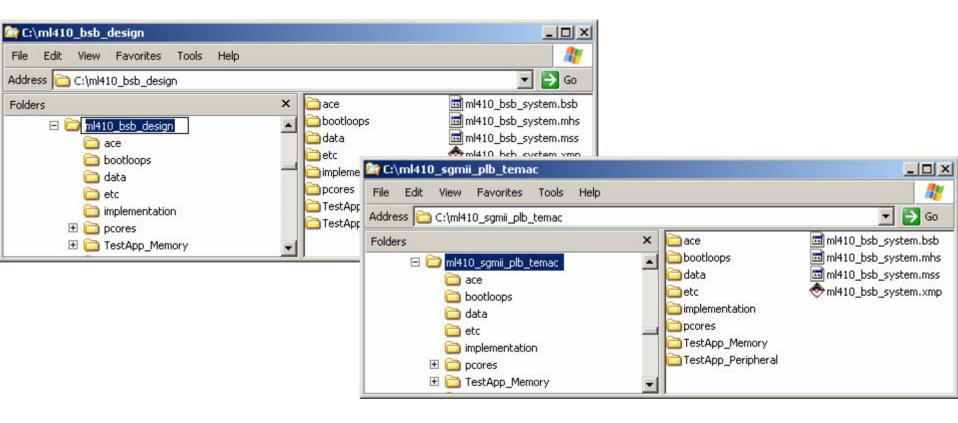

# **Extracting the Design**

Rename the project directory to ml410\_sgmii\_plb\_temac

# **Extracting the Design**

- Unzip the ml410\_plb\_sgmii\_overlay.zip file

- Unzip to the ml410\_sgmii\_plb\_temac directory

- This adds the PLB TEMAC with SGMII to the design directory

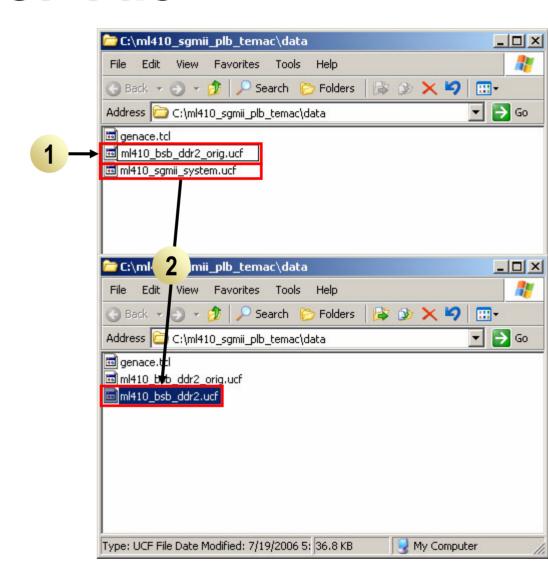

#### **UCF** File

Rename the ml410\_bsb\_ddr2.ucf (1)

Change the file named ml410\_sgmii\_system.ucf to ml410\_bsb\_ddr2.ucf (2)

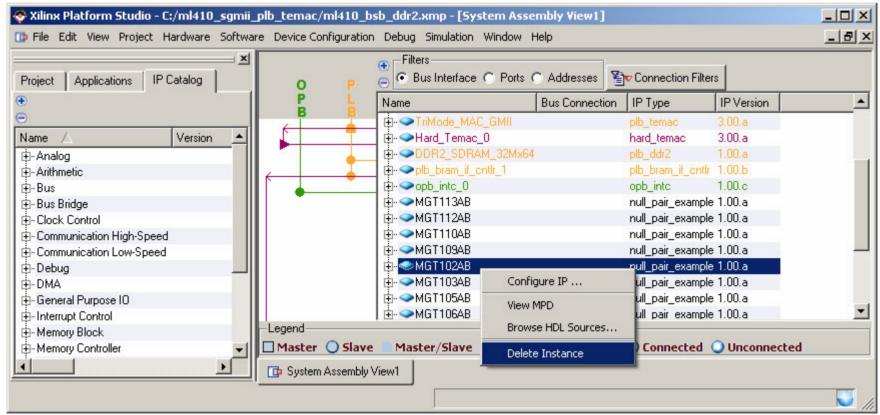

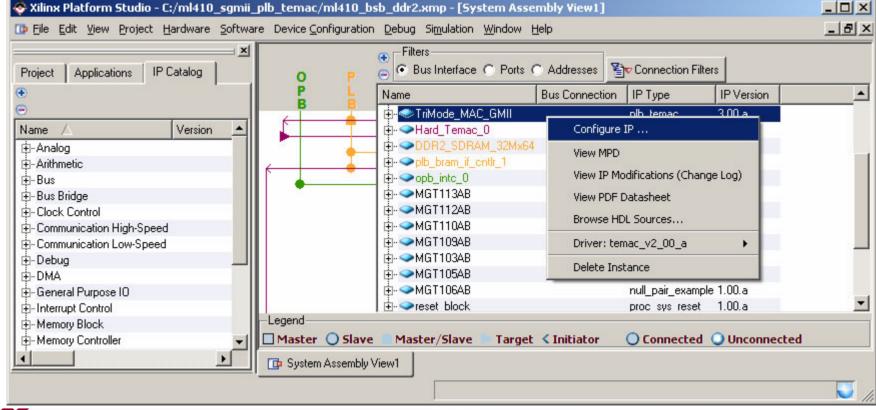

# Add and Configure IP

- Launch EDK project <design path>\ml410\_bsb\_ddr2.xmp

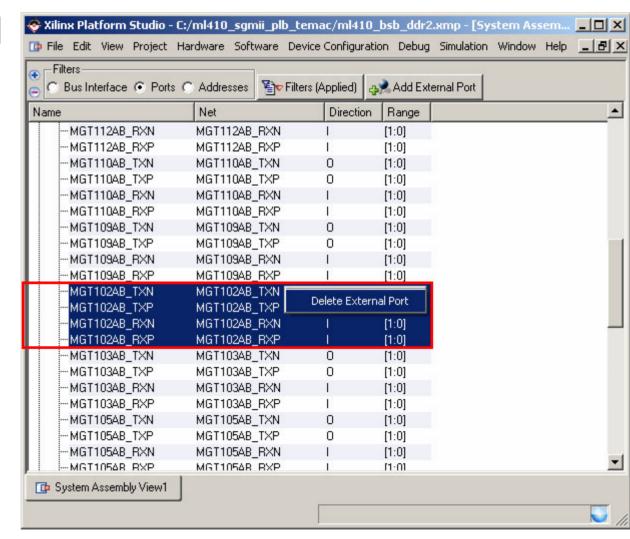

- Delete the MGT Null Tile, MGT102AB

Right-click on the TriMode\_MAC\_GMII and select

Configure IP ...

- Under the User tab, set the following parameters:

- Receiving FIFODepth: 131072

- Transmitting FIFODepth: 131072

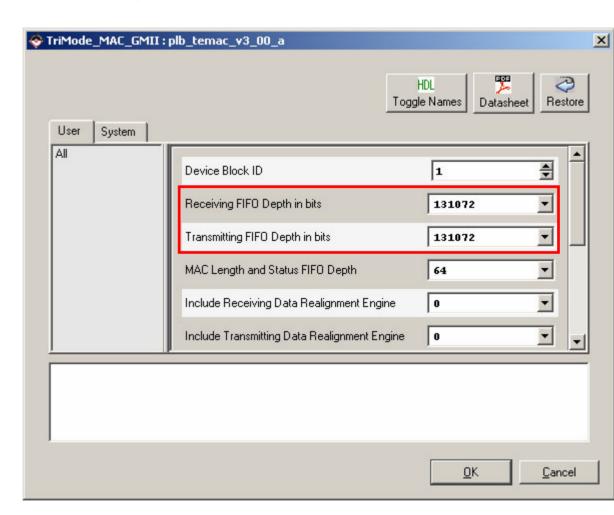

Right-click on the Hard\_Temac\_0 and select Configure IP ...

Set the C\_PHY\_TYPE to 4 for SGMII

| → Hard_Temac_0: hard_temac_v3_00_a △II | HDL Datasheet Restore     |

|----------------------------------------|---------------------------|

| C_PHY_TYPE                             | 4                         |

| C_EMAC1_PRESENT                        | Г                         |

| C_TEMAC0_PHYADDR                       | 00001                     |

| C_TEMAC1_PHYADDR                       | 00010                     |

| C_RGMII_RX_CLK_DELAY                   | 38                        |

| C_IDELAYCTRL_LOC                       | IDELAYCTRL_X1Y5           |

|                                        |                           |

|                                        | <u>O</u> K <u>C</u> ancel |

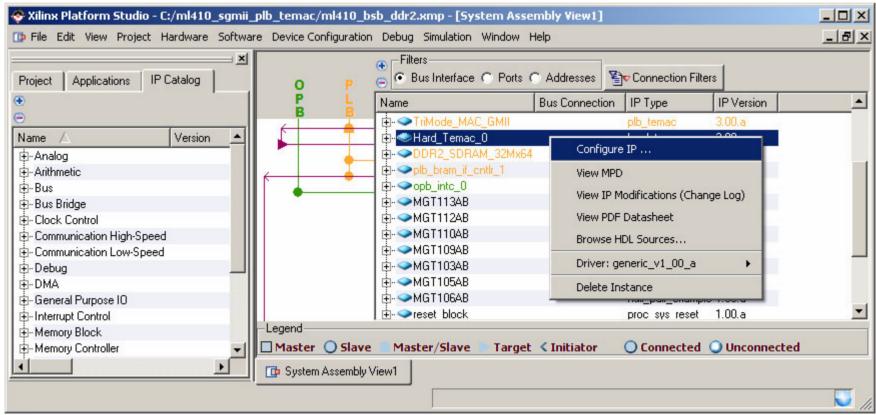

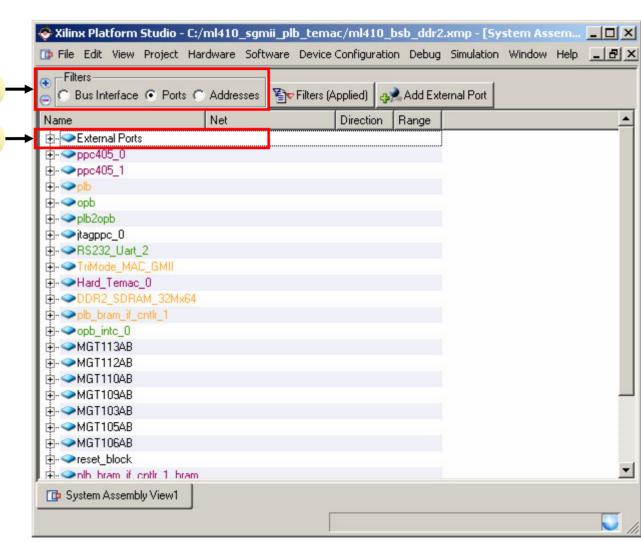

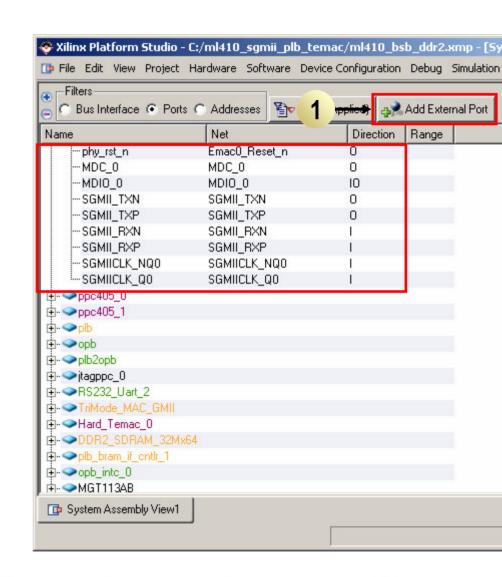

# Add External Ports Connect the Nets

Click on the Ports Button (1)

Expand the 2

External Ports (2)

Delete the existing Ethernet ports

```

🔗 Xilinx Platform Studio - C:/ml410_sgmii_plb_temac/ml410_bsb_ddr2.xmp - [System Assem... 🖃 🗖 🔀

🕩 File Edit View Project Hardware Software Device Configuration Debug Simulation Window Help 💶 🗗 🔀

Filters-

C Bus Interface @ Ports C Addresses

Filters (Applied)

Add External Port

Direction Range

Net

Name

🖮 🥯 External Ports

"fpga_0_RS232_Uart_2... fpga_0_RS232_Uart_2... I

-fpga_0_RS232_Uart_2... fpga_0_RS232_Uart_2... 0

-fpga_0_RS232_Uart_2... fpga_0_RS232_Uart_2_... I

-fpga_0_RS232_Uart_2... fpga_0_RS232_Uart_2... 0

-fpga_0_ORGate_1_Re... fpga_0_ORGate_1_Res = 0

-fpga_0_0RGate_1_Re... fpga_0_0RGate_1_Res 0

-fpga 0 ORGate 1 Re... fpga 0 ORGate 1 Res O

fpga_0_Hard_Temac_0... fpga_0<del>======</del>

[3:0]

Delete External Port

fpga 0 Hard Temac 0... fpga (

fpga_0_Hard_Temac_0... fpga_0_Hard_Temac_0... 0

fpga 0 Hard Temac O... fpga 0 Hard Temac O... I

[3:0]

fpga 0 Hard Temac 0... fpga 0 Hard Temac 0... I

fpga 0 Hard Temac 0... fpga 0 Hard Temac 0... I

fpga 0 Hard Temac 0... fpga 0 Hard Temac 0... I

fpga 0 Hard Temac 0... fpga 0 Hard Temac 0... I

fpga_0_Hard_Temac_0... fpga_0_Hard_Temac_0... 10

fpga 0 Hard Temac 0... fpga 0 Hard Temac 0... 0

fpga 0 TriMode_MAC_... fpga_0_TriMode_MAC_... 0

fpga 0 DDR2 SDRAM...fpga 0 DDR2 SDRAM... 0

-fpga_0_DDR2_SDRAM... fpga_0_DDR2_SDRAM... O

[0:12]

"foga 0 DDB2 SDBAM foga 0 DDB2 SDBAM 0

m:11

□ System Assembly View1

```

Delete the 4 External Ports for MGT102AB

- Use the Add External Port button (1) to add these Ports:

- phy\_rst\_n = Emac0\_Reset\_n

- MDC\_0 = MDC\_0

- MDIO\_0 = MDIO\_0

- SGMII\_TXN = SGMII\_TXN

- SGMII\_TXP = SGMII\_TXP

- SGMII\_RXN = SGMII\_RXN

- SGMII\_RXP = SGMII\_RXP

- SGMIICLK\_NQ0 = SGMIICLK\_NQ0

- SGMIICLK\_Q0 = SGMIICLK\_Q0

- Set the direction as shown

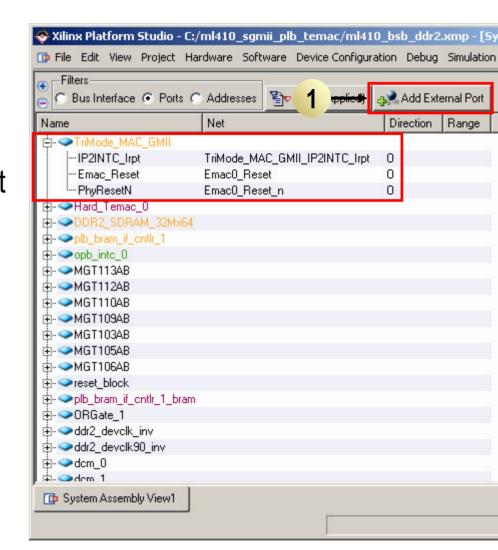

- Add the following ports to TriMode\_MAC\_GMII:

- IP2INTC\_Irpt =

TriMode\_MAC\_GMII\_IP2INTC\_Irpt

- Emac\_Reset = Emac0\_Reset

- PhyResetN = Emac0\_Reset\_n

- Set the direction as shown

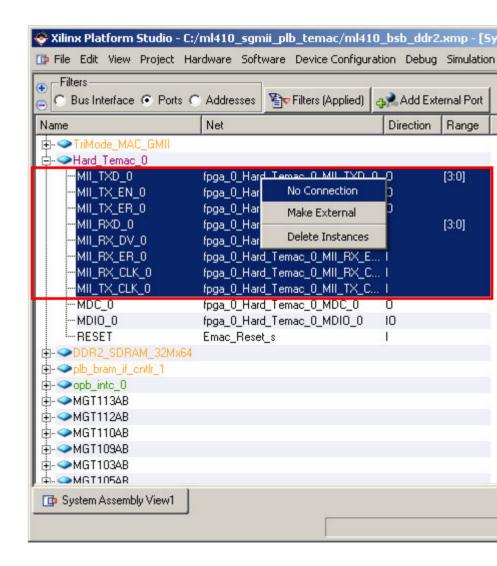

- Set these connections to No Connection:

- MII\_TXD\_0

- MII\_TX\_EN\_0

- MII\_TX\_ER\_0

- MII\_RXD\_0

- MII\_RX\_DV\_0

- MII\_RX\_ER\_0

- MII\_RX\_CLK\_0

- MII\_TX\_CLK\_0

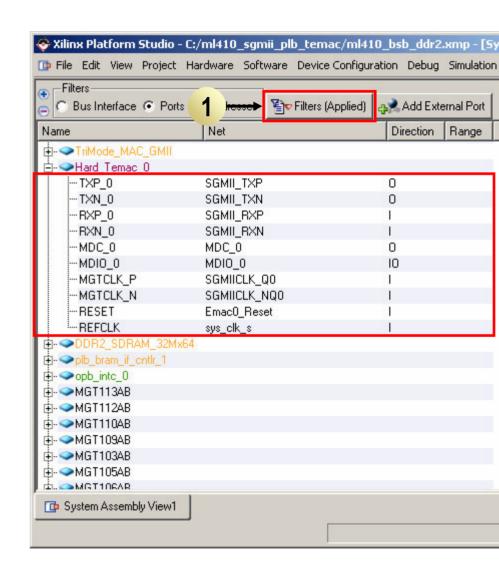

- Click on Filters to show unconnected nets (1)

- Add the following ports to hard\_temac:

- TXP\_0 = SGMII\_TXP

- TXN\_0 = SGMII\_TXN

- RXP\_0 = SGMII\_RXP

- RXN\_0 = SGMII\_RXN

- MDC\_0= MDC\_0

- MDIO\_0 = MDIO\_0

- MGTCLK\_P = SGMIICLK\_Q0

- MGTCLK\_N = SGMIICLK\_NQ0

- RESET = Emac0\_Reset

- REFCLK = sys\_clk\_s

- Set the direction as shown

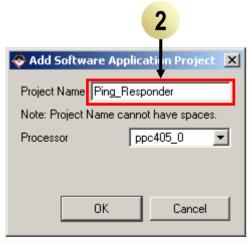

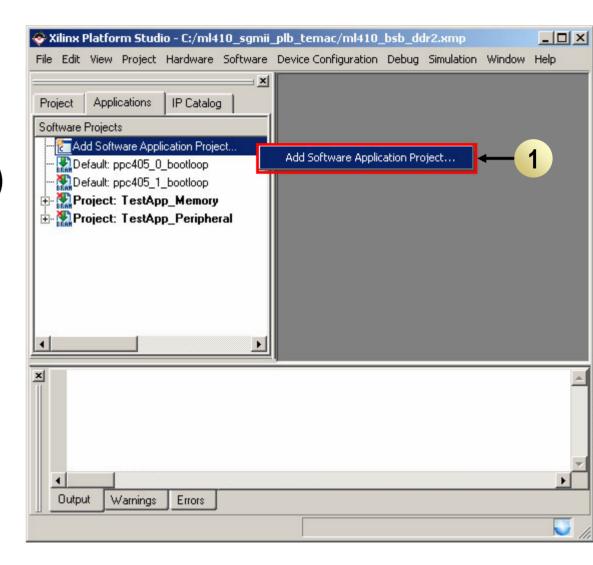

- Right-click on Software

Projects and select

Add Software

Application Project (1)

- Name this project

Ping\_Responder (2)

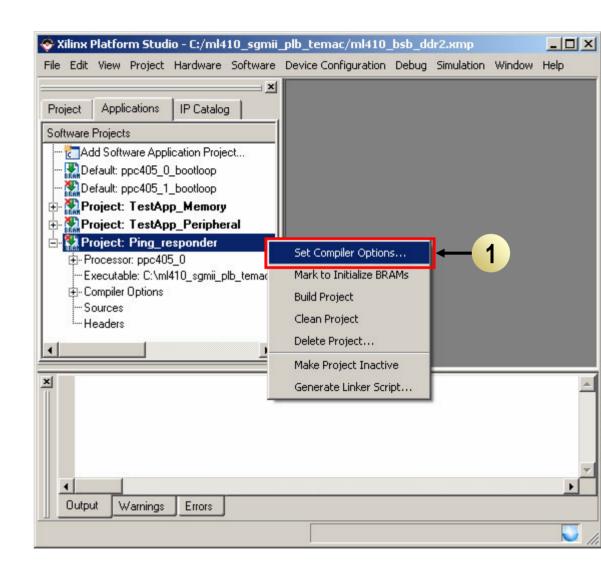

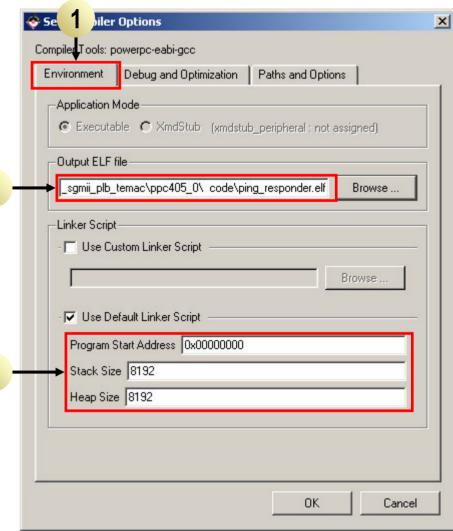

Right-click on Ping\_Responder and select Set Compiler Options... (1)

- Under the Environment tab (1):

- Set the ELF output file to (2):

<design path>\ppc405\_0\

code\ping\_responder.elf

- Set Program Start Address to (3):

0x0000000

- Set Stack and Heap to 8192 (3)

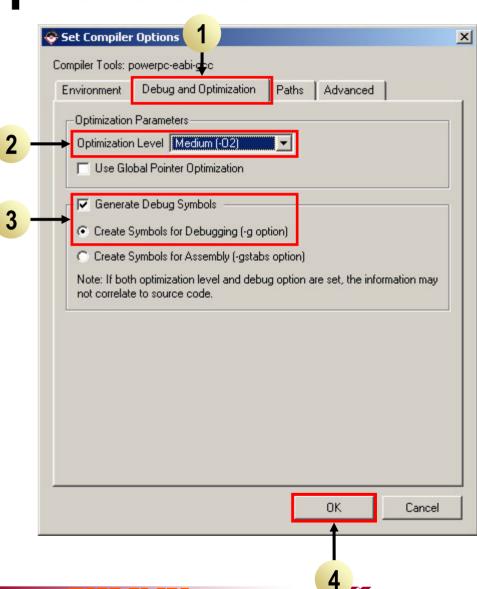

- Under the Optimization tab (1):

- Set optimization to Medium (2)

- Set debugging options to: Create Symbols for Debugging (-g option) (3)

- Click OK (4)

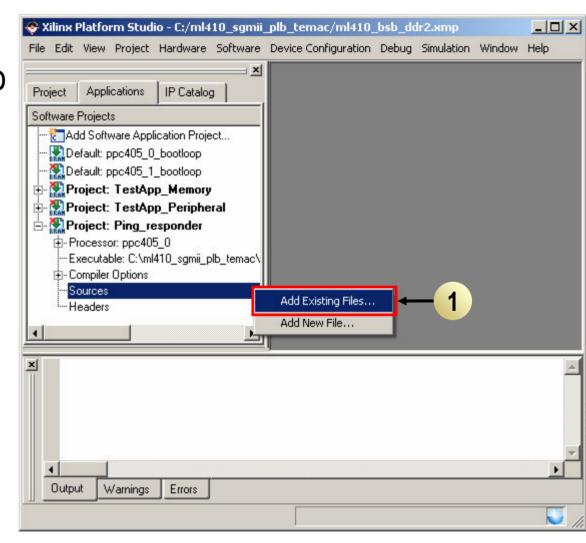

- In the <design path>\sw \standalone\Ping\_Respo nder\ directory, add these source files to the project (1):

- ethernet.c

- mdio.c

- ping\_responder.c

- serial\_io.c

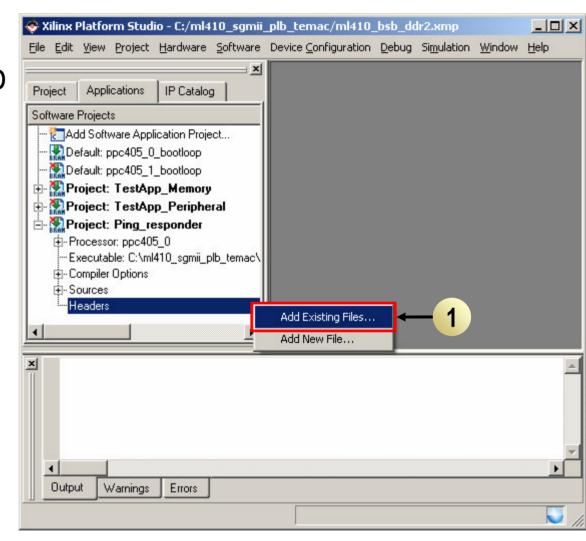

# **Adding Applications**

- In the <design path>\sw \standalone\Ping\_Respo nder\ directory, add these header files to the project (1):

- ethernet.h

- ping\_responder.h

- serial\_io.h

# **Adding Applications**

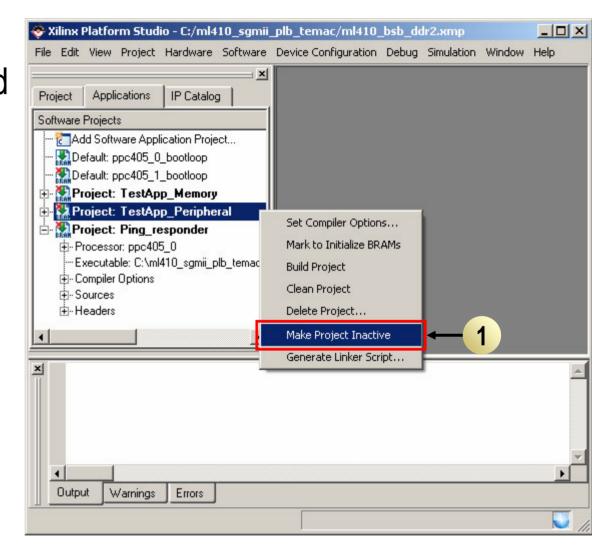

Right-click on

TestApp\_Peripheral and select Make

Project Inactive (1)

## **Update MSS File**

- Close the EDK Project prior to making this edit

- Reopen the EDK Project when finished

- Change the plb\_temac driver version:

- From PARAMETER DRIVER\_VER = 2.00.a

- To PARAMETER DRIVER\_VER = 1.00.a

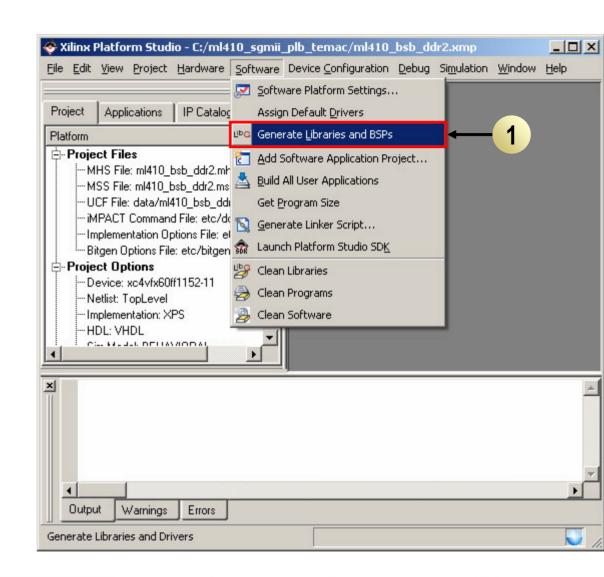

### **Generate Bitstream**

- Generate the libraries needed to create the bitstream

- Select Software →

Generate Libraries

and BSPs (1)

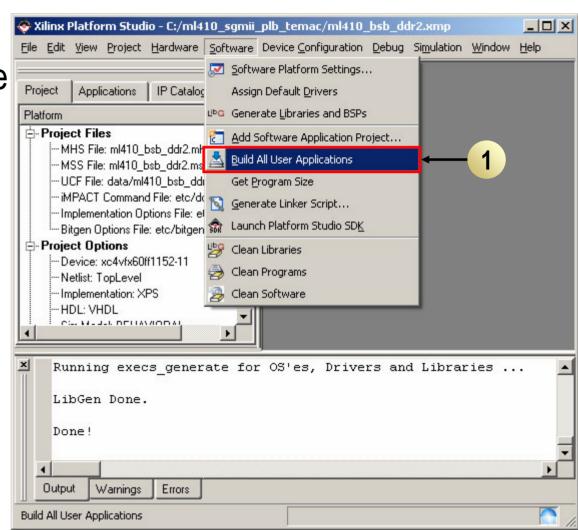

### **Generate Bitstream**

- Compile the applications and create an executable (executable.elf)

- Select Software →

Build All User

Applications (1)

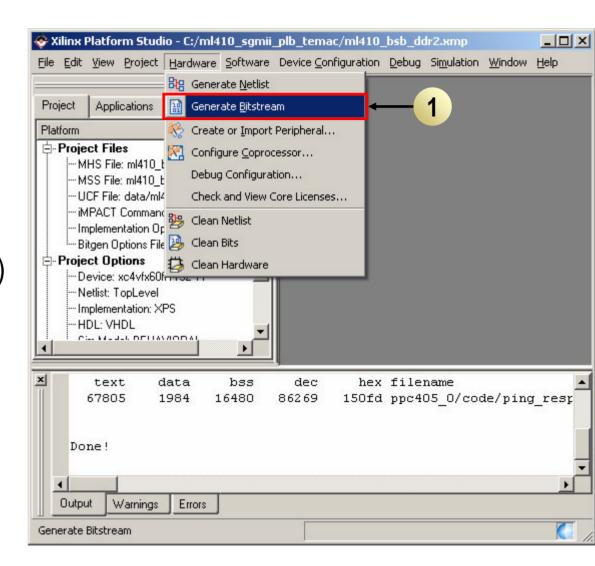

### **Generate Bitstream**

- Create the hardware design that is located in <project directory> /implementation

- Select Hardware →

Generate Bitstream (1)

(Takes roughly

90 minutes)

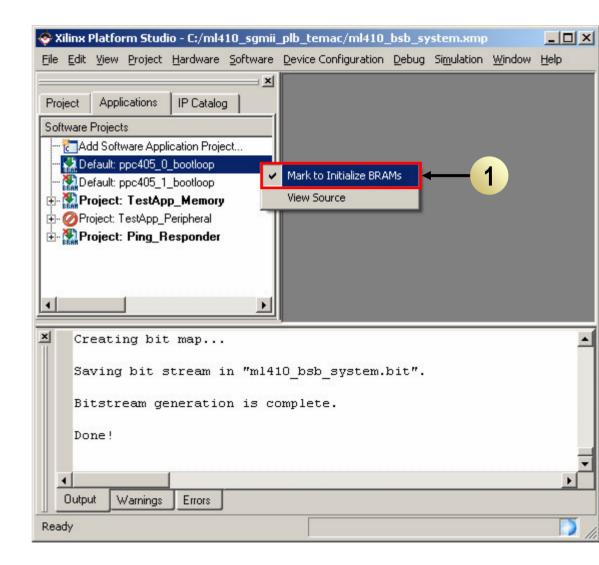

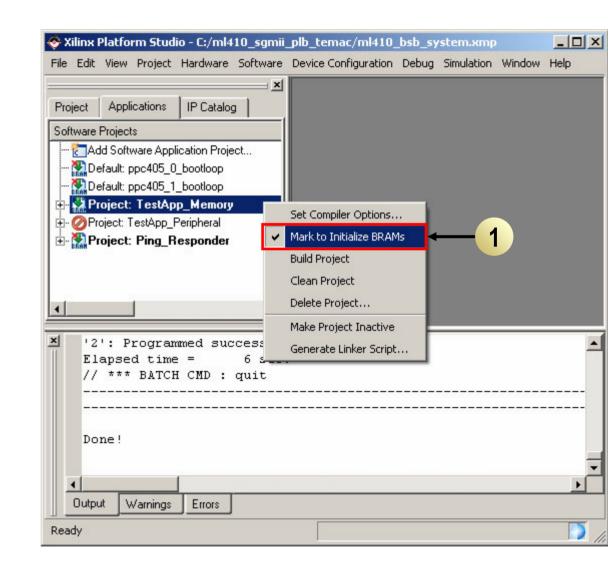

PRIGHT-click the ppc405\_0\_bootloop project and de-select Mark to Initialize BRAMs (1)

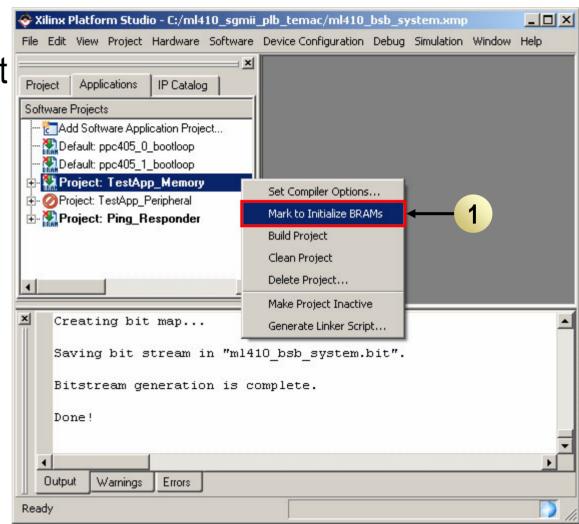

- Right-click the

TestApp\_Memory project

and select Mark to

Initialize BRAMs (1)

- Now the TestApp\_Memory will be instantiated into the block RAM rather than the bootloop ELF

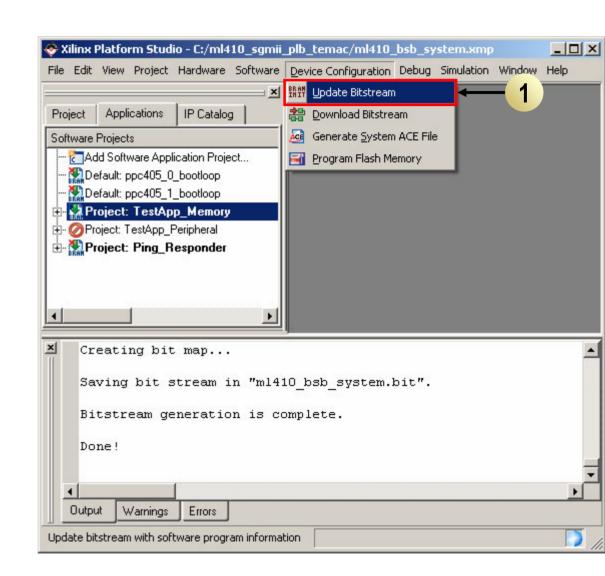

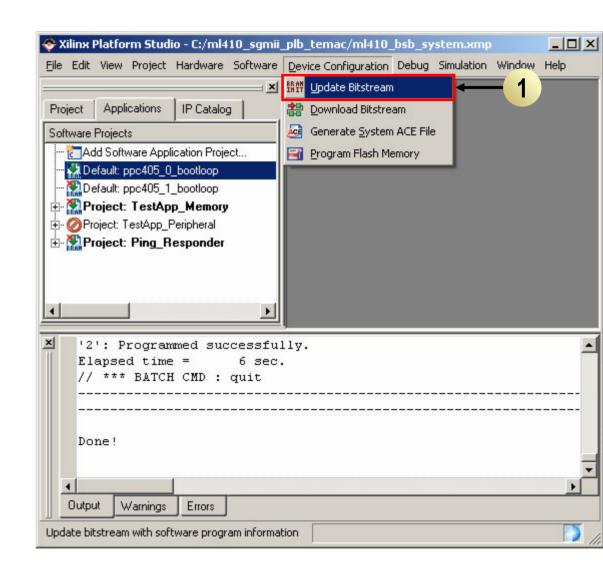

- Update the bitstream (download.bit) with the TestApp\_Memory ELF File

- Select Device

Configuration →

Update Bitstream (1)

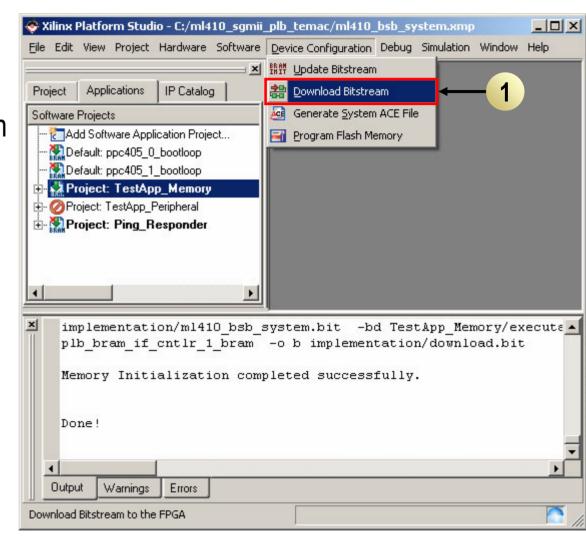

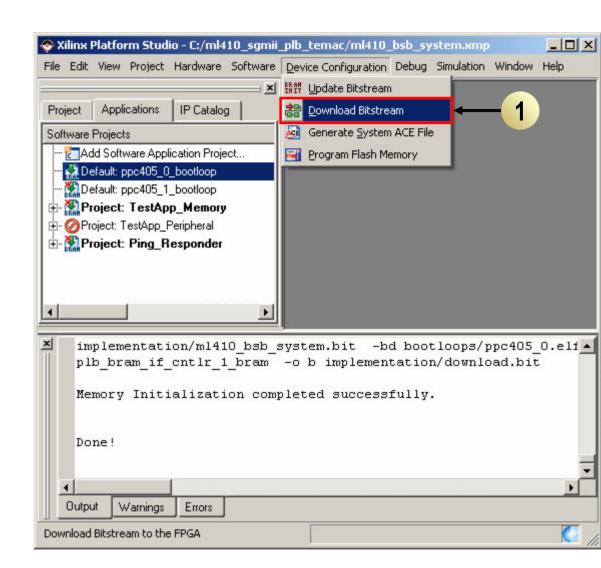

- Download the new bitstream (download.bit)

- Open a terminal program to view the output of the TestApp executable

- Select Device

Configuration →

Download

Bitstream (2)

View the output of a successful bitstream download in the terminal window

```

Tera Term - COM1 VI

File Edit Setup Control Window Help

-- Entering main() --

Starting MemoryTest for DDR_SDRAM_32Mx64:

Running 32-bit test...PASSED!

Running 16-bit test...PASSED!

Running 8-bit test...PASSED!

-- Exiting main() --

```

- A concatenated software/hardware file, known as an ACE file, is useful for loading large programs, such as a VxWorks or Linux demo, into the external memory

- A bootloop program must be used to occupy the processor until the software is loaded into memory

- The following pages show how to initialize a bootloop program into block RAM and to test its existence

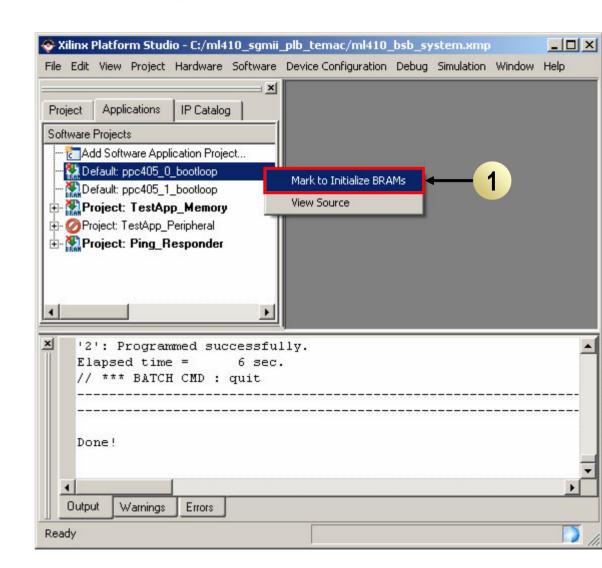

- Right-click the

TestApp\_Memory

project and de-select

Mark to Initialize

BRAMs (1)

- This will prevent the TestApp program from being inserted into the block RAM when the new bitstream is created

- Right-click the ppc405\_0\_bootloop project and select

Mark to Initialize BRAMs (1)

- Now bootloop will be instantiated into the block RAM rather than the TestApp project

- Update the bitstream (download.bit) with a bootloop ELF file (ppc405\_0.elf)

- Select Device

Configuration →

Update Bitstream (1)

- Load the new design onto the FPGA and load the bootloop program into the block RAM

- Select Device

Configuration →

Download

Bitstream (1)

- A memory read can be executed to test if the bootloop was successfully loaded

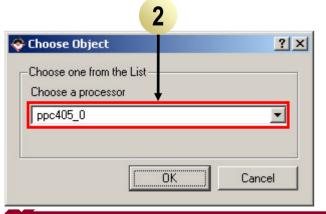

- Select Debug →

Launch XMD (1)

- Select ppc405\_0 (2)

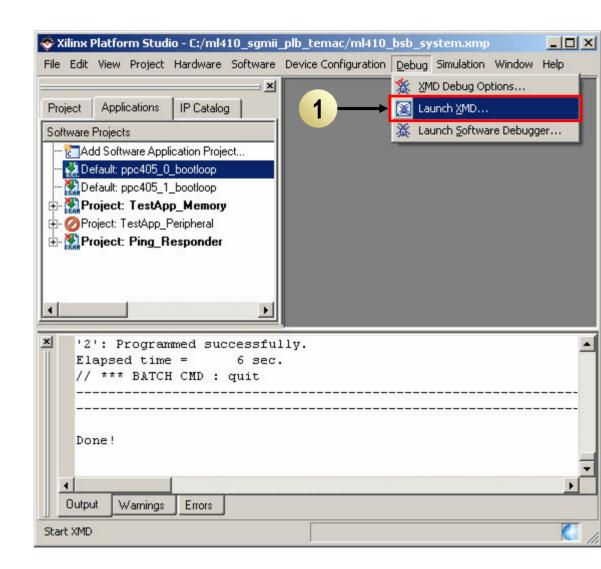

## XMD Setup

- The first time XMD runs on a project, the options will be set

- Click OK (1)

- Click Save (2)

XMD opens and connects to the processor, using the default options

```

C:\EDK Im Sp1.3.2\bin\nt\xmd.exe

Driver xpc4drvr.sys version = 1.0.4.0. LPT base address = 0378h.

Cable Type = 1, Revision = 3.

Setting cable speed to 5 MHz.

Cable connection established.

INFO:MDT - Assumption: Selected Device 2 for debugging.

JTAG chain configuration

Device

IR Length

Part Name

ID Code

System ACE

0a001093

01eh4093

XMD: Connected to PowerPC target. Processor Version No : 0x20011470

Address mapping for accessing special PowerPC features from XMD/GDB:

I-Cache (Data) :

I-Cache (Tag)

D-Cache (Data)

D-Cache (Tag)

ISOCM

Connected to "ppc" target. id = 0

Starting GDB server for "ppc" target (id = 0) at TCP port no 1234

XMD%

```

- To execute a memory read, type mrd 0xfffffffc

- This will read the memory address at the reset vector; the value should be 0x48000000 as shown below

```

_ | | ×

C:\EDK Im Sp1.3.2\bin\nt\xmd.exe

Cable connection established.

INFO:MDT - Assumption: Selected Device 2 for debugging.

JTAG chain configuration

Device

ID Code

IR Length

Part Name

0a001093

System ACE

XMD: Connected to PowerPC target. Processor Version No : 0x20011470

Address mapping for accessing special PowerPC features from XMD/GDB:

I-Cache (Data) :

I-Cache (Tag)

D-Cache (Data)

D-Cache (Tag)

ISOCM

Connected to "ppc" target. id = 0

Starting GDB server for "ppc" target (id = 0) at TCP port no 1234

XMD% mrd Øxfffff

XMD%

```

#### **Download ELF File**

Download the ping\_responder ELF file from XMD rst

dow ppc405\_0/code/ping\_responder.elf (1)

```

C:\EDK Im Sp1.3.2\bin\nt\xmd.exe

Target reset successfully

XMD% dow ppc405_0/code/ping_responder.elf

section, .text: ขxขขขขขขข-ขxขขขบta10

section, .init: 0x0000fa10-0x0000fa34

section, .fini: 0x0000fa34-0x0000fa54

section, .boot0: 0x000150f0-0x00015100

section, .boot: 0xfffffffc-0x00000000

section, .rodata: 0x0000fa58-0x000108cd

section, .sdata2: 0x000108d0-0x000108d0

section, .sbss2: 0x000108d0-0x000108d0

section, .data: 0x000108d0-0x00010fe8

section, .fixup: 0x00010fe8-0x00010fe8

section, .got1: 0x00010fe8-0x00010fe8

section, .got2: 0x00010fe8-0x00011004

section, .ctors: 0x00011004-0x0001100c

section, .dtors: 0x0001100c-0x00011014

section, .got: 0x00011014-0x00011014

section, .eh_frame: 0x00011014-0x0001106c

section, .jcr: 0x0001106c-0x00011070

section, .gcc_except_table: 0x00011070-0x00011070

section, .sdata: 0x00011070-0x00011090

section. .sbss: 0x00011090-0x000110ac

section. .bss: 0x000110ac-0x000150f0

Downloaded Program ppc405_0/code/ping_responder.elf

Setting PC with program start addr = 0xffffffffc

PC reset to Øxffffffffc, Clearing MSR Register

```

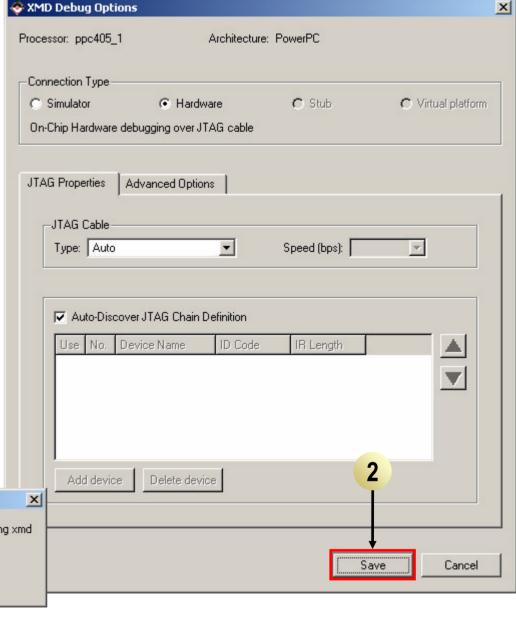

- Open a terminal program

- Enter con in the XMD window to start Ping Responder (1)

```

C:\EDK Im Sp1.3.2\bin\nt\xmd.exe

XMD% dow ppc405_0/code/ping_responder.elf

section, .text: 0x00000000-0x0000fa10

section, .init: 0x0000fa10-0x0000fa34

section, .fini: 0x0000fa34-0x0000fa54

section, .boot0: 0x000150f0-0x00015100

section, .boot: 0xfffffffc-0x00000000

section, .rodata: 0x0000fa58-0x000108cd

section, .sdata2: 0x000108d0-0x000108d0

section, .sbss2: 0x000108d0-0x000108d0

section, .data: 0x000108d0-0x00010fe8

section, .fixup: 0x00010fe8-0x00010fe8

section, .got1: 0x00010fe8-0x00010fe8

section, .got2: 0x00010fe8-0x00011004

section, .ctors: 0x00011004-0x0001100c

section, .dtors: 0x0001100c-0x00011014

section, .got: 0x00011014-0x00011014

section, .eh_frame: 0x00011014-0x0001106c

section, .jcr: 0x0001106c-0x00011070

section, .gcc_except_table: 0x00011070-0x00011070

section, .sdata: 0x00011070-0x00011090

section, .sbss: 0x00011090-0x000110ac

section. .bss: 0x000110ac-0x000150f0

Downloaded Program ppc405_0/code/ping_responder.elf

Setting PC with program start addr = 0xffffffffc

PC reset to Oxffffffffc. Clearing MSR Register

rrocessor started. Type "stop" to stop processor

RUNNI NG>

```

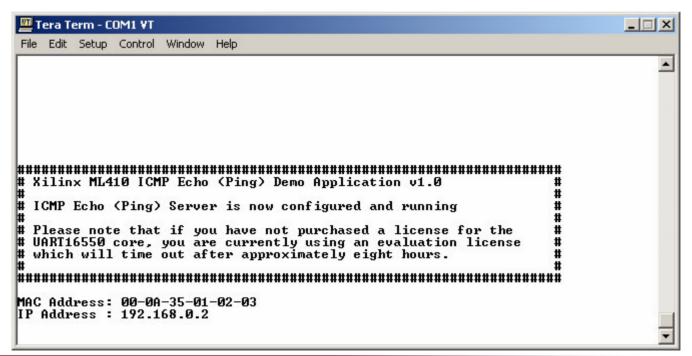

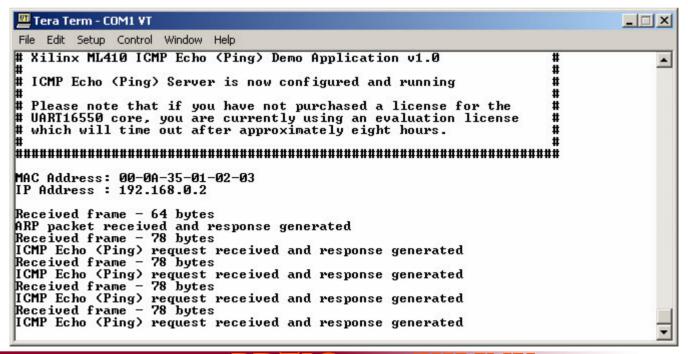

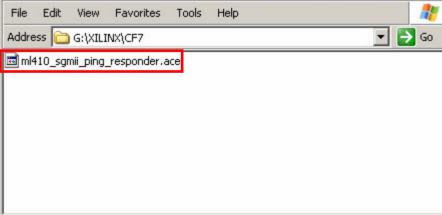

- View the output in the terminal program

- Ping Responder is running in external memory of ML410 (below)

After setting up the PHY, the program awaits a network ping:

## **Ping ML410 Target from Host**

- Open a DOS window on the PC Host (Start → Programs → Accessories → Command Prompt)

- Type ping 192.168.0.2 (1)

- Ping from PC host 192.168.0.1 to ML410 target 192.168.0.2

- You may see some timeouts on the PC

```

Microsoft Windows XP [Version 5.1.2600]

(C) Copyright 1985-2001 Microsoft Corp.

C:\>ping 192.168.0.2

Pinging 192.168.0.2 with 32 bytes of data:

Request timed out.

Reply from 192.168.0.2: bytes=32 time=232ms TTL=128

Reply from 192.168.0.2: bytes=32 time=85ms TTL=128

Reply from 192.168.0.2: bytes=32 time=194ms TTL=128

Ping statistics for 192.168.0.2:

Packets: Sent = 4, Received = 3, Lost = 1 (25% loss),

Approximate round trip times in milli-seconds:

Minimum = 85ms, Maximum = 232ms, Average = 170ms

C:\>

```

- The program responds to incoming pings

- It also notes and ignores any other packets on the network

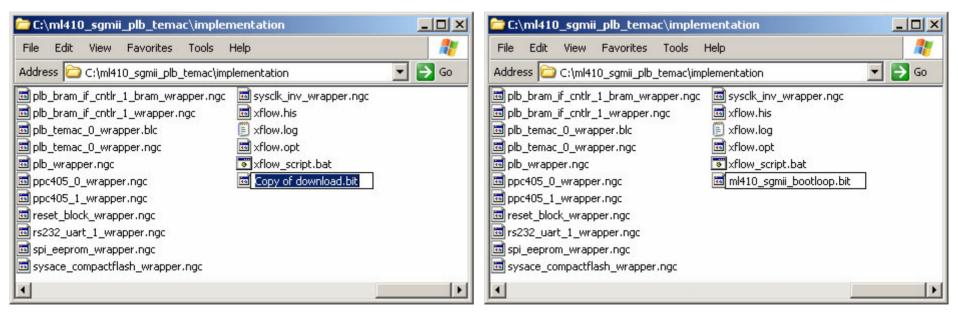

Make a copy of the updated bitstream (download.bit) and rename it ml410\_sgmii\_bootloop.bit

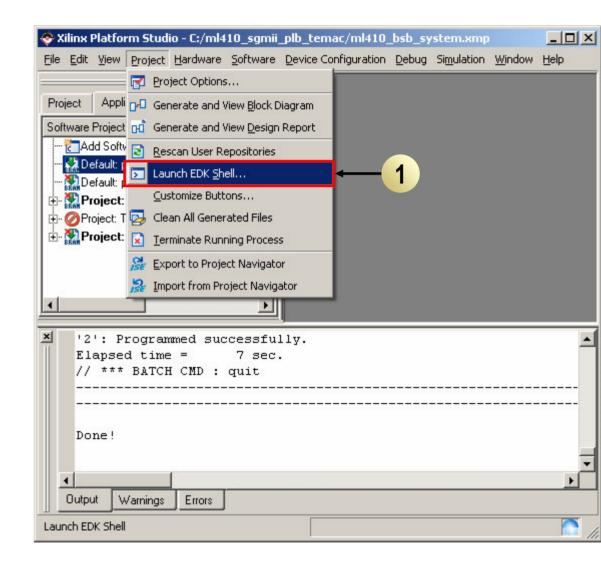

#### Create an ACE File

- Open an EDK shell

- Select Project →LaunchEDK Shell (1)

- This shell is used for entering and executing the commands to create a concatenated (HW+SW) ACE file

### Create an ACE File

• At the bash prompt, type (1):

cd ace

./genace\_sgmii\_ping\_responder.sh

```

bash-2.05$ cd ace ./yenace_symii_ping_responder.sh

```

#### Create an ACE File

- This creates a concatenated (HW+SW) ACE file

- Input: ping responder ELF file, ml410\_sgmii\_bootloop.bit

- Genace\_sgmii\_ping\_responder.sh uses XMD and a genace.tcl script with ML410 appropriate options to generate an ACE file (1)

```

C:\EDK_Im_Sp1.3.2\bin\nt\xbash.exe

section. .eh frame: 0x00011014-0x0001106c

section. .jcr: 0x0001106c-0x00011070

section. .gcc except table: 0x00011070-0x00011070

section. .sdata: 0x00011070-0x00011090

section. .sbss: 0x00011090-0x000110ac

section. .bss: 0x000110ac-0x000150f0

Downloaded Program ../ppc405_0/code/ping_responder.elf

Setting PC with program start addr = 0xffffffffc

PC reset to Øxffffffffc. Clearing MSR Register

Copying ../ppc405_0/code/ping_responder.svf File to _m1410_sgmii_ping_responder.

svf File

Writing Processor JTAG "continue" command to SUF file 'sw_suffix.svf'

Processor started. Type "stop" to stop processor

Converting SUF file 'ml410_sgmii_ping_responder.svf' to SystemACE file 'ml410_sg

mii_ping_responder.ace'

Executing 'impact -batch svf2ace.scr'

SystemACE file 'ml410_sgmii_ping_responder.ace' created successfully

```

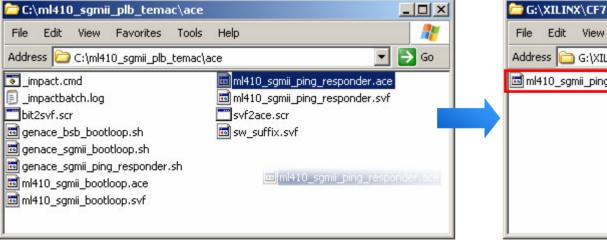

#### Run ACE File

- Copy ml410\_sgmii\_ping\_responder.ace to the xilinx\cf7 directory on your CompactFlash card

- Important: Delete any existing ace files in this CF7 directory

- Note: Use a CompactFlash reader to mount the CompactFlash as a disk drive

\_ | D | X

#### Run ACE File

- Eject the CompactFlash from your PC and insert it back into the ML410

- Type 7 to run the newly created ACE file

```

File Edit Setup Control Window Help

ML410 ACE-loader

Enter Desired System ACE CF Configuration <0-7>.

Ø: ACE-loader.

1: Configuration 1.

2: Configuration 2

3: Configuration 3

4: Configuration 4

5: Configuration 5

6: Configuration 6

7: Configuration 7

Select <0-7>: Rebooting to System ACE Configuration Address 7...

```

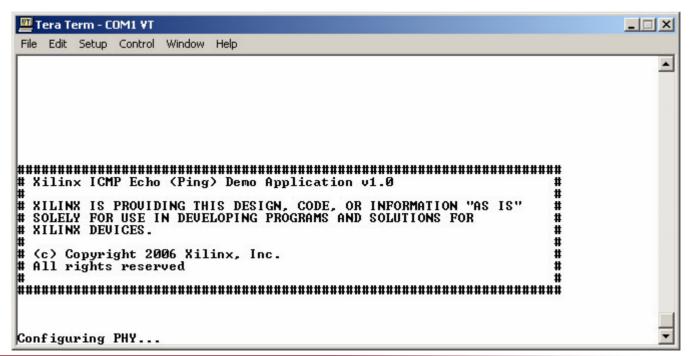

## Using the ACE File

Ping Responder output after booting ACE file

### **Available Documentation**

- Platform Studio Documentation

- Embedded Development Kit (EDK) Resources

<a href="http://www.xilinx.com/ise/embedded\_design\_prod/platform\_studio.htm">http://www.xilinx.com/ise/embedded\_design\_prod/platform\_studio.htm</a>

- OS and Libraries Document Collection

<a href="http://www.xilinx.com/ise/embedded/oslib\_rm.pdf">http://www.xilinx.com/ise/embedded/oslib\_rm.pdf</a>

- ML410

- ML410 User's Guide

<a href="http://www.xilinx.com/bvdocs/userguides/ug085.pdf">http://www.xilinx.com/bvdocs/userguides/ug085.pdf</a>

- ML410 Overview<a href="http://www.xilinx.com/ml410">http://www.xilinx.com/ml410</a>

- ML410 Schematics

http://www.xilinx.com/products/boards/ml410/docs/ml410\_revE.pdf