# ML40*x* EDK Processor Reference Design

## User Guide for EDK 8.1

UG082 (v5.0) June 30, 2006

www.BDTIC.com/XILINX

Xilinx is disclosing this Document and Intellectual Property (hereinafter "the Design") to you for use in the development of designs to operate on, or interface with Xilinx FPGAs. Except as stated herein, none of the Design may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Any unauthorized use of the Design may violate copyright laws, trademark laws, the laws of privacy and publicity, and communications regulations and statutes.

Xilinx does not assume any liability arising out of the application or use of the Design; nor does Xilinx convey any license under its patents, copyrights, or any rights of others. You are responsible for obtaining any rights you may require for your use or implementation of the Design. Xilinx reserves the right to make changes, at any time, to the Design as deemed desirable in the sole discretion of Xilinx. Xilinx assumes no obligation to correct any errors contained herein or to advise you of any correction if such be made. Xilinx will not assume any liability for the accuracy or correctness of any engineering or technical support or assistance provided to you in connection with the Design.

THE DESIGN IS PROVIDED "AS IS" WITH ALL FAULTS, AND THE ENTIRE RISK AS TO ITS FUNCTION AND IMPLEMENTATION IS WITH YOU. YOU ACKNOWLEDGE AND AGREE THAT YOU HAVE NOT RELIED ON ANY ORAL OR WRITTEN INFORMATION OR ADVICE, WHETHER GIVEN BY XILINX, OR ITS AGENTS OR EMPLOYEES. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DESIGN, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND NONINFRINGEMENT OF THIRD-PARTY RIGHTS.

IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOST DATA AND LOST PROFITS, ARISING FROM OR RELATING TO YOUR USE OF THE DESIGN, EVEN IF YOU HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. THE TOTAL CUMULATIVE LIABILITY OF XILINX IN CONNECTION WITH YOUR USE OF THE DESIGN, WHETHER IN CONTRACT OR TORT OR OTHERWISE, WILL IN NO EVENT EXCEED THE AMOUNT OF FEES PAID BY YOU TO XILINX HEREUNDER FOR USE OF THE DESIGN. YOU ACKNOWLEDGE THAT THE FEES, IF ANY, REFLECT THE ALLOCATION OF RISK SET FORTH IN THIS AGREEMENT AND THAT XILINX WOULD NOT MAKE AVAILABLE THE DESIGN TO YOU WITHOUT THESE LIMITATIONS OF LIABILITY.

The Design is not designed or intended for use in the development of on-line control equipment in hazardous environments requiring failsafe controls, such as in the operation of nuclear facilities, aircraft navigation or communications systems, air traffic control, life support, or weapons systems ("High-Risk Applications"). Xilinx specifically disclaims any express or implied warranties of fitness for such High-Risk Applications. You represent that use of the Design in such High-Risk Applications is fully at your risk.

© 2004–2006 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. PowerPC is a trademark of IBM, Inc. All other trademarks are the property of their respective owners.

## **Revision History**

The following table shows the revision history for this document.

| Date     | Version | Revision                                                                                                                                                                                                                                                               |

|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11/22/04 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                |

| 03/04/05 | 2.0     | Renamed title from <i>ML401 Evaluation Platform</i> user guide to <i>ML40x Evaluation Platform</i> user guide.<br>Expanded document from ML401-specific to include ML401, ML402, and ML403 platforms.<br>Added "Building the Linux BSP (PPC405 Systems Only)" section. |

| 07/05/05 | 3.0     | Renamed title from ML40x Evaluation Platform user guide to ML40x EDK ProcessorEvaluation Platform user guide.Updated the user guide for EDK 7.1 release.Revised the "Building the Linux BSP (PPC405 Systems Only)" section.                                            |

| 02/14/06 | 4.0     | Updated the user guide for EDK 8.1 release.                                                                                                                                                                                                                            |

| 05/04/06 | 4.1     | Updated "Instructions for Downloading the Design."                                                                                                                                                                                                                     |

| 06/30/06 | 5.0     | Expanded to include ML405 evaluation platform.                                                                                                                                                                                                                         |

# Table of Contents

| Schedule of Figures 7                                                            |   |

|----------------------------------------------------------------------------------|---|

| Schedule of Tables 99                                                            |   |

| Preface: About This Guide                                                        |   |

| <b>Guide Contents</b>                                                            |   |

| Additional Resources                                                             |   |

| Conventions12Typographical12Online Document13                                    |   |

| Chapter 1: Introduction to the ML40 <i>x</i> Embedded Processor Reference System | e |

| Introduction                                                                     |   |

| <b>Requirements</b>                                                              |   |

| <b>CoreConnect</b>                                                               |   |

| Reference System Information 16                                                  |   |

| Further Reading 17                                                               |   |

| Resources for EDK Users (Including New Users)                                    |   |

| Documentation Provided by Xilinx                                                 |   |

| Chapter 2: ML40 <i>x</i> Embedded Processor Reference System                     |   |

| Introduction                                                                     |   |

| Hardware                                                                         |   |

| Hardware                                             |

|------------------------------------------------------|

| Overview                                             |

| Processor Local Bus (PLB) 22                         |

| On-Chip Peripheral Bus (OPB) 23                      |

| Device Control Register (DCR) 24                     |

| Interrupts                                           |

| Clock/Reset Distribution                             |

| CPU Debug via JTAG                                   |

| Error LEDs                                           |

| IP Version and Source                                |

| Synthesis and Implementation 27                      |

| Design Flow Environment                              |

| <b>Memory Map</b> 28                                 |

| ML40x Specific Registers                             |

| ML40 <i>x</i> Board General Purpose I/O Registers    |

| ML40 <i>x</i> Control Register 1                     |

| ML40 <i>x</i> Control Register 2                     |

| ML40 $x$ Character LCD General Purpose I/O Registers |

| ML40 <i>x</i> Differential Expansion Header General Purpose I/O Registers | . 32 |

|---------------------------------------------------------------------------|------|

| ML40 <i>x</i> Single-Ended Expansion Header General Purpose I/O Registers | . 33 |

| Extending or Modifying the Design                                         | . 34 |

| Adding or Removing IP Cores                                               | . 34 |

## **Chapter 3: EDK Tutorial and Demonstration**

| Introduction                                                               |

|----------------------------------------------------------------------------|

| Instructions for Invoking the EDK tools                                    |

| Launching Xilinx Platform Studio (XPS) 36                                  |

| Instructions for Selecting Software Application                            |

| Instructions for Building and Implementing the Design                      |

| Instructions for Downloading the Design                                    |

| Download Using Parallel Cable IV or Platform Cable USB (iMPACT Program) 37 |

| Download Using the System ACE Interface                                    |

| <b>Software</b>                                                            |

| Building the Linux BSP (PPC405 Systems Only)                               |

## **Chapter 4: Introduction to Hardware Reference IP**

| Introduction                                 | 43 |

|----------------------------------------------|----|

| Hardware Reference IP Source Format and Size | 44 |

## Chapter 5: Using IPIF to Build IP

| Introduction                                               | -5 |

|------------------------------------------------------------|----|

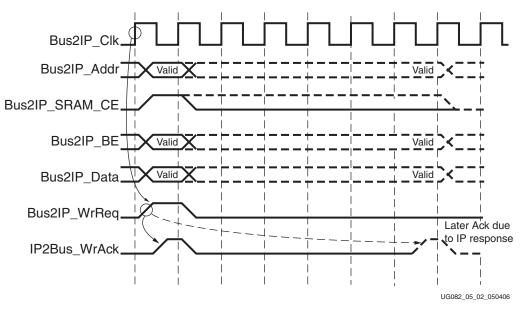

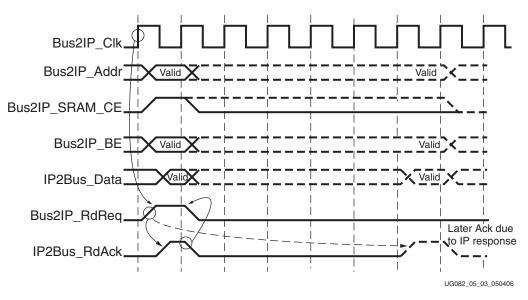

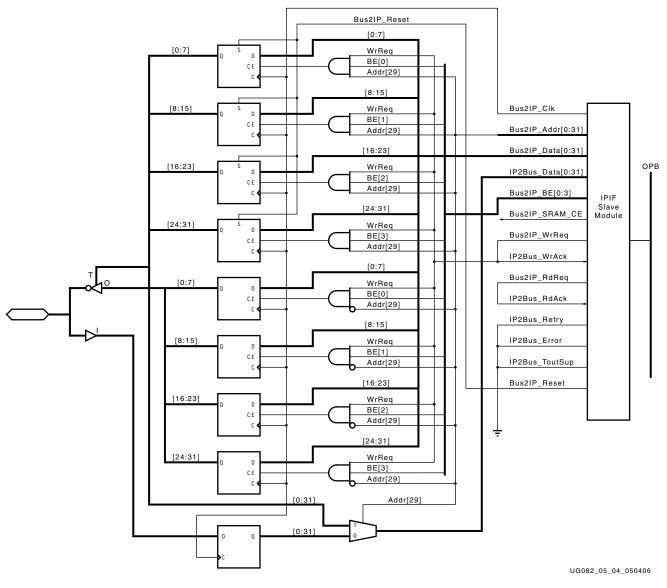

| SRAM Protocol Overview of IPIF 4                           | 6  |

| Basic Write Transactions 4                                 | 7  |

| Basic Read Transactions 4                                  | 8  |

| IPIF Status and Control Signals 4                          | 8  |

| Using IPIF to Create a GPIO Peripheral from Scratch 4      | 8  |

| Using IPIF to Connect a Pre-Existent Peripheral to the Bus | 50 |

| Conclusion                                                 | 51 |

| Conclusion                                                 | 1  |

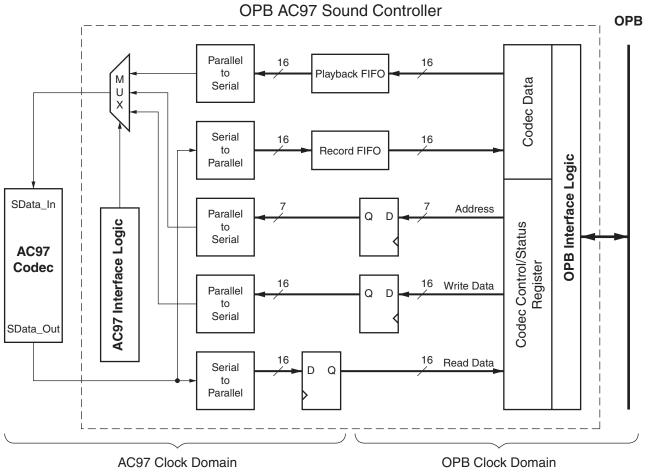

## Chapter 6: OPB AC97 Sound Controller

| Overview              | 53 |

|-----------------------|----|

| Related Documents     | 53 |

| Features              | 53 |

| Module Port Interface | 54 |

| Implementation        | 56 |

| Memory Map            | 57 |

## Chapter 7: OPB PS/2 Controller (Dual)

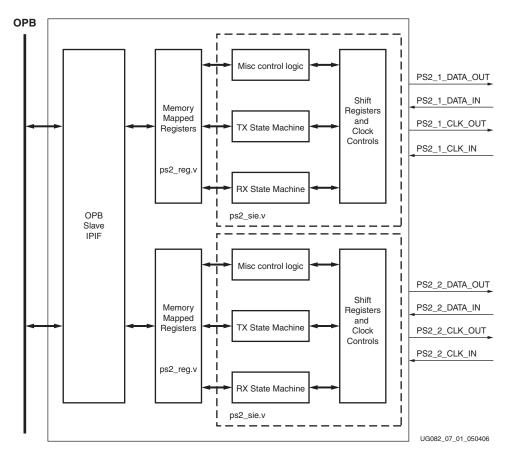

| Overview              | . 61 |

|-----------------------|------|

| Related Documents     | . 61 |

| Features              | . 61 |

| Module Port Interface | . 62 |

## **XILINX**<sup>®</sup>

| Implementation | 64 |

|----------------|----|

| Memory Map     | 65 |

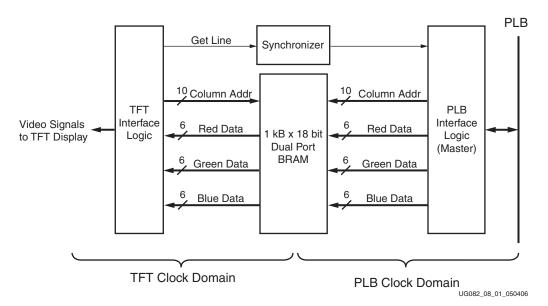

## Chapter 8: PLB TFT LCD Controller

| <b>Overview</b>                   |

|-----------------------------------|

| Related Documents                 |

| <b>Features</b>                   |

| Module Port Interface             |

| Hardware                          |

| Implementation                    |

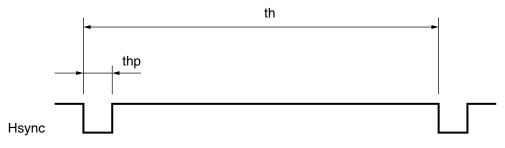

| Video Timing                      |

| Memory Map                        |

| Video Memory                      |

| Control Registers (DCR Interface) |

# Schedule of Figures

# Chapter 1: Introduction to the ML40*x* Embedded Processor Reference System

## Chapter 2: ML40x Embedded Processor Reference System

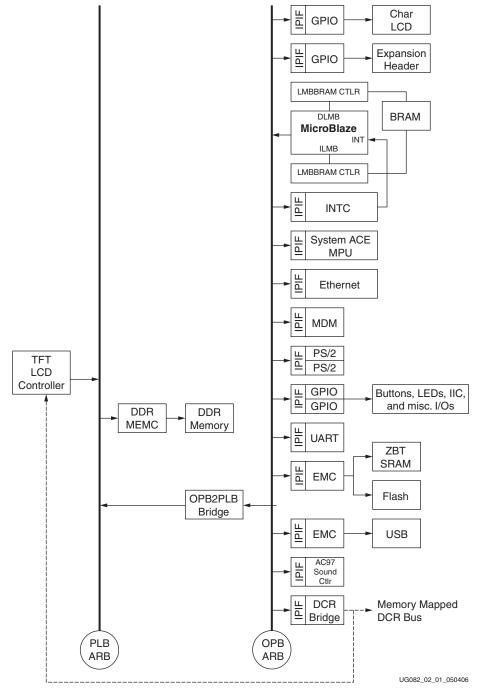

| Figure 2-1: | Hardware View of ML40 <i>x</i> Embedded MicroBlaze Reference System | 20 |

|-------------|---------------------------------------------------------------------|----|

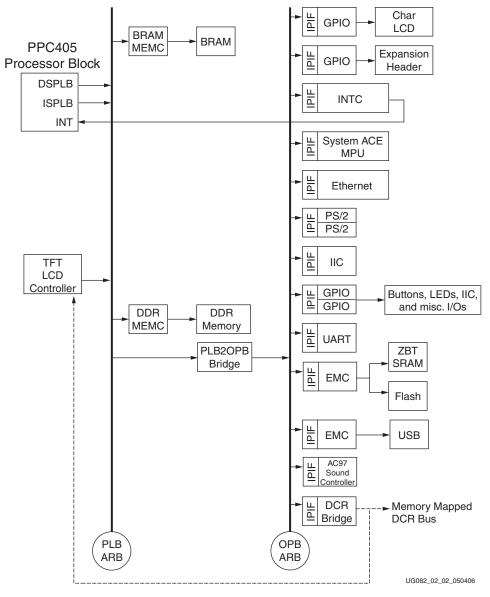

| Figure 2-2: | Hardware View of ML40 <i>x</i> Embedded PPC405 Reference System     | 21 |

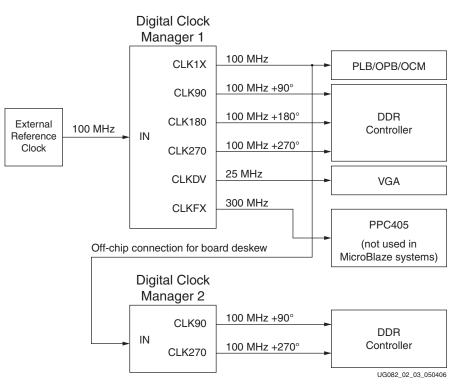

| Figure 2-3: | Clock Generation                                                    | 25 |

### Chapter 3: EDK Tutorial and Demonstration

### **Chapter 4: Introduction to Hardware Reference IP**

### Chapter 5: Using IPIF to Build IP

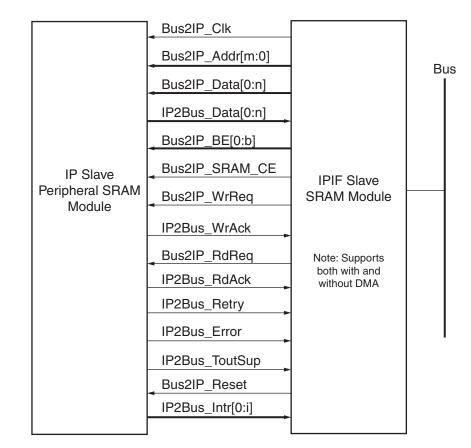

| Figure 5-1: | IPIF SRAM Module Interface               | 46 |

|-------------|------------------------------------------|----|

| Figure 5-2: | IPIF Simple SRAM Write Cycle             | 47 |

| Figure 5-3: | IPIF Simple SRAM Read Cycle              | 48 |

| Figure 5-4: | IPIF SRAM Module to GPIO Logic Interface | 49 |

## Chapter 6: OPB AC97 Sound Controller

| Figure 6-1: OPB AC97 Sound Controller Block Diagram | 56 |

|-----------------------------------------------------|----|

|                                                     |    |

## Chapter 7: OPB PS/2 Controller (Dual)

| Figure 7-1: OPB PS/2 Controller Block Diagram | 64 |

|-----------------------------------------------|----|

|-----------------------------------------------|----|

## Chapter 8: PLB TFT LCD Controller

| Figure 8-1: | High-Level Block Diagram. | 75 |

|-------------|---------------------------|----|

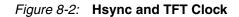

| Figure 8-2: | Hsync and TFT Clock       | 76 |

| Figure 8-3: | Horizontal Data           | 76 |

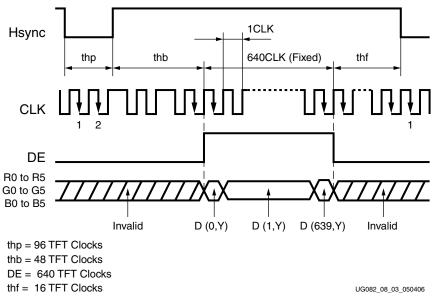

| Figure 8-4: | Vsync and h_syncs         | 77 |

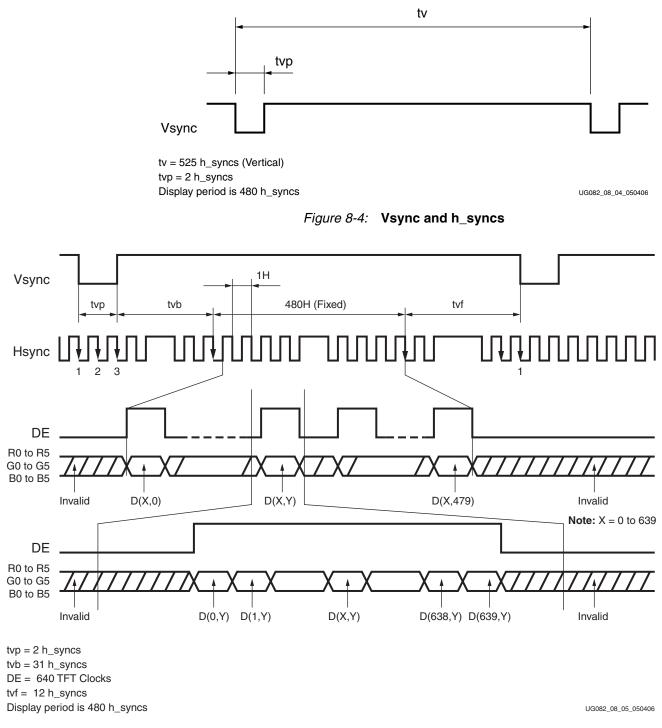

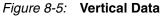

| Figure 8-5: | Vertical Data             | 77 |

## Schedule of Tables

# Chapter 1: Introduction to the ML40*x* Embedded Processor Reference System

## Chapter 2: ML40x Embedded Processor Reference System

| Table 2-1:       IP Cores in the ML40x Embedded Processor Reference System.       26             |

|--------------------------------------------------------------------------------------------------|

| Table 2-2:         Memory Maps                                                                   |

| Table 2-3:         GPIO Registers (Address 0x9000000-0x90000004)         29                      |

| Table 2-4:    Control Register 1 (Address 0x9000008).    30                                      |

| Table 2-5:    Control Register 2 (Address 0x900000C)    31                                       |

| Table 2-6:       Character LCD GPIO Registers (Address 0x90002000-0x90002004)       32           |

| Table 2-7:       Differential Expansion Header GPIO Regs (Addr 0x90001000-0x90001004)       . 32 |

| Table 2-8: Single-Ended Expansion Header GPIO Regs (Addr 0x90001008-0x9000100C) 33               |

## **Chapter 3: EDK Tutorial and Demonstration**

| Table 3-1: Demonstration Software Applications | 39 |

|------------------------------------------------|----|

|------------------------------------------------|----|

## **Chapter 4: Introduction to Hardware Reference IP**

## Chapter 5: Using IPIF to Build IP

## Chapter 6: OPB AC97 Sound Controller

| Table 6-1: | Global Signals        | 54 |

|------------|-----------------------|----|

| Table 6-2: | OPB Slave Signals     | 54 |

| Table 6-3: | External I/O Pins     | 54 |

| Table 6-4: | Generics (Parameters) | 55 |

| Table 6-5: | Memory Map            | 57 |

## Chapter 7: OPB PS/2 Controller (Dual)

| Table 7-1: OPB Slave Signa       | als $\epsilon$                | 52 |

|----------------------------------|-------------------------------|----|

| Table 7-2: External I/O Pin      | s 6                           | 52 |

| Table 7-3:    Parameters         | $\cdots$                      | 53 |

| Table 7-4: Memory Map Ta         | $ble \dots \dots \dots h ble$ | 55 |

| Table 7-5: <b>OPB PS/2 Slave</b> | Device Pin Description6       | 56 |

## Chapter 8: PLB TFT LCD Controller

| Table 8-1: Global Signals | . 71 |

|---------------------------|------|

|---------------------------|------|

| Table 8-2: PLB Ma   | ster Signals                 |

|---------------------|------------------------------|

| Table 8-3: DCR Sla  | we Signals                   |

| Table 8-4: External | Output Pins                  |

| Table 8-5: Paramet  | ers                          |

| Table 8-6: Pixel Co | lor Encoding                 |

| Table 8-7: Control  | Registers (DCR Interface) 79 |

## Preface

## About This Guide

This user guide documents the ML40x reference design.

## **Guide Contents**

This user guide contains the following chapters:

- Chapter 1, "Introduction to the ML40x Embedded Processor Reference System"

- Chapter 2, "ML40x Embedded Processor Reference System"

- Chapter 3, "EDK Tutorial and Demonstration"

- Chapter 4, "Introduction to Hardware Reference IP"

- Chapter 5, "Using IPIF to Build IP"

- Chapter 6, "OPB AC97 Sound Controller"

- Chapter 7, "OPB PS/2 Controller (Dual)"

- Chapter 8, "PLB TFT LCD Controller"

## **Additional Resources**

To find additional documentation, see the Xilinx website at:

http://www.xilinx.com/literature.

To search the Answer Database of silicon, software, and IP questions and answers, or to create a technical support WebCase, see the Xilinx website at:

http://www.xilinx.com/support.

## **Conventions**

This document uses the following conventions. An example illustrates each convention.

### **Typographical**

The following typographical conventions are used in this document:

| Convention                  | Meaning or Use                                                                                                        | Example                                                                                                  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Courier font                | Messages, prompts, and<br>program files that the system<br>displays                                                   | speed grade: - 100                                                                                       |

| Courier bold                | Literal commands that you enter in a syntactical statement                                                            | ngdbuild design_name                                                                                     |

| Helvetica bold              | Commands that you select from a menu                                                                                  | $\textbf{File} \rightarrow \textbf{Open}$                                                                |

|                             | Keyboard shortcuts                                                                                                    | Ctrl+C                                                                                                   |

|                             | Variables in a syntax statement<br>for which you must supply<br>values                                                | ngdbuild design_name                                                                                     |

| Italic font                 | References to other manuals                                                                                           | See the <i>Development System</i><br><i>Reference Guide</i> for more<br>information.                     |

|                             | Emphasis in text                                                                                                      | If a wire is drawn so that it<br>overlaps the pin of a symbol, the<br>two nets are <i>not</i> connected. |

| Square brackets []          | An optional entry or parameter.<br>However, in bus specifications,<br>such as <b>bus</b> [7:0], they are<br>required. | <b>ngdbuild</b> [option_name]<br>design_name                                                             |

| Braces { }                  | A list of items from which you must choose one or more                                                                | lowpwr ={on off}                                                                                         |

| Vertical bar                | Separates items in a list of choices                                                                                  | lowpwr ={on off}                                                                                         |

| Vertical ellipsis<br>•<br>• | Repetitive material that has been omitted                                                                             | IOB #1: Name = QOUT'<br>IOB #2: Name = CLKIN'                                                            |

| Horizontal ellipsis         | Repetitive material that has been omitted                                                                             | allow block block_name loc1<br>loc2 locn;                                                                |

## **Online Document**

| Convention            | Meaning or Use                                             | Example                                                                                                         |  |

|-----------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|

| Blue text             | Cross-reference link to a location in the current document | See the section "Additional<br>Resources" for details.<br>Refer to "Title Formats" in<br>Chapter 1 for details. |  |

| Red text              | Cross-reference link to a location in another document     | See Figure 2-5 in the Virtex-II Platform FPGA User Guide.                                                       |  |

| Blue, underlined text | Hyperlink to a website (URL)                               | Go to <u>http://www.xilinx.com</u><br>for the latest speed files.                                               |  |

The following conventions are used in this document:

## Chapter 1

## Introduction to the ML40x Embedded Processor Reference System

## Introduction

This chapter briefly describes the reference system provided for ML40*x* evaluation platforms. The ML40*x* Embedded Processor Reference System contains a combination of known working hardware and software elements that, together, create an entire system. It demonstrates a system using the Processor Local Bus (PLB), On-Chip Peripheral Bus (OPB), Device Control Register (DCR) Bus, and the PowerPC<sup>TM</sup> 405 or MicroBlaze<sup>TM</sup> processor core. The design operates under the Embedded Development Kit (EDK) suite of tools that provides a graphical tool framework for designing embedded hardware and software. The reference system is intended to familiarize users with the Virtex<sup>TM</sup>-4 product, its design tool flows, and its features. It provides a foundation for those who are learning how to use embedded processors in Virtex-4 FPGAs.

This document covers MicroBlaze based systems for ML401, ML402, ML403 boards in addition to PowerPC 405 based systems for the ML403 and ML405 boards.

## **Requirements**

The following hardware and software are required in order to use the ML40*x* Embedded Processor Reference System.

- Operating System Requirements:

- Windows XP Professional or Linux

- Note: A PC is required for FPGA download and debug via Xilinx download cables.

- Hardware Requirements:

- Xilinx ML401, ML402, ML403, or ML405 evaluation platform

- Software Requirements:

- Embedded Development Kit (EDK) 8.1

- · Service Pack 1 for ML401, ML402, ML403

- Service Pack 2 for ML405

- ♦ ISE 8.1i

- Service Pack 2 for ML01, ML402, ML403

- Service Pack 3 for ML405

For new EDK users, the ML40*x* Embedded Processor Reference System provides an excellent example of how the EDK tools can be used to design a full featured embedded system consisting of hardware and software. The reference system also illustrates how to debug designs under EDK.

References to additional information about learning to use EDK is available in "Further Reading," page 17.

## CoreConnect

Download and installation of the IBM CoreConnect Toolkit can be useful for hardware and systems. The CoreConnect Toolkit is only available to CoreConnect licensees. Xilinx has simplified the process of becoming a CoreConnect licensee through Web-based registration available at <a href="http://www.xilinx.com/coreconnect">http://www.xilinx.com/coreconnect</a>. CoreConnect licensees are entitled to full access to the CoreConnect Toolkit including powerful bus functional modeling, bus monitoring tools, and periodic updates. To get the most out of the Embedded Development Kit, Xilinx recommends the use of the IBM CoreConnect Toolkit.

## **Reference System Information**

This section is an overview of the features of the ML40*x* Embedded Processor Reference System. Although the information contained in the reference system chapter is not exhaustive, it covers the basic requirements to effectively use the MicroBlaze or PowerPC processor. Chapter 2, "ML40*x* Embedded Processor Reference System" and Chapter 3, "EDK Tutorial and Demonstration" have instructions on how to synthesize and run the designs through the Xilinx Implementation Tools (ISE) for the Virtex-4 family.

The reference system chapters contain sections about:

- Hardware used in the system

- HDL file organization

- Synthesis and implementation

- Software applications that interoperate with the system

- Instructions to run the software applications

The ML40*x* Embedded Processor Reference System is an example of a completely embedded computer. It provides a wide variety of memory interfaces on three differing buses, as well as various peripherals such as memory controllers, general purpose I/O (GPIO), and UARTs. The example software provided with this reference system is designed to demonstrate the system running a stand-alone application.

The Embedded Processor Reference System provides additional study of the PLB, OPB, and DCR buses. In addition, it affords the opportunity to see how OPB-based devices are used in a system. Step-by-step instructions are provided to help the user through the design flow and to target a Virtex-4 device. Users can modify the ML40*x* Embedded Processor Reference System to add and subtract peripherals, as well as to change the software for their own custom-designed systems. These designs can be synthesized and run through place-and-route to produce a bitstream for Virtex-4 devices.

*Note:* The README file in the EDK project directory of the reference design contains important release notes and information about the design.

## **Further Reading**

Xilinx provides a wealth of valuable information to assist you in your design efforts. Some of the relevant documentation is listed below with more information available through the Xilinx Support website at <u>http://www.xilinx.com/support</u>. To obtain the most recent revision of documentation related to the ML40*x* board, see the corresponding Web page:

- ML401: <u>http://www.xilinx.com/ml401</u>

- ML402: <u>http://www.xilinx.com/ml402</u>

- ML403: <u>http://www.xilinx.com/ml403</u>

- ML405: <u>http://www.xilinx.com/ml405</u>

#### Resources for EDK Users (Including New Users)

EDK Main Web Page http://www.xilinx.com/ise/embedded/edk.htm

Getting Started with the EDK http://www.xilinx.com/ise/embedded/edk\_getstarted.pdf

Embedded System Tools Guide http://www.xilinx.com/ise/embedded/est\_guide.pdf

EDK Tutorials and Design Examples http://www.xilinx.com/ise/embedded/edk\_examples.htm

Embedded Processor Discussion Forum http://toolbox.xilinx.com/cgi-bin/forum?14@@/Embedded%20Processors

#### **Documentation Provided by Xilinx**

Virtex-4 Data Sheet: DC and Switching Characteristics http://www.xilinx.com/bvdocs/publications/ds302.pdf

Virtex-4 User Guide http://www.xilinx.com/bvdocs/userguides/ug070.pdf

#### **IBM CoreConnect Documentation**

The Embedded Development Kit integrates with the IBM CoreConnect Toolkit. The toolkit provides a number of features, enhancing design productivity and allowing you to get the most from the EDK. To obtain the toolkit, you must be a licensee of the IBM CoreConnect Bus Architecture. Licensing CoreConnect provides access to a wealth of documentation, Bus Functional Models, Hardware IP, and the toolkit.

Xilinx provides a Web-based licensing mechanism that allows you to obtain the CoreConnect toolkit from our website. To license CoreConnect, use an Internet browser to access <a href="http://www.xilinx.com/ipcenter/processor\_central/register\_coreconnect.htm">http://www.xilinx.com/ipcenter/processor\_central/register\_coreconnect.htm</a>. After your request has been approved (typically within 24 hours), you will receive an e-mail granting access to a protected website. You can then download the toolkit. If you prefer, you can also license CoreConnect directly from IBM.

If you would like further information on CoreConnect Bus Architecture, see IBM's CoreConnect website at <u>http://www.ibm.com/chips/products/coreconnect</u>.

## Chapter 2

## ML40x Embedded Processor Reference System

## Introduction

The ML40*x* Embedded Processor Reference System is an example of a large Virtex-4 based system. An IBM Core Connect infrastructure connects the CPU to numerous peripherals using Processor Local Bus (PLB), On-Chip Peripheral Bus (OPB), and Device Control Register (DCR) buses to build a complete system. This document describes the contents of the reference system and provides information about how the system is organized and implemented. A complete design cycle incorporating synthesis, FPGA implementation, and download is described. The information introduces many aspects of the ML40*x* Embedded Processor Reference System, but the user should refer to additional specific documentation for more detailed information about the software, tools, peripherals, interface protocols, and capabilities of the FPGA.

### Hardware

#### Overview

Figure 2-1, page 20 provides a high-level view of the hardware contents of the Embedded MicroBlaze Processor System. Figure 2-2, page 21 provides an overview of the PPC405-based system for ML403. These designs demonstrate a system that uses PLB, OPB, and DCR devices. The PLB protocol generally supports higher bandwidths, so the high-bandwidth devices are placed there. The OPB connects the lower-performance peripheral devices to the CPU. The OPB offers a less complex protocol relative to the PLB, making it easier to design peripherals that do not require the highest performance. The OPB also has the advantage that it can support a greater number of devices. DCR is used with control and status registers for simplicity when performance is not important. Refer to the PLB, OPB, and DCR CoreConnect Architecture Specifications for more information. The hardware devices used in this design are described in more detail in the *Processor IP Reference Guide* (see <*EDK Install Directory*>/doc/proc\_ip\_ref\_guide.pdf) and in Chapter 4, "Introduction to Hardware Reference IP."

Figure 2-1: Hardware View of ML40x Embedded MicroBlaze Reference System

Figure 2-2: Hardware View of ML40x Embedded PPC405 Reference System

### Processor Local Bus (PLB)

The PLB connects the CPU to high-performance devices, such as memory controllers. The PLB protocol supports higher bandwidth transactions and has a feature set better than OPB/DCR. PLB supports memory operations OPB/DCR. Highlights of the PLB protocol include synchronous architecture, independent read/write data paths, and split transaction address/data buses. The reference design includes a 64-bit PLB infrastructure with 64-bit master and slave devices attached.

The PLB devices in the reference system include:

- PLB Masters

- ◆ 640x480 VGA Controller

- OPB-to-PLB Bridge (MicroBlaze system)

- PPC405 Instruction-Side PLB Interface (PPC405 system)

- PPC405 Data-Side PLB Interface (PPC405 system)

- PLB Slaves

- Double Data Rate (DDR) SDRAM Controller

- BRAM Controller (PPC405 systems)

- PLB-to-OPB Bridge (PPC405 system)

- PLB Arbiter

- 64-bit Xilinx PLB Arbiter

In general, all PLB devices are optimized around the FPGA architecture and use pipelining to improve maximum clock frequencies and reduce logic utilization. Refer to the documentation accompanying each device for more information about its design.

## **On-Chip Peripheral Bus (OPB)**

The OPB connects lower-performance peripheral devices to the system. The OPB has a less complex architecture, simplifying peripheral development. OPB and PLB devices can communicate by way of an OPB-to-PLB Bridge or an PLB-to-OPB Bridge.

The OPB devices in the reference system include:

- OPB Masters

- Ethernet Controller (DMA Engine, if enabled)

- MicroBlaze Processor Instruction-Side Interface (MicroBlaze system)

- MicroBlaze Processor Data-Side Interface (MicroBlaze system)

- PLB-to-OPB Bridge (PPC405 system)

- OPB Slaves

- IIC Controller (PPC405 system)

- General-Purpose Input/Output (GPIO) x3

- ◆ 16450 UART

- Interrupt Controller

- External Memory Controller x2

- Microprocessor Debug Module (MicroBlaze system)

- AC97 Sound Controller

- OPB-to-DCR Bridge

- Ethernet Controller

- Dual PS/2 Controller

- ◆ System ACE<sup>™</sup> MPU Interface

- OPB-to-PLB Bridge-In (MicroBlaze system)

- OPB Arbiter

In general, all OPB devices are optimized around the FPGA architecture and make use of pipelining to improve maximum clock frequencies and reduce logic utilization. Refer to the accompanying documentation for each device for more information about its design.

The OPB devices in the reference design make use of Intellectual Property InterFace (IPIF) modules to further simplify IP development. The IPIF converts the OPB protocol into common interfaces, such as an SRAM protocol or a control register interface. IPIF modules also provide support for DMA and interrupt functionality. IPIF modules simplify software development because the IPIF framework has many common features. Refer to Chapter 5, "Using IPIF to Build IP" for more information.

The IPIF is designed mainly to support a wide variety of common interfaces, but might not be the optimal solution in all cases. Where additional performance or functionality is required, the user can develop a custom OPB interface. The IPIF protocols can also be extended to support other bus standards, such as PLB. This allows the backend interface to the IP to remain the same while the bus interface logic in the IPIF is changed. This provides an efficient means for supporting different bus standards with the same IP device.

The OPB specification supports masters and slaves of up to 64 bits with a *dynamic bus sizing* capability that allows OPB masters and slaves of different sizes to communicate with each other. The ML40*x* Embedded Processor Reference System uses a subset of the OPB specification that supports only 32-bit byte enable masters and slaves. Legacy devices utilizing 8- or 16-bit interfaces or those that require dynamic bus sizing functionality are not directly supported. It is recommended that all new OPB peripherals support byte-enable operations for better performance and reduced logic utilization.

## Device Control Register (DCR)

The DCR bus offers a very simple interface protocol and is used for accessing control and status registers in various devices. It allows for register access to various devices without overloading the OPB and PLB interfaces. Because DCR devices are generally accessed infrequently and do not have high-performance requirements, they are used throughout the reference design for functions, such as error status registers, interrupt controllers, and device initialization logic.

An OPB-to-DCR Bridge is instantiated to locate the 4-KB DCR space within the general system memory space. The DCR slave devices connected to the OPB-to-DCR Bridge include:

- PLB Arbiter (if enabled)

- VGA TFT LCD Controller

The DCR specification requires that the DCR master and slave clocks be synchronous to each other and related in frequency by an integer multiple. It is important to be aware of the clock domains of each of the DCR devices to ensure proper functionality.

#### Interrupts

An interrupt controller for interrupts is controlled through the OPB. It allows multiple edge or level sensitive interrupts from peripherals to be OR'ed together back to the CPU. The ability for bitwise masking of individual interrupts is also provided. The connections from the IP to the interrupt controller are:

- UART

- Microprocessor debug module (MicroBlaze system)

- Ethernet controller

- PS/2 Port #1

- PS/2 Port #2

- External USB chip

- System ACE MPU

- AC97 sound controller (play buffer)

- AC97 sound controller (record buffer)

- Ethernet PHY

- IIC controller (PPC405 system)

#### **Clock/Reset Distribution**

Virtex-4 FPGAs have abundant clock management and global clock buffer resources. To demonstrate some of these capabilities, the ML40*x* Embedded Processor Reference System uses a variety of different clocks. Figure 2-3, page 25 illustrates use of the digital clock managers (DCMs) for generating the main clocks in the design. A 100-MHz input reference clock is used to generate the main 100-MHz PLB, OPB, and DCR clocks. The CLK90/180/270 output of the DCM produces a 100-MHz clock that is phase shifted by 90/180/270 degrees for use by the DDR SDRAM controller. The CLKFX output of the DCM produces a 300-MHz processor clock for PPC405 designs. The main 100-MHz clock is divided by four to create a 25-MHz VGA clock. A second DCM is used to recover and deskew the external clock from the DDR SDRAM. A third DCM (not shown) is used to deskew the externally driven SRAM clock with the internal 100-MHz clock.

Because each clock is referenced from the same 100-MHz clock, they are all phase aligned to each other. This synchronous phase alignment is required by the CPU and many other devices so they can pass signals from one clock domain to another.

Figure 2-3: Clock Generation

After a system reset or at FPGA startup, a debounce circuit inside the Processor System Reset IP Module holds the FPGA in reset until the DCM has locked onto its reference clock. Once the DCM is locked and the clocks remain stable for several cycles, the reset condition is released to allow the system logic to begin operating. For example, the CPU begins fetching instructions a few cycles after reset is released. Because the reset net is a highfanout signal, it might not be able to reach all the logic in the design within one clock cycle. User IP blocks should be designed to take into account the possible skew in the global reset and still start up properly. Alternatively, the global reset can be registered locally in each IP block to generate a synchronous reset signal.

#### CPU Debug via JTAG

The CPU in the ML40*x* Embedded Processor Reference System can be debugged via JTAG using the EDK tools.

The preferred method of communicating with the CPU via JTAG is to combine the CPU JTAG chain with the FPGA's main JTAG chain, which is also used to download bitstreams. For MicroBlaze designs, this method requires the user to instantiate an OPB MDM component and directly connect it to the CPU in the user's design. For PPC405 designs, a JTAGPPC component must be instantiated and connected to the PPC405 processor. The primary advantage of sharing the same JTAG chain for CPU debug and FPGA programming is that this simplifies the number of cables needed; a single JTAG cable (like the Xilinx Parallel Cable IV cable) can be used for bitstream download as well as CPU software debugging.

#### Error LEDs

The design contains two\* error LED outputs to signal OPB (Error 1) and PLB (Error 2) errors. OPB errors (Error 1 LED on the ML40*x* board) signal an OPB timeout or OPB error acknowledge condition. PLB errors (Error 2 LED on the ML40*x* board) signal a PLB timeout or data error acknowledge condition as reported by the PLB arbiter. Control registers in the design allow the error conditions to be cleared. See "ML40*x* Control Register 2," page 31 for more information.

*Note:* \*On the ML403 and ML405 boards, only the Error 1 LED is present. It signals both PLB and OPB error conditions.

#### **IP Version and Source**

Table 2-1 (which spans multiple pages) summarizes the list of IP cores making up the ML40*x* Embedded Processor Reference System. The table shows the hardware version number of each IP core used in the design. The table also lists whether the source of the IP is from the EDK installation or whether it is reference IP in the local **pcores** directory.

| Hardware IP                               | Version | Source                                       |

|-------------------------------------------|---------|----------------------------------------------|

| bram_block                                | 1.00.a  | EDK Installation                             |

| dcm_module                                | 1.00.a  | EDK Installation                             |

| dcr_v29                                   | 1.00.a  | EDK Installation                             |

| jtagppc_cntlr<br>(PPC405 systems)         | 2.00.a  | EDK Installation                             |

| lmb_bram_if_cntlr<br>(MicroBlaze systems) | 1.00.b  | Local <b>pcores</b> Directory <sup>(1)</sup> |

| lmb_v10<br>(MicroBlaze systems)           | 1.00.a  | EDK Installation                             |

| microblaze                                | 4.00.a  | EDK Installation                             |

| misc_logic                                | 1.00.a  | Local <b>pcores</b> Directory                |

| opb_ac97_controller_ref                   | 1.00.a  | Local <b>pcores</b> Directory                |

| opb_emc                                   | 2.00.a  | EDK Installation                             |

Table 2-1: IP Cores in the ML40x Embedded Processor Reference System

| Hardware IP                            | Version                                | Source                                                           |

|----------------------------------------|----------------------------------------|------------------------------------------------------------------|

| opb_ethernet                           | 1.02.a                                 | EDK Installation                                                 |

| opb_gpio                               | 3.01.b                                 | EDK Installation                                                 |

| opb_iic (PPC405 systems)               | 1.01.d                                 | EDK Installation                                                 |

| opb_intc                               | 1.00.c                                 | EDK Installation                                                 |

| opb_mdm<br>(MicroBlaze systems)        | 2.01.a (ML401)<br>2.00.a (ML402/ML403) | Local <b>pcores</b> Directory <sup>(2)</sup><br>EDK Installation |

| opb_ps2_dual_ref                       | 1.00.a                                 | Local <b>pcores</b> Directory                                    |

| opb_sysace                             | 1.00.c                                 | EDK Installation                                                 |

| opb_uart16550                          | 1.00.d                                 | EDK Installation                                                 |

| opb_v20                                | 1.10.c                                 | EDK Installation                                                 |

| opb2dcr_bridge                         | 1.00.b                                 | EDK Installation                                                 |

| opb2plb_bridge<br>(MicroBlaze systems) | 1.00.c                                 | EDK Installation                                                 |

| plb_bram_if_cntlr<br>(PPC405 systems)  | 1.00.b                                 | EDK Installation                                                 |

| plb_ddr                                | 1.11.a                                 | EDK Installation                                                 |

| plb_tft_cntlr_ref                      | 1.00.c                                 | Local <b>pcores</b> Directory                                    |

| plb_v34                                | 1.02.a                                 | EDK Installation                                                 |

| plb2opb_bridge<br>(PPC405 systems)     | 1.01.a                                 | EDK Installation                                                 |

| ppc405_virtex4<br>(PPC405 systems)     | 1.00.a                                 | EDK Installation                                                 |

| proc_sys_reset                         | 1.00.a                                 | EDK Installation                                                 |

Table 2-1: IP Cores in the ML40x Embedded Processor Reference System

#### Notes:

1. Modified to reduce power consumption.

2. Modified to use alternate boundary scan (BSCAN) primitive required for early Virtex-4 engineering sample (ES) devices.

## Synthesis and Implementation

The ML40*x* Embedded Processor Reference System can be synthesized and placed/routed into a Virtex-4 FPGA under the EDK tools. A basic set of timing constraints for the design is provided to allow the design to go through place-and-route.

## **Design Flow Environment**

The EDK provides an environment to help manage the design flow for the ML40*x* Embedded Processor Reference System including synthesis, implementation, and software compilation. EDK offers a GUI or command line interface to run these tools as part of the design flow. Consult the EDK documentation for more information.

## **Memory Map**

This section diagrams the system memory map for the ML40*x* Embedded Processor Reference System. It also documents the location of the DCR devices as mapped by the OPB to DCR Bridge. The memory map shown in Table 2-2 reflects the default location of the system devices as defined in the **system.mhs** file.

#### Table 2-2: Memory Maps

|                              | · · ·     | (MicroBlaze)<br>Address |        |                                                                                                                            | 1                    |

|------------------------------|-----------|-------------------------|--------|----------------------------------------------------------------------------------------------------------------------------|----------------------|

| Device                       | Max       | Min                     | Size   | Comment                                                                                                                    |                      |

| DDR SDRAM                    |           | 10000000                |        |                                                                                                                            | 1)                   |

| DDR SDRAM Shadow Memory      |           | 14000000                | -      | Shadow memory allows video memory to be accessed as an uncached                                                            |                      |

| PLB Device Memory Ma         |           |                         |        | region. Shadow Memory contains three copies of DDR memory.                                                                 | J                    |

| 22 Dovido moniory ma         |           | dress                   |        |                                                                                                                            | 1                    |

| Device                       | Max       | Min                     | Size   | Comment                                                                                                                    |                      |

| DDR SDRAM                    | 03FFFFFF  | 00000000                | 64 MB  |                                                                                                                            |                      |

| DDR SDRAM Shadow Memory      | OFFFFFF   | 0400000                 | 192 MB | Shadow memory allows video memory to be accessed as an uncached region. Shadow Memory contains three copies of DDR memory. |                      |

|                              | 3FFFFFFF  | 20000000                | 256 MB | PPC405 systems only                                                                                                        |                      |

| PLB to OPB Bridge            | 7FFFFFFF  | 60000000                | 256 MB | PPC405 systems only                                                                                                        | ]                    |

|                              | DFFFFFFF  | 80000000                | 768 MB | PPC405 systems only                                                                                                        |                      |

| BRAM                         | FFFFFFFF  | FFFF0000                | 64 KB  |                                                                                                                            |                      |

| OPB Device Memory Ma         | •         |                         |        | Г                                                                                                                          | -                    |

| <b>.</b> .                   |           | dress                   |        |                                                                                                                            |                      |

| Device                       | Max       | Min                     | Size   | Comment                                                                                                                    | -                    |

| LMB BRAM                     | 0000FFFF  | 00000000                | 64 KB  | MicroBlaze systems only                                                                                                    | , ,                  |

| OPB to PLB Bridge            | 1FFFFFFF  | 10000000                | 256 MB | MicroBlaze systems only                                                                                                    | }~                   |

| OPB EMC (ZBT SRAM)           | 200FFFFF  | 20000000                | 1 MB   |                                                                                                                            |                      |

| OPB EMC (Flash)              | 287FFFFF  | 28000000                | 8 MB   |                                                                                                                            |                      |

| Ethernet                     | 60003FFF  | 60000000                | 16 KB  |                                                                                                                            |                      |

| Dual GPIO                    | 900001FF  | 90000000                | 512 B  |                                                                                                                            |                      |

| Dual GPIO (Expansion Header) | 900011FF  | 90001000                | 512 B  |                                                                                                                            |                      |

| GPIO (Character LCD)         | 900021FF  | 90002000                | 512 B  |                                                                                                                            |                      |

| UART1                        | A0001FFF  | A0000000                | 8 KB   |                                                                                                                            | ]                    |

| OPB EMC (USB)                | A50000FF  | A5000000                | 256 B  |                                                                                                                            | ]                    |

| AC97 Sound                   | A60000FF  | A6000000                | 256 B  |                                                                                                                            | ]                    |

| IIC Controller               | A80001FF  | A8000000                | 512 B  | PPC405 systems only                                                                                                        |                      |

| PS/2 (Dual)                  | A9001FFF  | A9000000                | 8 KB   |                                                                                                                            |                      |

| System ACE MPU               | CF0001FF  | CF000000                | 512 B  |                                                                                                                            | ].                   |

| OPB to DCR Bridge            | D0000FFF  | D0000000                | 4 KB   | mem addr = DCR addr x 4                                                                                                    | $] \} - $            |

| OPB INTC                     | D1000FDF  | D1000FC0                | 32 B   |                                                                                                                            |                      |

| OPB MDM                      |           | FFFE8000                | 256 B  | MicroBlaze systems only                                                                                                    |                      |

| lemory-Mapped DCR D          |           |                         |        |                                                                                                                            | - <b>-</b>           |

|                              | A .I      | dress                   | 1      | Commont                                                                                                                    |                      |

| Device                       | Ad<br>Max | Min                     | Size   | Comment<br>(DCR Addr Range)                                                                                                | OPB to DCR<br>Bridge |

UG082\_02\_04\_050406

## ML40x Specific Registers

The design also contains a number of register bits to control various items on the ML40*x* such as the buttons and LEDs. See the EDK *Processor IP Reference Guide* at (*<EDK Install Directory*>/doc/proc\_ip\_ref\_guide.pdf) for more information about the GPIO. Table 2-3 through Table 2-8 contain information about control and status registers specific to the ML40*x* Embedded Processor Reference System.

## ML40x Board General Purpose I/O Registers

Table 2-3 (which spans to the next page) shows the standard set of GPIO data/direction registers at address 0x9000000-0x90000004.

| Bit(s)  | Description                                     |

|---------|-------------------------------------------------|

| 0 (LSB) | General Purpose LED 0                           |

| 1       | General Purpose LED 1                           |

| 2       | General Purpose LED 2                           |

| 3       | General Purpose LED 3                           |

| 4       | Center Directional LED                          |

| 5       | West Directional LED                            |

| 6       | South Directional LED                           |

| 7       | East Directional LED                            |

| 8       | North Directional LED                           |

| 9       | Center Directional Button                       |

| 10      | West Directional Button                         |

| 11      | South Directional Button                        |

| 12      | East Directional Button                         |

| 13      | North Directional Button                        |

| 14      | General Purpose DIP Switch 1 (ML401/ML402 only) |

| 15      | General Purpose DIP Switch 2 (ML401/ML402 only) |

| 16      | General Purpose DIP Switch 3 (ML401/ML402 only) |

| 17      | General Purpose DIP Switch 4 (ML401/ML402 only) |

| 18      | General Purpose DIP Switch 5 (ML401/ML402 only) |

| 19      | General Purpose DIP Switch 6 (ML401/ML402 only) |

| 20      | General Purpose DIP Switch 7 (ML401/ML402 only) |

| 21      | General Purpose DIP Switch 8 (ML401/ML402 only) |

| 22      | SMA "Input N" (ML401/ML403/ML405 only)          |

| 23      | SMA "Input P"(ML401/ML403/ML405 only)           |

| 24      | SMA "Output N"(ML401/ML403/ML405 only)          |

Table 2-3: GPIO Registers (Address 0x9000000-0x90000004)

| Bit(s)      | Description                            |  |  |

|-------------|----------------------------------------|--|--|

| 25          | SMA "Output P"(ML401/ML403/ML405 only) |  |  |

| 26          | User Clock (ML401/ML403/ML405 only)    |  |  |

| 27          | IIC Bus Select 0 (ML405 only)          |  |  |

| 28          | IIC Bus Select 1 (ML405 only)          |  |  |

| 31-29 (MSB) | Reserved                               |  |  |

Table 2-3: GPIO Registers (Address 0x9000000-0x90000004) (Continued)

Note: A 1 value indicates a button was pushed or turns ON an LED.

#### ML40x Control Register 1

Table 2-4 shows Control Register 1 located at address 0x90000008.

Table 2-4:

Control Register 1 (Address 0x9000008)

| Bit(s)      | Description                                                                                                                                                                                                                                                                                                     |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 (LSB)     | IIC SCL. Valid only when IIC GPIO is enabled (see "ML40x Control Register 2," Bit 6). Reading this bit reads the value from the external pin. Writing this bit sets the value of the external pin if the corresponding direction bit is set to a "write" (see "ML40x Control Register 2," Bit 0).               |

| 1           | IIC SDA. Valid only when IIC GPIO is enabled (see "ML40x Control Register 2,"<br>Bit 6). Reading this bit reads the value from the external pin. Writing this bit sets the<br>value of the external pin if the corresponding direction bit is set to a "write" (see<br>"ML40x Control Register 2," Bit 1).      |

| 7-2         | Reserved.                                                                                                                                                                                                                                                                                                       |

| 8           | PS/2 Mouse Clock. Valid only when PS/2 GPIO is enabled (see "ML40x Control Register 2," Bit 7). Reading this bit reads the value from the external pin. Writing this bit sets the value of the external pin if the corresponding direction bit is set to a "write" (see "ML40x Control Register 2," Bit 8).     |

| 9           | PS/2 Mouse Data. Valid only when PS/2 GPIO is enabled (see "ML40x Control Register 2," Bit 7). Reading this bit reads the value from the external pin. Writing this bit sets the value of the external pin if the corresponding direction bit is set to a "write" (see "ML40x Control Register 2," Bit 9).      |

| 10          | PS/2 Keyboard Clock. Valid only when PS/2 GPIO is enabled (see "ML40x Control Register 2," Bit 7). Reading this bit reads the value from the external pin. Writing this bit sets the value of the external pin if the corresponding direction bit is set to a "write" (see "ML40x Control Register 2," Bit 10). |

| 11          | PS/2 Keyboard Data. Valid only when PS/2 GPIO is enabled (see "ML40x Control Register 2," Bit 7). Reading this bit reads the value from the external pin. Writing this bit sets the value of the external pin if the corresponding direction bit is set to a "write" (see "ML40x Control Register 2," Bit 11).  |

| 12          | CPU Reset Button. Valid only when CPU Reset GPIO is enabled (see "ML40x<br>Control Register 2," Bit 12). Reading this bit reads the value from the external pin.<br>A "1" value indicates the CPU reset button was pushed.                                                                                      |

| 31-13 (MSB) | Reserved.                                                                                                                                                                                                                                                                                                       |

WWW.BDT Willicom/XILION Processor Reference Design UG082 (v5.0) June 30, 2006

## ML40x Control Register 2

Table 2-5 shows Control Register 2 located at address 0x9000000C.

Table 2-5: Control Register 2 (Address 0x9000000C)

| Bit(s)      | Description                                                                                                                                                                                                                                                                                              |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 (LSB)     | IIC SCL I/O Direction. Valid only when IIC GPIO is enabled (see "ML40x Control Register 2," Bit 6). Setting this bit to a 1 makes the GPIO IIC SCL bit a read input. Setting this bit to 0 makes the GPIO IIC SCL bit a write output.                                                                    |

| 1           | IIC SDA I/O Direction. Valid only when IIC GPIO is enabled (see "ML40x Control Register 2," Bit 6). Setting this bit to a 1 makes the GPIO IIC SDA bit a read input. Setting this bit to 0 makes the GPIO IIC SDA bit a write output.                                                                    |

| 2           | Error 1 LED Reset. Writing a 1 to this bit holds the Error 1 LED off. This bit must be written back to a 0 to permit normal operation.                                                                                                                                                                   |

| 3           | Error 1 LED Set. Writing a 1 to this bit holds the Error 1 LED on. This bit must be written back to a 0 to permit normal operation.                                                                                                                                                                      |

| 4           | Error 2 LED Reset. Writing a 1 to this bit holds the Error 2 LED off. This bit must be written back to a 0 to permit normal operation. (ML401/ML402 only)                                                                                                                                                |

| 5           | Error 2 LED Set. Writing a 1 to this bit holds the Error 2 LED on. This bit must be written back to a 0 to permit normal operation. (ML401/ML402 only)                                                                                                                                                   |

| 6           | IIC GPIO. Writing this bit to a 1 makes the IIC SCL/SDA pins controlled via GPIO registers. Writing this bit to a 0 makes IIC SCL/SDA pins controlled by the OPB IIC Controller (if instantiated in system.mhs).                                                                                         |

| 7           | IIC PS/2. Writing this bit to a 1 makes the PS/2 mouse/keyboard pins controlled via GPIO registers. Writing this bit to a 0 makes the PS/2 pins controlled by the OPB Dual PS/2 Controller.                                                                                                              |

| 8           | PS/2 Mouse Clock I/O Direction. Valid only when PS/2 GPIO is enabled (see "ML40x Control Register 2," Bit 7). Setting this bit to a 1 makes the PS/2 Mouse Clock bit a read input. Setting this bit to 0 makes the bit a write output.                                                                   |

| 9           | PS/2 Mouse Data I/O Direction. Valid only when PS/2 GPIO is enabled (see "ML40x Control Register 2,", Bit 7). Setting this bit to a 1 makes the PS/2 Mouse Data bit a read input. Setting this bit to 0 makes the bit a write output.                                                                    |

| 10          | PS/2 Keyboard Clock I/O Direction. Valid only when PS/2 GPIO is enabled (see "ML40x Control Register 2," Bit 7). Setting this bit to a 1 makes the PS/2 Keyboard Clock bit a read input. Setting this bit to 0 makes the bit a write output.                                                             |

| 11          | PS/2 Keyboard Data I/O Direction. Valid only when PS/2 GPIO is enabled (see "ML40x Control Register 2," Bit 7). Setting this bit to a 1 makes the PS/2 Keyboard Data bit a read input. Setting this bit to 0 makes the bit a write output.                                                               |

| 12          | CPU Reset GPIO. Writing this bit to a 1 makes the state of the CPU Reset button readable using ML40 <i>x</i> Control Register 1, Bit 12. Setting this bit to a 1 prevents the CPU Reset button from causing a system reset. This bit must be set back to 0 for normal operation of the CPU Reset button. |

| 13          | USB Reset. Setting this bit to a 1 resets the USB controller chip. This bit must be set back to 0 to permit normal operation of the USB controller.                                                                                                                                                      |

| 31-14 (MSB) | Reserved.                                                                                                                                                                                                                                                                                                |

### ML40*x* Character LCD General Purpose I/O Registers

Table 2-6 shows the character LCD registers, which are a standard set of GPIOdata/direction registers at address 0x90002000-0x90002004.

#### Table 2-6: Character LCD GPIO Registers (Address 0x90002000-0x90002004)

| Bit(s)     | Description             |

|------------|-------------------------|

| 0 (LSB)    | Character LCD Pin "DB4" |

| 1          | Character LCD Pin "DB5" |

| 2          | Character LCD Pin "DB6" |

| 3          | Character LCD Pin "DB7" |

| 4          | Character LCD Pin "RW"  |

| 5          | Character LCD Pin "RS"  |

| 6          | Character LCD Pin "E"   |

| 31-7 (MSB) | Reserved                |

#### ML40x Differential Expansion Header General Purpose I/O Registers

Table 2-7 shows the differential expansion header registers, which are a standard set of GPIO data/direction registers at address 0x90001000-0x90001004.

| Bit   | Description            | Bit   | Description            |

|-------|------------------------|-------|------------------------|

| 1-0   | J5, Pin 4; J5, Pin 2   | 17-16 | J5, Pin 36; J5, Pin 34 |

| 3-2   | J5, Pin 8; J5, Pin 6   | 19-18 | J5, Pin 40; J5, Pin 38 |

| 5-4   | J5, Pin 12; J5, Pin 10 | 21-20 | J5, Pin 44; J5, Pin 42 |

| 7-6   | J5, Pin 16; J5, Pin 14 | 23-22 | J5, Pin 48; J5, Pin 46 |

| 9-8   | J5, Pin 20; J5, Pin 18 | 25-24 | J5, Pin 52; J5, Pin 50 |

| 11-10 | J5, Pin 24; J5, Pin 22 | 27-26 | J5, Pin 56; J5, Pin 54 |

| 13-12 | J5, Pin 28; J5, Pin 26 | 29-28 | J5, Pin 60; J5, Pin 58 |

| 15-14 | J5, Pin 32; J5, Pin 30 | 31-30 | J5, Pin 64; J5, Pin 62 |

Table 2-7: Differential Expansion Header GPIO Regs (Addr 0x90001000-0x90001004)

## ML40x Single-Ended Expansion Header General Purpose I/O Registers

Table 2-8 shows the single-ended expansion header registers, which are a standard set of GPIO data/direction registers at address 0x90001008-0x9000100C.

Table 2-8: Single-Ended Expansion Header GPIO Regs (Addr 0x90001008-0x9000100C)

| Bit | Description | Bit | Description |

|-----|-------------|-----|-------------|

| 0   | J6, Pin 2   | 16  | J6, Pin 34  |

| 1   | J6, Pin 4   | 17  | J6, Pin 36  |

| 2   | J6, Pin 6   | 18  | J6, Pin 38  |

| 3   | J6, Pin 8   | 19  | J6, Pin 40  |

| 4   | J6, Pin 10  | 20  | J6, Pin 42  |

| 5   | J6, Pin 12  | 21  | J6, Pin 44  |

| 6   | J6, Pin 14  | 22  | J6, Pin 46  |

| 7   | J6, Pin 16  | 23  | J6, Pin 48  |

| 8   | J6, Pin 18  | 24  | J6, Pin 50  |

| 9   | J6, Pin 20  | 25  | J6, Pin 52  |

| 10  | J6, Pin 22  | 26  | J6, Pin 54  |

| 11  | J6, Pin 24  | 27  | J6, Pin 56  |

| 12  | J6, Pin 26  | 28  | J6, Pin 58  |

| 13  | J6, Pin 28  | 29  | J6, Pin 60  |

| 14  | J6, Pin 30  | 30  | J6, Pin 62  |

| 15  | J6, Pin 32  | 31  | J6, Pin 64  |

## **Extending or Modifying the Design**

The ML40*x* Embedded Processor Reference System is a good starting point from which a user can add, remove, or modify components in the system. Because most of the IP in the design is attached to the CoreConnect infrastructure under EDK, adding or removing devices is a fairly straightforward process. Below is an overview for making various changes to the system.

## Adding or Removing IP Cores

To remove an IP core:

- 1. Delete the instantiation for that piece of IP from the **system.mhs** file (or use the **Add/Edit Cores** feature of the EDK GUI).

- 2. Delete all corresponding external I/O ports from the system.mhs file.

- 3. Remove corresponding UCF file entries specifying timing or pinout locations for that IP.

To add an IP core:

- 1. Instantiate the device by adding it to the **system.mhs** file (or use the **Add/Edit Cores** feature of the EDK GUI).

- 2. Connect its external I/O to the top level.

- 3. Set its configuration parameters (i.e., base address) in the **system.mhs** file (or use the **Add/Edit Cores** feature of the EDK GUI).

- 4. Add appropriate timing and pinout constraints to the UCF file.

## Chapter 3

## **EDK** Tutorial and Demonstration

## Introduction

This chapter contains basic instructions for using the EDK tools with the ML40*x* Embedded Processor Reference System. It is designed to help illustrate the steps to build and download the design. Information about demonstration software applications is also provided. The instructions that follow provide only an overview of the capabilities of EDK. Much more detail about operating the EDK tools can be found in the EDK documentation. This chapter assumes that the reference design and all other necessary tools are properly installed.

## Instructions for Invoking the EDK tools

This tutorial section and those that follow have directory path names that are shown separated by the "/" character as per the UNIX convention. For Windows, the """ should be used to separate directory paths.

The instructions that follow reference the *<EDK Project Directory>* located at:

- ML401

- MicroBlaze: <Reference Design Install Directory>/projects/ml401\_emb\_ref/

- ML402

- MicroBlaze: <Reference Design Install Directory>/projects/ml402\_emb\_ref/

- ML403

- MicroBlaze: < Reference Design Install Directory > / projects / ml403\_emb\_ref /

- PPC405: <*Reference Design Install Directory*>/projects/ml403\_emb\_ref\_ppc/

- ML405

- MicroBlaze: <*Reference Design Install Directory*>/projects/ml405\_emb\_ref/

- PPC405: <*Reference Design Install Directory*>/projects/ml405\_emb\_ref\_ppc/

These are the areas where the EDK Xilinx Microprocessor Project (XMP) files reside after installing the ML40*x* Embedded Processor Reference System.

### Launching Xilinx Platform Studio (XPS)

1. Open the XPS GUI.

On a PC, click:

#### $Start \rightarrow Programs \rightarrow Xilinx \ Platform \ Studio.$

On Linux, source the necessary environment scripts, and launch XPS:

\$ xps

Open XPS project file for the ML40*x* Embedded Processor Reference System: Click File →Open Project.

Browse to find the <EDK Project Directory>.

Select the file **system.xmp**, click **Open**.

This opens the project file under EDK. It is now ready to build or download the system using the user-selected software application program. You are now ready to proceed with the following instructions.

## Instructions for Selecting Software Application

The **system.xmp** EDK project file supports multiple user software applications. To select which software application to compile, follow the instructions below.

- 1. Click the Applications tab on the left-hand pane, then scroll down and look for **Project: hello\_uart**.

- 2. Right-click on Project: hello\_uart and select Make Project Active.

**Note:** This tutorial uses the **hello\_uart** application as an example. To select a different software application, right-click on the active project and select **Make Project Inactive**. Then find the software application of interest and make that project active. See "Software," page 39 for more information.

## Instructions for Building and Implementing the Design

After successfully loading the design, it can now be synthesized and place-and-routed to be run on real ML40*x* hardware.

1. Synthesize the design.

In XPS, click **Hardware**→**Generate Netlist**.

*Note:* This step might take some time to complete.

In XPS, click **Hardware**→**Generate Bitstream**.

*Note:* This step might take some time to complete.

## Instructions for Downloading the Design

The hardware bitstreams and software binary executable files can be downloaded to the ML40*x* board using a download cable (Xilinx Parallel Cable IV or Platform Cable USB) or the System ACE interface.

The downloaded design runs the hello\_uart program. To see this program running, connect a serial cable from a PC to the ML40*x* board. Use a terminal program like HyperTerminal (shipped with Windows) and set the COM port settings to 9600 baud, 8 Data Bits, No Parity, 1 Stop Bit, No flow control. After the program is downloaded using the instructions below, you should see Hello World! on your terminal. The board then echoes the characters you type until you press the Escape key.

# Download Using Parallel Cable IV or Platform Cable USB (iMPACT Program)

After the design is implemented, a bitstream can be generated and downloaded into an FPGA using a program like iMPACT, available with the Xilinx ISE tools. (A PC should be used for this step.)

- 1. Connect the download cable from a PC to the ML40*x* board and power on the board.

- 2. Click **Device Configuration** → **Download Bitstream** within XPS.

*Note:* This loads a bitstream containing a bootloop program that effectively idles the processor - *not* the software program that you have specified. You must continue with the remaining steps in this section to load your program.

3. Click **Debug** → **Launch XMD**...

**Note:** On the ML401 board, you must configure XMD to communicate with the opb\_mdm module using BSCAN number 1 instead of the default of BSCAN 0. Refer to the *<EDK Project Directory*>/README file and Solution Record #20060 for more information. By default, the ML401 xmd\_microblaze\_0.opt file is configured for Parallel Cable IV download and requires editing for use with the Platform Cable USB.

**Note:** For ML402, ML403, and ML405, the "set the XMD Debug Options...," message appears the first time you run XMD. Click **OK** to enter debug option information such as the type of JTAG cable you are using. Then click **Save** when finished. You may change debug options at any time by selecting Debug $\rightarrow$ XMD Debug Options from the XPS GUI. Refer to the *<EDK Project Directory*/README file for more information.