# Spartan-3AN FPGA In-System Flash User Guide

For Spartan™-3AN FPGA applications that read or write data to or from the In-System Flash memory after configuration

UG333 (v1.1.1) September 24, 2007

Xilinx is disclosing this Document and Intellectual Property (hereinafter "the Design") to you for use in the development of designs to operate on, or interface with Xilinx FPGAs. Except as stated herein, none of the Design may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Any unauthorized use of the Design may violate copyright laws, trademark laws, the laws of privacy and publicity, and communications regulations and statutes.

Xilinx does not assume any liability arising out of the application or use of the Design; nor does Xilinx convey any license under its patents, copyrights, or any rights of others. You are responsible for obtaining any rights you may require for your use or implementation of the Design. Xilinx reserves the right to make changes, at any time, to the Design as deemed desirable in the sole discretion of Xilinx. Xilinx assumes no obligation to correct any errors contained herein or to advise you of any correction if such be made. Xilinx will not assume any liability for the accuracy or correctness of any engineering or technical support or assistance provided to you in connection with the Design.

THE DESIGN IS PROVIDED "AS IS" WITH ALL FAULTS, AND THE ENTIRE RISK AS TO ITS FUNCTION AND IMPLEMENTATION IS WITH YOU. YOU ACKNOWLEDGE AND AGREE THAT YOU HAVE NOT RELIED ON ANY ORAL OR WRITTEN INFORMATION OR ADVICE, WHETHER GIVEN BY XILINX, OR ITS AGENTS OR EMPLOYEES. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DESIGN, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND NONINFRINGEMENT OF THIRD-PARTY RIGHTS.

IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOST DATA AND LOST PROFITS, ARISING FROM OR RELATING TO YOUR USE OF THE DESIGN, EVEN IF YOU HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. THE TOTAL CUMULATIVE LIABILITY OF XILINX IN CONNECTION WITH YOUR USE OF THE DESIGN, WHETHER IN CONTRACT OR TORT OR OTHERWISE, WILL IN NO EVENT EXCEED THE AMOUNT OF FEES PAID BY YOU TO XILINX HEREUNDER FOR USE OF THE DESIGN. YOU ACKNOWLEDGE THAT THE FEES, IF ANY, REFLECT THE ALLOCATION OF RISK SET FORTH IN THIS AGREEMENT AND THAT XILINX WOULD NOT MAKE AVAILABLE THE DESIGN TO YOU WITHOUT THESE LIMITATIONS OF LIABILITY.

The Design is not designed or intended for use in the development of on-line control equipment in hazardous environments requiring fail-safe controls, such as in the operation of nuclear facilities, aircraft navigation or communications systems, air traffic control, life support, or weapons systems ("High-Risk Applications"). Xilinx specifically disclaims any express or implied warranties of fitness for such High-Risk Applications. You represent that use of the Design in such High-Risk Applications is fully at your risk.

© 2007 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

## **Revision History**

The following table shows the revision history for this document.

| Date     | Version | Revision                                                                                                                                                                               |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 02/26/07 | 1.0     | Initial release.                                                                                                                                                                       |

| 08/29/07 | 1.1     | Updated throughout. Removed legacy commands not recommended for designs. Added "MultiBoot Configuration Bitstream Guidelines". Simplified discussion in Chapter 7, "Power Management". |

| 09/24/07 | 1.1.1   | Add Caution to Chapter 1, "Overview and SPI_ACCESS Interface,", that SPI_ACCESS is not currently supported in simulation.                                                              |

| Chapter 1: Overview and SPI_ACCESS Interface                         |

|----------------------------------------------------------------------|

| In-System Flash Summary 7                                            |

| Accessing In-System Flash Memory After Configuration                 |

| SPI_ACCESS Design Primitive                                          |

| HDL Instantiation Examples                                           |

| VHDL       10         Verilog       11                               |

| SPI Transactions                                                     |

| Example Detailed Command Sequence                                    |

|                                                                      |

| Chapter 2: In-System Flash Memory Architecture                       |

| Block Diagram                                                        |

| Flash Memory Array 15                                                |

| Addressing Overview                                                  |

| Addressing Modes                                                     |

| Default Addressing Mode                                              |

| Delivered State                                                      |

| Memory Allocation Tables                                             |

| MultiBoot Configuration Bitstream Guidelines                         |

| Align to Flash Sector Boundaries                                     |

| Additional Memory Space Required for DCM_WAIT                        |

| User Data Storage Guidelines                                         |

| Chapter 3: Read Commands                                             |

| •                                                                    |

| Fast Read                                                            |

| Random Read                                                          |

| Page to Buffer Transfer                                              |

| Buffer Read                                                          |

| Chapter 4: Write and Program Commands                                |

| Chapter 4: Write and Program Commands                                |

| Buffer Write                                                         |

| Buffer to Page Program with Built-in Erase                           |

| Buffer to Page Program without Built-in Erase                        |

| Page Program Through Buffer 44                                       |

| Page to Buffer Compare (Program Verify) 46                           |

| Pre-initializing SRAM Page Buffer Contents                           |

| EEPROM-Like, Byte-Level Write Operations                             |

| <b>Sequential vs. Random Page Programming, Cumulative Operations</b> |

| Auto Page Rewrite 49                                                 |

|                                                                      |

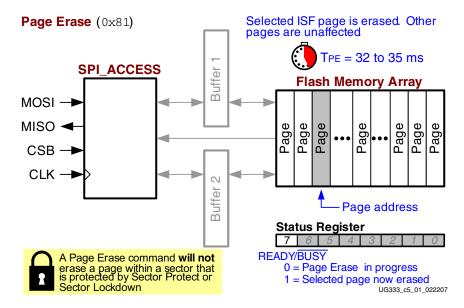

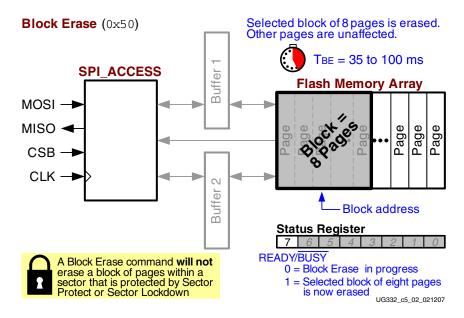

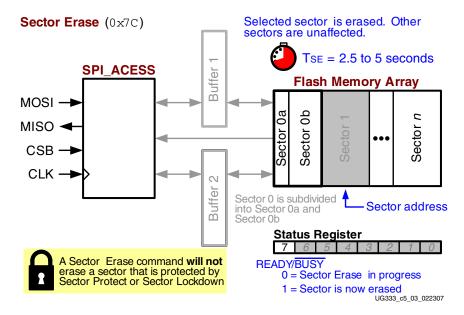

| Chapter 5: Erase Commands                                            |

| Sector Protect and Sector Lockdown Prevent Erase Operations          |

| Erased State                                                         |

| Page Erase 52                                                        |

| Block Erase                                                       | 54 |

|-------------------------------------------------------------------|----|

| Sector Erase                                                      | 57 |

| Sector Addressing                                                 |    |

| Default Addressing Mode                                           |    |

| Operation Timing                                                  | 61 |

| Chapter 6: Status and Information Commands                        |    |

| Status Register                                                   | 63 |

| READY/BUSY                                                        |    |

| Compare                                                           |    |

| ISF Memory Size                                                   |    |

| Sector Protect                                                    |    |

| Page Size                                                         |    |

| Status Register Read                                              |    |

| Information Read                                                  |    |

| Manufacturer Identifier                                           |    |

| Family Code/Memory Density Code                                   |    |

| Memory Type/Product Version Code                                  |    |

| Extended Device Information Field                                 |    |

| Chapter 7: Power Management                                       |    |

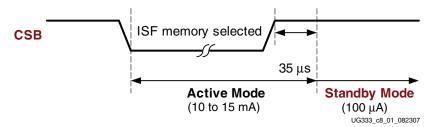

| Active Mode                                                       |    |

| Standby Mode                                                      |    |

| Thermal Considerations                                            |    |

| Thermal Considerations                                            |    |

| Chapter 8: Sector-Based Program/Erase Protection                  |    |

| Sector Protection                                                 | 7/ |

| Sector Protection Status at Power-Up                              |    |

| Sector Protection Register                                        |    |

| Sector Protection Register Erase                                  |    |

| Sector Protection Register Program                                |    |

| Unprotecting Sectors While Sector Protection Enabled              |    |

| Sector Protection Register Limited to 10,000 Program/Erase Cycles |    |

| Sector Protection Register Read                                   |    |

| Sector Protection Enable                                          |    |

| Sector Protection Disable                                         |    |

| Sector Lockdown                                                   |    |

| Sector Lockdown Program                                           |    |

| Sector Lockdown Register                                          |    |

|                                                                   |    |

| Chapter 9: Security Register                                      |    |

| Security Register                                                 | 83 |

| Security Register Program                                         |    |

| Security Register Read                                            | 84 |

## Appendix 10: Optional Power-of-2 Addressing Mode

| How to Determine the Current Addressing Mode           | 87 |

|--------------------------------------------------------|----|

| Permanently Changing to the Power-of-2 Addressing Mode | 88 |

| Power-of-2 Addressing Mode                             | 88 |

| Power-of-2 Addressing                                  | 89 |

| Power-of-2 Page Addressing                             | 89 |

| Power-of-2 Block Addressing                            | 90 |

| Power-of-2 Sector Addressing                           | 90 |

# Overview and SPI\_ACCESS Interface

**Note:** This user guide only applies to Spartan<sup>™</sup>-3AN FPGA designs that access or modify the insystem Flash *after* configuration. This user guide is not required for applications that only use the insystem Flash to configure the FPGA. For Spartan-3AN FPGA configuration information, see UG332: Spartan-3 Generation Configuration User Guide.

Spartan-3AN FPGAs include abundant In-System Flash (ISF) memory. The ISF memory array appears to a Spartan-3AN FPGA application as SPI-based serial Flash memory. The ISF memory is primarily designed to automatically configure the FPGA when power is applied or whenever the PROG\_B pin is pulsed Low. However, the ISF memory array is large enough to store ...

- two complete, uncompressed FPGA configuration bitstreams. Using the MultiBoot feature, the FPGA application can selectively choose between the two designs or reserve one image as a fail-safe image for live in-system Flash updates.

- additional nonvolatile data for the FPGA application, such as MicroBlaze<sup>™</sup> processor code, serial numbers, Ethernet MAC IDs, graphic images, message templates, and so on.

## **In-System Flash Summary**

Table 1-1, page 8 summarizes the key attributes and capabilities of the ISF memory. The remainder of this user guide describes these features and capabilities in greater detail.

The table also summarizes the amount of Flash memory available to the FPGA application, depending on the number of design options.

- How many FPGA configuration bitstreams are stored in the ISF array?

- Most applications store a single FPGA configuration bitstream, leaving the remaining space for nonvolatile user data.

- Optionally, each Spartan-3AN FPGA can store two uncompressed MultiBoot configuration images, which reduces the amount of Flash memory available to the application.

- Does the FPGA application use the ISF memory's Sector Protect or Sector Lockdown features to protect ISF memory contents?

- Without using the sector-based data protection features, user application data can be stored in the next available page location following the FPGA bitstream (page aligned).

- If the application uses the sector-based data protection features, then user application data is typically aligned to the next sector boundary (sector aligned).

Table 1-1: In-System Flash Memory Summary

|                                                                                                                                |                    |                              |                                  |                                  | Spartan-3AN FPGA                 |                                     |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------------|----------------------------------|----------------------------------|----------------------------------|-------------------------------------|--|--|--|--|--|--|--|

| Description                                                                                                                    |                    | 3S50AN                       | 3S200AN                          | 3S400AN                          | 3S700AN                          | 3S1400AN                            |  |  |  |  |  |  |  |

| In-System Flash (ISF) memory bits                                                                                              | 1,081,344<br>(1M+) | 4,325,376<br>(4M+)           | 4,325,376<br>(4M+)               | 8,650,752<br>(8M+)               | 17,301,504<br>(16M+)             |                                     |  |  |  |  |  |  |  |

| SRAM page buffers                                                                                                              |                    | 1                            | 2                                | 2                                | 2                                | 2                                   |  |  |  |  |  |  |  |

| Default Addressing Mode page size (byte                                                                                        | es)                | 264                          | 264                              | 264                              | 264                              | 528                                 |  |  |  |  |  |  |  |

| Optional Power-of-2 Addressing Mode pa                                                                                         | ige size (bytes)   | 256                          | 256                              | 256                              | 256                              | 512                                 |  |  |  |  |  |  |  |

| Pages                                                                                                                          |                    | 512                          | 2,048                            | 2,048                            | 4,096                            | 4,096                               |  |  |  |  |  |  |  |

| Blocks                                                                                                                         |                    | 64                           | 256                              | 256                              | 512                              | 512                                 |  |  |  |  |  |  |  |

| Sectors                                                                                                                        |                    | 4                            | 8                                | 8                                | 16                               | 16                                  |  |  |  |  |  |  |  |

| Pages per Block                                                                                                                |                    | 8                            | 8                                | 8                                | 8                                | 8                                   |  |  |  |  |  |  |  |

| Pages per Sector                                                                                                               |                    | 128                          | 256                              | 256                              | 256                              | 256                                 |  |  |  |  |  |  |  |

| Bytes per Block                                                                                                                |                    | 2,112                        | 2,112                            | 2,112                            | 2,112                            | 4,224                               |  |  |  |  |  |  |  |

| Bytes per Sector                                                                                                               | Bytes per Sector   |                              |                                  |                                  | 67,584                           | 135,168                             |  |  |  |  |  |  |  |

| FPGA configuration bitstream size (unco                                                                                        | mpressed)          | 437,312                      | 1,196,128                        | 1,886,560                        | 2,732,640                        | 4,755,296                           |  |  |  |  |  |  |  |

| Pages required for FPGA bitstream,                                                                                             | Default            | 208                          | 567                              | 894                              | 1,294                            | 1,126                               |  |  |  |  |  |  |  |

| always starting at page 0                                                                                                      | Power-of-2         | 214                          | 585                              | 922                              | 1,335                            | 1,161                               |  |  |  |  |  |  |  |

| Page Aligned User Data (maximizes ava                                                                                          | ailable data sp    | ace but limi                 | ts Sector Pr                     | rotect, Sect                     | or Lockdow                       | n features)                         |  |  |  |  |  |  |  |

| Pages available for user application beyon<br>configuration bitstream, data aligned to r<br>boundary, Default Addressing Mode  | 304                | 1,481                        | 1,154                            | 2,802                            | 2,970                            |                                     |  |  |  |  |  |  |  |

| Total Flash memory bits available for use<br>Default Addressing Mode                                                           | r application,     | 642,048<br>(627K)<br>(0.61M) | 3,127,872<br>(3,054K)<br>(2.98M) | 2,437,248<br>(2,380K)<br>(2.32M) | 5,917,824<br>(5,779K)<br>(5.64M) | 12,545,280<br>(12,251K)<br>(11.96M) |  |  |  |  |  |  |  |

| Sector Aligned User Data (user data ali                                                                                        | gned to sector     | s for Secto                  | r Protect, Se                    | ector Lockd                      | own feature                      | s)                                  |  |  |  |  |  |  |  |

| Sectors required per uncompressed FPGA                                                                                         | A bitstream        | 2                            | 3                                | 4                                | 6                                | 5                                   |  |  |  |  |  |  |  |

| Sectors available for user application beyonfiguration bitstream, aligned to next s boundary                                   |                    | 2                            | 5                                | 4                                | 10                               | 11                                  |  |  |  |  |  |  |  |

| Total bits available for user application in sectors, Default Addressing Mode                                                  | remaining          | 540,672<br>(528K)<br>(0.51M) | 2,703,360<br>(2,640K)<br>(2.57M) | 2,162,688<br>(2,112K)<br>(2.06M) | 5,406,720<br>(5,280K)<br>(5.15M) | 11,894,784<br>(11,616K)<br>(11.34M) |  |  |  |  |  |  |  |

| MultiBoot FPGA Configuration                                                                                                   |                    |                              | +                                | +                                | +                                | +                                   |  |  |  |  |  |  |  |

| Maximum number of uncompressed Mul configuration images                                                                        | tiBoot FPGA        | 2                            | 2                                | 2                                | 2                                | 2                                   |  |  |  |  |  |  |  |

| Total sectors available for user application<br>MultiBoot FPGA configuration bitstreams                                        |                    | 0                            | 2                                | 0                                | 4                                | 6                                   |  |  |  |  |  |  |  |

| Total Flash memory bits available for use<br>beyond MultiBoot FPGA configuration be<br>sector aligned, Default Addressing Mode | itstreams,         | 0                            | 1,081,344<br>(1,056K)<br>(1.03M) | 0                                | 2,162,688<br>(2,112K)<br>(2.06M) | 6,488,064<br>(6,336K)<br>(6.18M)    |  |  |  |  |  |  |  |

## **Accessing In-System Flash Memory After Configuration**

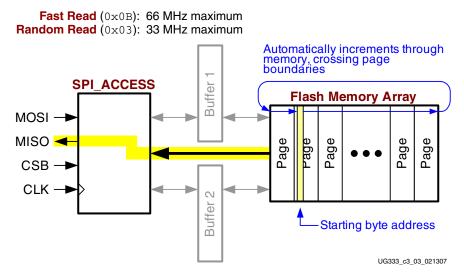

#### SPI\_ACCESS Design Primitive

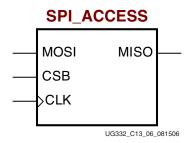

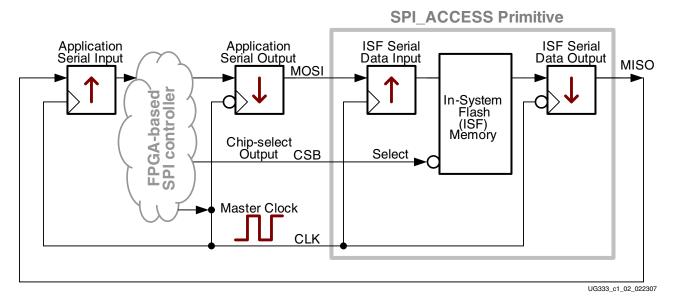

After the FPGA configures, the application loaded into the FPGA can access the ISF memory using a special design primitive called SPI\_ACCESS, shown in Figure 1-1. All data accesses to and from the ISF memory are performed using an SPI serial protocol. Neither the Spartan-3AN FPGA itself nor the SPI\_ACCESS primitive includes a dedicated SPI master controller. Instead, the control logic is implemented using the FPGA's programmable logic resources. The SPI\_ACCESS primitive essentially connects the FPGA application to the In-System Flash memory array.

Figure 1-1: SPI\_ACCESS Primitive (only available on Spartan-3AN FPGAs)

Table 1-2 describes the connections to the SPI\_ACCESS primitive. The serial data lines are names relating to the logic that drives the data. The FPGA application is always the Master of each SPI transaction; the ISF memory is always the Slave.

| Port Name | Direction | Function                                                                                                                         |

|-----------|-----------|----------------------------------------------------------------------------------------------------------------------------------|

| MISO      | Output    | <u>M</u> aster <i>I</i> nput, <u>S</u> lave <u>O</u> utput. Serial data output from the ISF memory array back to the FPGA logic. |

| MOSI      | Input     | <u>M</u> aster <u>O</u> utput, <u>S</u> lave <u>I</u> nput. Serial data input to the ISF memory array from the FPGA logic.       |

| CSB       | Input     | Active-Low chip-enable to ISF memory array, driven by FPGA logic.                                                                |

| CLK       | Input     | Clock input to ISF memory array, driven by FPGA logic.                                                                           |

Table 1-2: SPI\_ACCESS Primitive Connections

Table 1-3 describes the available attributes for the SPI\_ACCESS primitive.

Table 1-3: SPI\_ACCESS Primitive Attributes

| Attribute      | Туре                             | Allowed Values                                      | Default       | Description                                                                             |

|----------------|----------------------------------|-----------------------------------------------------|---------------|-----------------------------------------------------------------------------------------|

| SIM_DEVICE     | String                           | 3S50AN, 3S200AN,<br>3S400AN, 3S700AN<br>or 3S1400AN | "unspecified" | Specifies the target device so that the proper size ISF memory is used. Required.       |

| SIM_FACTORY_ID | SIM_FACTORY_ID 64-bit Bit Vector |                                                     | All zeroes    | Optionally specifies the factory-programmed unique identifier in the Security Register. |

| SIM_USER_ID    | 64-bit Bit<br>Vector             | Any 64-bit value                                    | All zeroes    | Optionally specifies the user-defined field in the Security Register.                   |

| SIM_MEM_FILE   | String                           | Any file and directory name                         | "none"        | Optionally specifies a hex file containing the memory contents for the ISF memory.      |

#### **HDL Instantiation Examples**

The SPI\_ACCESS design primitive must be instantiated in an HDL design; it cannot be inferred by the logic synthesis software.

**Caution!** The SPI\_ACCESS In-System Flash memory operations are not currently supported in simulation.

#### **VHDL**

The SPI\_ACCESS primitive requires that the Xilinx Unisim Library be declared. Instantiate the SPI\_ACCESS component and connect it to the other signals in the design.

#### Xilinx Unisim Library

The Xilinx Unisim library includes definitions for all the Spartan-3AN FPGA design primitives, including the SPI\_ACCESS primitive. Declare the Unisim library before the **entity** declaration.

```

library UNISIM;

use UNISIM.VComponents.all;

entity XXXX is

```

#### Instantiate SPI ACCESS Primitive

Instantiate the SPI\_ACCESS design primitive after the **architecture** declaration. Connect each of the four SPI\_ACCESS ports to a signal name in the FPGA application.

```

architecture Behavioral of XXXX is

begin

...

SPI_ACCESS_inst: SPI_ACCESS

generic map (

SIM_DEVICE => "3S700AN"

)

port map (

MISO => MISO_signal, -- 1-bit SPI output data

MOSI => MOSI_signal, -- 1-bit SPI input data

CSB => CSB_signal, -- 1-bit SPI chip enable

CLK => CLK_signal -- 1-bit SPI clock input

);

-- End of SPI_ACCESS_inst instantiation

```

#### Verilog

Using Verilog, simply connect the SPI\_ACCESS design primitive to signal names within the FPGA application.

```

SPI_ACCESS #(

.SIM_DEVICE("3S700AN")

) SPI_ACCESS_inst (

.MISO(MISO_signal), // 1-bit SPI output data

.MOSI(MOSI_signal), // 1-bit SPI input data

.CSB(CSB_signal), // 1-bit SPI chip enable

.CLK(CLK_signal) // 1-bit SPI clock input

);

// End of SPI_ACCESS_inst instantiation

```

#### **SPI Transactions**

The SPI\_ACCESS primitive uses a typical SPI serial transaction protocol. By default, the interface supports SPI "Mode 3" transfers.

**Caution!** The SPI\_ACCESS SPI serial transaction protocol is not currently supported in simulation.

Figure 1-2: FPGA-to-SPI\_ACCESS Interface and Active Clock Edges

- All transactions are controlled by a SPI Master controller, built using FPGA logic.

- All transactions are synchronized by the CLK input on the SPI\_ACCESS primitive.

The FPGA application generates the CLK signal.

- The SPI protocol uses both the rising and falling edges of the CLK signal.

- The FPGA application selects the ISF memory by driving the SPI\_ACCESS CSB input Low when the CLK input is High and de-selects the ISF memory by driving the CSB input High.

- When CSB returns High, the current command is terminated.

- The SPI Master, which is the FPGA application, starts every transaction by supplying a command code or command sequence to the SPI\_ACCESS MOSI input.

- The CSB select input must be Low throughout the duration of a transaction. It cannot change during the middle of an operation. Some ISF memory operations, such as erasing a page or sector, continue automatically even after the SPI transaction is complete.

- The FPGA application supplies data to the ISF memory via the SPI\_ACCESS MOSI input, clocked on the falling edge of CLK.

- The ISF memory captures any data supplied on the SPI\_ACCESS MOSI input using the rising edge of CLK.

- The ISF memory presents data or status on the SPI\_ACCESS MISO output using the falling edge of CLK.

- The FPGA application captures any data supplied by the ISF memory on the SPI\_ACCESS MISO output using the rising edge of CLK.

- Because MISO output data changes every falling edge of CLK, the FPGA can also capture data on the falling edge of CLK to simplify the FPGA application.

- All data, commands, and address information are supplied serially, ordered from most-significant bit to least-significant bit.

- When the CSB select input is High to deselect the ISF memory, the SPI\_ACCESS MISO output is High.

#### **Example Detailed Command Sequence**

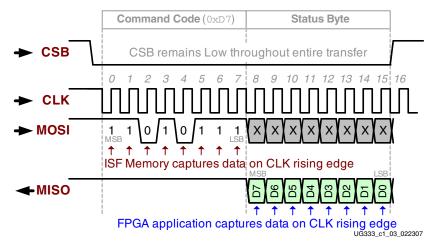

Figure 1-3 provides a detailed example of a command sequence that reads the Status Register. This example shows the relation of the various control signals and the clock edges when data appears and is captured.

Figure 1-3: Status Register Read Command Sequence

- 1. The FPGA application starts the command by driving the SPI\_ACCESS CSB input Low, while the CLK input is High. Subsequently, the CSB input must remain Low throughout the entire transfer.

- The Status Register Read command code is 0xD7, as detailed in Table 6-7, page 66. As mentioned in "SPI Transactions," all data is transferred most-significant bit first.

Consequently, the FPGA application clocks in the binary pattern "11010111" on the MOSI input, synchronized to the falling edge of CLK.

- The ISF memory captures the command sequence on the rising edge of CLK, as indicated.

- 4. Before data appears, the MISO output is High.

- 5. After all eight command bits are transferred, the ISF memory provides the current Status Register contents on the SPI\_ACCESS MISO output. Again, the data appears most-significant bit first, synchronized to the falling edge of CLK.

- 6. The FPGA application captures the ISF status information on the rising edge of CLK.

- 7. After receiving the last bit of status information, the FPGA application drives the CSB input High to end the transaction.

# In-System Flash Memory Architecture

#### **Block Diagram**

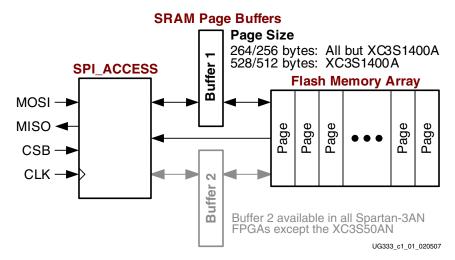

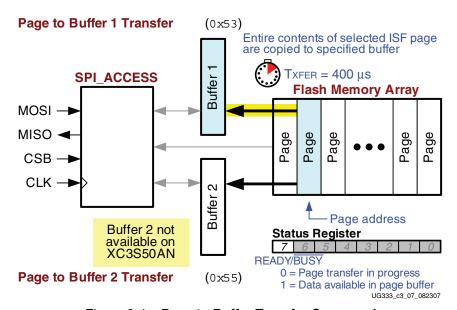

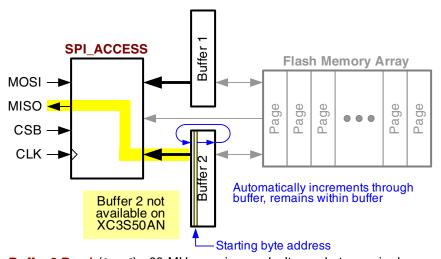

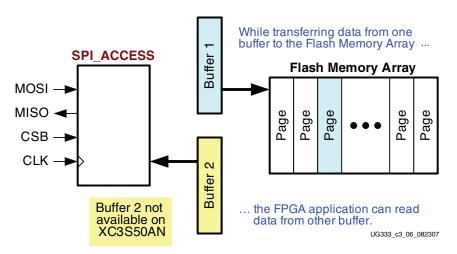

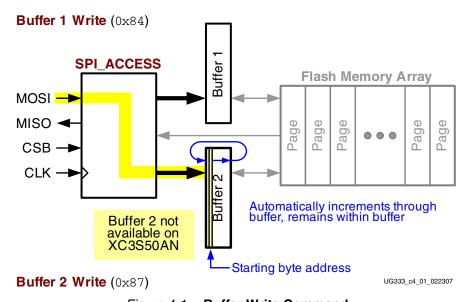

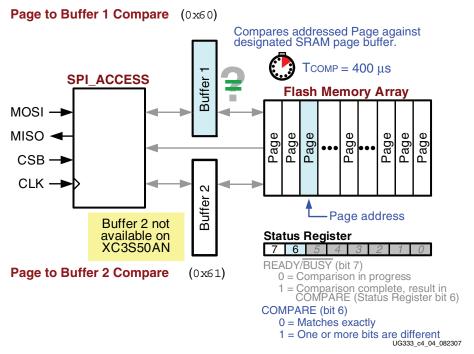

The Spartan<sup>TM</sup>-3AN FPGA In-System Flash (ISF) memory consists of a main nonvolatile, reprogrammable Flash memory array and one or two SRAM page buffers, as shown in Figure 2-1. The Flash memory array is organized into Pages, Blocks, and Sectors. The smallest erasable unit is a Page. Page size depends on both the device and the addressing mode. The one or two SRAM page buffers simplify system interfaces and data programming. All Spartan-3AN FPGAs, except the XC3S50AN FPGA, have two SRAM page buffers. The XC3S50AN FPGA has a single such buffer.

All accesses to the ISF from the FPGA application are through a four-wire SPI interface, as described in "SPI\_ACCESS Design Primitive," page 9.

Figure 2-1: Internal SPI Flash Block Diagram

## **Flash Memory Array**

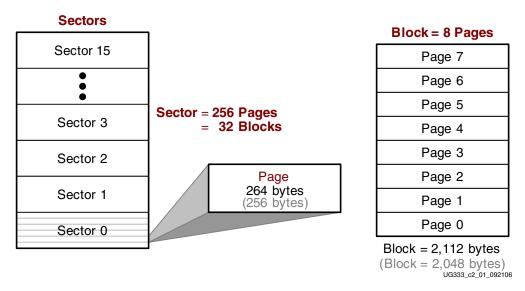

For optimal flexibility, the In-System Flash (ISF) memory is divided into three levels of granularity, as shown in Figure 2-2. Figure 2-2 shows a specific example for the XC3S700AN. Other Spartan-3AN FPGA family members are similar but either have a different number of sectors or a different page size. The number of sectors and page size for other Spartan-3AN FPGAs is listed in Table 2-1, page 16.

Figure 2-2: XC3S700AN Internal SPI Flash Memory Hierarchy

Table 2-1: Spartan-3AN FPGA Memory Architecture

| Device     | Total Flash<br>Bits | Sectors | Sector Size | Pages per<br>Sector | Total<br>Pages | Page Size<br>(Bytes) |

|------------|---------------------|---------|-------------|---------------------|----------------|----------------------|

| XC3S50AN   | 1,081,344           | 4       | 33K         | 128                 | 512            | 264                  |

| XC3S200AN  | 4,325,376           | 8       | 66K         |                     | 2,048          | 264                  |

| XC3S400AN  | 4,325,376           | 8       | 66K         | 256                 | 2,048          | 264                  |

| XC3S700AN  | 8,650,752           | 16      | 66K         | 230                 | 4,096          | 264                  |

| XC3S1400AN | 17,301,504          | 16      | 132K        |                     | 4,096          | 528                  |

The most basic construct within the hierarchy is a memory *Page*. By default, a Page consists of 264 bytes, except on the XC3S1400AN FPGA, which has a larger page size of 528 bytes. The page size is reduced when the Optional Power-of-2 Addressing Mode is selected, as shown in gray in Figure 2-2. The SRAM page buffer(s), shown in Figure 2-1, are large enough to hold an entire page image. A page is the smallest erasable element within the ISF memory, while a byte is the smallest readable and writable element within an SRAM page buffer.

Pages are also grouped into a larger structure called a *Block*, which consists of 8 pages. The Block Erase command provides an intermediate solution between the fast-but-small Page Erase command and the slower-but-larger Sector Erase command. Finally, pages and blocks are further combined into *Sectors*. A sector typically consists of 256 contiguous pages or 32 contiguous blocks, except on the XC3S50AN, which has 128 pages per sector. Sectors have additional control options. Sectors can be selectively write-protected by the FPGA application, a featured called Sector Protection. Similarly, sectors can be permanently locked down, preventing the contents from ever being erased or modified, using a feature called Sector Lockdown. The sector controls similarly affect any data bytes, pages, and blocks within the sector.

The ISF memory hierarchy directly impacts the ISF commands and addressing, as described in subsequent sections.

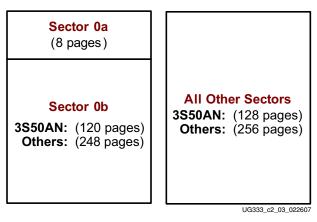

Sector 0 is further subdivided into two, individually protected sub-sectors, as shown in Figure 2-3. While the combined Sector 0 is the same size as all other sectors, Sector 0a is always 8 pages while Sector 0b represents the remaining pages in Sector 0. Consequently, the commands that operate on Sector 0 require slightly different addressing and control than the same commands used on other sectors.

Figure 2-3: Sector 0 is Sub-divided into Two Smaller Sub-sectors

Spartan-3AN FPGA applications generally never make use of the split Sector 0 structure, but applications must be aware that it exists in order to erase or protect Sector 0.

## **Addressing Overview**

All commands that require an address use a 24-bit address field to select a sector, a block, a page, or a byte location within a page. However, the In-System Flash memory supports two different possible addressing schemes.

#### **Addressing Modes**

- All Spartan-3AN FPGAs, as delivered, use the Default Addressing Mode, detailed in Table 2-2. All Xilinx software primarily supports this mode.

- With an additional, special programming step, described in Appendix 10, "Optional Power-of-2 Addressing Mode", Spartan-3AN FPGAs support a slightly different addressing mode, which may be more natural for some applications.

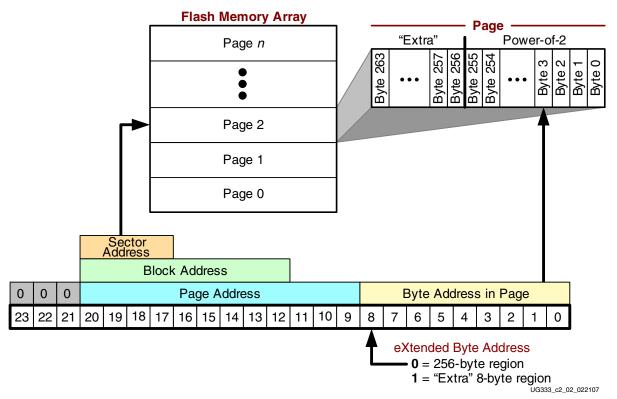

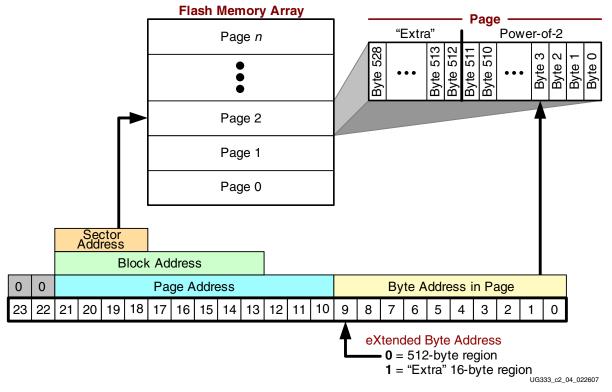

The Default Addressing Mode provides roughly 3% more total memory bits. Figure 2-4, page 18 shows the Flash memory array for the XC3S700AN FPGA, plus a detailed, expanded diagram of a page within the Flash array. The diagram also describes how the 24 bits in a command address field select a sector, block, page, or byte within a memory page. Figure 2-5 is a similar diagram specific to the XC3S1400AN, which uses a larger page size.

Using the Default Addressing Mode, each memory page is slightly larger than the typical power-of-2 page size found in other memories. For example, all Spartan-3AN FPGAs except the XC3S1400AN use a 264-byte page, while the XC3S1400AN memory pages are double the size at 528 bytes. The "extra" bits are useful for a variety of applications.

- More total nonvolatile memory for FPGA configuration or data storage applications.

- Page pointers, linked address pointers, attributes, and status indicators for a Flashbased file system.

- Error detection/correction bits for extreme applications.

• Counters, to track the number of program/erase cycles per page.

Figure 2-4: Default Addressing Mode for XC3S700AN FPGA

Figure 2-5: Default Addressing Mode, XC3S1400AN FPGA

#### **Default Addressing Mode**

In the default addressing mode, specific memory bytes are addressed by page and by the specific byte location within that page. As shown in Table 2-2, the number of pages and the page size varies by FPGA part number.

Table 2-2: Default Addressing Mode

|              |    | ļ  | Hig     | h A  | ddı  | ess  | 3         |      |                | N                   | lido       | lle A | Add    | ires        | s    |      |       |      | Lov  | v A      | ddr  | ess         | •    |       |

|--------------|----|----|---------|------|------|------|-----------|------|----------------|---------------------|------------|-------|--------|-------------|------|------|-------|------|------|----------|------|-------------|------|-------|

| FPGA         | 23 | 22 | 21      | 20   | 19   | 18   | 17        | 16   | 15             | 14                  | 13         | 12    | 11     | _           | 9    | 8    | 7     | 6    | 5    | 4        | 3    | 2           | 1    | 0     |

| 3S50AN       | 0  | 0  | 0       | 0    | 0    | 0    | Sec       | ctor |                |                     |            |       |        | I           | Don  | 't C | Care  | bit  | s    |          |      |             |      |       |

|              |    |    |         |      |      |      | SA1       | SA0  |                | Secto<br>Secto      |            |       | X      | X           | X    | X    | X     | X    | X    | X        | X    | X           | X    | X     |

|              |    |    |         |      |      |      |           | Blo  | ck A           | Add                 | ress       | 3     |        |             |      | I    | Don   | ′t C | are  | bit      | s    |             |      |       |

|              |    |    |         |      |      |      | BL5       | BL4  | BL3            | BL2                 | BL1        | BL0   | Х      | X           | X    | X    | X     | X    | X    | X        | X    | X           | X    | X     |

|              |    |    |         |      |      |      |           | Pag  | e A            | ddr                 | ess        | (512  | 2 pa   | ges)        |      |      | Byt   | e A  | ddr  | ess      | (264 | 1 by        | tes) |       |

|              |    |    |         |      |      |      | PA8       | 7    | 91             | 2                   | 44         | 3     | 2      | 1           | 0,   | 81   | 7     | 91   | 2    | 47       | 13   | 7           | 11   | 01    |

|              |    |    |         |      |      |      | PA        | PA7  | PA6            | PA5                 | PA4        | PA3   | PA2    | PA1         | PA0  |      | BA7   | BA6  | BA5  | BA4      | BA3  | BA2         | BA1  | BA0   |

| 3S200AN      | 0  | 0  | 0       | 0    | S    | ecto | or        |      |                |                     |            |       |        | Do          | on't | Ca   | re b  | its  |      |          |      |             |      |       |

| 3S400AN      |    |    |         |      | SA2  | SA1  | SA0       |      |                | ctor<br>ctor        |            |       | X      | X           | X    | X    | X     | X    | X    | X        | X    | X           | X    | X     |

|              |    |    |         |      |      | ]    |           | ck A | Add            | lres                | S          |       |        |             |      | I    | Don   | 't C | are  | bit      | S    |             |      |       |

|              |    |    |         |      | BL7  | BL6  | BL5       | BL4  | BL3            | BL2                 | BL1        | BL0   | Х      | Х           | Х    | X    | Х     | X    | Х    | X        | х    | х           | Х    | х     |

|              |    |    |         |      |      |      | age       | Ad   |                | ess (               |            |       | age    | es)         |      |      | Byt   | e A  | ddr  | ess      | (264 | l<br>1 by   | tes) |       |

|              |    |    |         |      | 0    |      |           |      |                | · ·                 |            | _     |        |             | 0    |      |       |      |      | l        |      |             |      |       |

|              |    |    |         |      | PA10 | PA9  | PA8       |      | PA6            | PA5                 | PA4        | PA3   | PA2    | PA1         | PA0  |      |       | BA6  | BA5  | BA4      | BA3  | BA2         | BA1  | BA0   |

| Bit Location | 23 | 22 | 21      | 20   | 19   | 18   | 17        | 16   | 15             | 14                  | 13         | 12    | 11     | 10          | 9    | 8    | 7     | 6    | 5    | 4        | 3    | 2           | 1    | 0     |

| 3S700AN      | 0  | 0  | 0       |      | Sec  | ctor |           |      |                |                     |            |       |        | DO          | on't | Ca   | re b  | 1ts  |      |          |      |             |      |       |

|              |    |    |         | SA3  | SA2  | SA1  | SA0       |      |                | ctor<br>ctor        |            |       | X      | X           | X    | X    | Χ     | X    | X    | X        | X    | X           | X    | X     |

|              |    |    |         |      |      | Bl   | ock       | Ac   | ldre           | ess                 |            |       |        |             |      | I    | Don   | 't C | Care | bit      | s    |             |      |       |

|              |    |    |         | BL8  | BL7  | BL6  | BL5       | BL4  | BL3            | BL2                 | BL1        | BL0   | х      | Х           | Х    | X    | X     | X    | X    | Х        | X    | х           | Х    | Х     |

|              |    |    |         |      |      | Pag  | ge A      | dd   | ress           | s (4,               | 096        | pag   | ges)   | )           |      |      | Byt   | e A  | ddr  | ess      | (264 | 1 by        | tes) |       |

|              |    |    |         | PA11 | PA10 | PA9  | PA8       | PA7  | PA6            | PA5                 | PA4        | PA3   | PA2    | PA1         | PA0  | BA8  | BA7   | BA6  | BA5  | BA4      | BA3  | BA2         | BA1  | BA0   |

| 3S1400AN     | 0  | 0  |         |      | ctor |      |           |      | _              |                     |            |       | ]      | Don         | 't C |      |       |      |      |          |      |             |      |       |

|              |    |    | SA3     | SA2  | SA1  | SA0  |           |      | ctor           |                     |            | х     | X      | X           | Х    | X    |       | Х    | Х    | х        | Х    | X           | Х    | X     |

|              |    |    |         |      |      |      | Ac        | ldre |                |                     |            |       |        |             |      | Do   | on't  | Ca   | re b | its      |      |             |      |       |

|              |    |    | BL8     | BL7  | BL6  | BL5  | BL4       | εŞ   | BL2            | BL1                 | BL0        | Х     | Х      | Х           | Х    | X    |       | Х    | Х    | Х        | Х    | Х           | Х    | Х     |

|              |    |    | $\sim$  | -    |      |      |           |      |                |                     |            |       |        | Address (52 |      |      |       |      |      |          |      |             |      |       |

|              |    |    | B       |      |      |      | dd        | ress | (4             | ddress (4,096 pages |            |       |        |             |      | By   | yte . | Ada  | lres | s (F     | 281  | byte        | 25)  |       |

|              |    |    |         |      | Pag  | ge A |           |      |                |                     |            |       |        |             | _    |      |       |      |      | <u>`</u> |      |             |      |       |

| Bit Location | 23 | 22 | PA11 Bl |      |      |      | dd<br>LY2 | ress | (4,<br>SVA SVA | 096<br>FY4          | pag<br>EW3 | ges)  | 11 PA1 | PA0         | BA9  |      | PA7   | Ado  | BY2  | BY4 83   | 28 l | byte<br>BY7 | es)  | • BA0 |

#### **Delivered State**

Each Spartan-3AN FPGA is delivered with an erased ISF memory. Engineering Samples may have a pre-programmed pattern, and should be erased and reprogrammed with the FPGA bitstream used in the end application.

- All Flash memory locations are erased and byte locations contain 0xFF.

- Spartan-3AN FPGAs use the "Default Addressing Mode," page 19.

- The "Sector Protection Register," page 74 is programmed with 0x00, indicating that all memory sectors are unprotected.

- The Unique Identifier field in the "Security Register," page 83 is permanently factory programmed with a value that is unique to every Spartan-3AN FPGA.

- The User-Defined Field in the "Security Register," page 83 is erased, and all locations are 0xFF.

## **Memory Allocation Tables**

The following tables describe how the ISF memory is allocated to FPGA configuration bitstreams and the portions that are available for page-aligned and sector-aligned data. The tables assume that the ISF memory contains two FPGA configuration bitstreams, the primary bitstream loaded at power-up and a secondary MultiBoot bitstream, starting at the next sector boundary. If the application does not require a MultiBoot bitstream, then the allocated ISF memory can be used for data storage. The physical address is shown for both the Default Addressing Mode and for the Optional Power-of-2 Addressing Mode. Consequently, the starting page number is different between the addressing modes for any user data that shares a sector with the end of an FPGA configuration bitstream.

- ISF memory allocation for the XC3S50AN FPGA is provided in Table 2-3, page 21.

- ISF memory allocation for the XC3S200AN FPGA is provided in Table 2-4, page 22.

- ISF memory allocation for the XC3S400AN FPGA is provided in Table 2-5, page 23.

- ISF memory allocation for the XC3S700AN FPGA is provided in Table 2-6, page 24.

- ISF memory allocation for the XC3S1400AN FPGA is provided in Table 2-7, page 25.

Table 2-3: XC3S50AN In-System Flash Memory Allocation

|                                                           |       |   | Defau | ult Addressing<br>Mode | Optional Power-of-2<br>Addressing Mode |           |  |  |

|-----------------------------------------------------------|-------|---|-------|------------------------|----------------------------------------|-----------|--|--|

| Allocation                                                | Secto | r | Page  | Address                | Page                                   | Address   |  |  |

|                                                           | 0     | a | 0     | 0x00_0000              | 0                                      | 0x00_0000 |  |  |

| Bitstream                                                 | U     | b |       | 0x00_1000              |                                        | 0x00_0800 |  |  |

|                                                           | 1     |   | 207   | 0x01_9E00              | 213                                    | 0x00_D500 |  |  |

|                                                           | 1     |   | 208   | 0x01_A000              | 214                                    | 0x00_D600 |  |  |

| First available user data space (page aligned)            |       |   |       |                        |                                        |           |  |  |

| 1 4 0 0 /                                                 |       |   | 255   | 0x01_FE00              | 255                                    | 0x00_FF00 |  |  |

|                                                           | 2     |   | 256   | 0x02_0000              | 256                                    | 0x01_0000 |  |  |

| 2nd MultiBoot Bitstream, or available for user data space | 3     |   |       |                        |                                        |           |  |  |

| 1                                                         |       |   | 463   | 0x03_9E00              | 469                                    | 0x01_D500 |  |  |

|                                                           |       |   | 464   | 0x03_A000              | 470                                    | 0x01_D600 |  |  |

| Second available user data space (page aligned)           | 3     |   |       |                        |                                        |           |  |  |

| 1 1 0 0                                                   |       |   | 511   | 0x03_FE00              | 511                                    | 0x01_FF00 |  |  |

Table 2-4: XC3S200AN In-System Flash Memory Allocation

|                                                 |      |     | Defau | ult Addressing<br>Mode | Optional Power-of-2<br>Addressing Mode |           |  |  |

|-------------------------------------------------|------|-----|-------|------------------------|----------------------------------------|-----------|--|--|

| Allocation                                      | Sect | tor | Page  | Address                | Page                                   | Address   |  |  |

|                                                 | 0    | a   | 0     | 0x00_0000              | 0                                      | 0x00_0000 |  |  |

| Bitstream                                       | O    | b   |       | 0x00_1000              |                                        | 0x00_0800 |  |  |

| Ditstream                                       |      |     |       |                        |                                        |           |  |  |

|                                                 | 2    |     | 566   | 0x04_6C00              | 584                                    | 0x02_4800 |  |  |

|                                                 |      |     | 567   | 0x04_6E00              | 585                                    | 0x02_4900 |  |  |

| First available user data space (page aligned)  | 2    |     |       |                        |                                        |           |  |  |

| 1 400                                           |      |     | 767   | 0x05_FE00              | 767                                    | 0x02_FF00 |  |  |

| 2nd MultiBoot Bitstream, or                     | 3    |     | 768   | 0x06_0000              | 768                                    | 0x03_0000 |  |  |

| available for user data                         |      |     |       |                        |                                        |           |  |  |

| space                                           | 5    |     | 1,334 | 0x0A_6C00              | 1,352                                  | 0x05_4800 |  |  |

|                                                 |      |     | 1,335 | 0x0A_6E00              | 1,353                                  | 0x05_4900 |  |  |

| Second available user data space (page aligned) | 5    |     |       |                        |                                        |           |  |  |

|                                                 |      |     | 1,535 | 0x0B_FE00              | 1,535                                  | 0x05_FF00 |  |  |

|                                                 |      |     | 1,536 | 0x0C_0000              | 1,536                                  | 0x06_0000 |  |  |

|                                                 | 6    |     |       |                        |                                        |           |  |  |

| User data space                                 |      |     | 1,791 | 0x0D_FE00              | 1,791                                  | 0x06_FF00 |  |  |

| (sector aligned)                                |      |     | 1,792 | 0x0E_0000              | 1,792                                  | 0x07_0000 |  |  |

|                                                 | 7    |     | •••   |                        |                                        |           |  |  |

|                                                 |      |     | 2,047 | 0x0F_FE00              | 2,047                                  | 0x07_FF00 |  |  |

Table 2-5: XC3S400AN In-System Flash Memory Allocation

|                                                 |      |     | Defau | IIt Addressing<br>Mode | Optional Power-of-<br>Addressing Mode |           |  |  |

|-------------------------------------------------|------|-----|-------|------------------------|---------------------------------------|-----------|--|--|

| Allocation                                      | Sect | tor | Page  | Address                | Page                                  | Address   |  |  |

|                                                 | 0    | a   | 0     | 0x00_0000              | 0                                     | 0x00_0000 |  |  |

| Bitstream                                       | U    | b   |       | 0x00_1000              |                                       | 0x00_0800 |  |  |

| Ditstream                                       |      |     |       |                        |                                       |           |  |  |

|                                                 | 3    |     | 893   | 0x06_FA00              | 921                                   | 0x03_9900 |  |  |

|                                                 | 3    |     | 894   | 0x06_FC00              | 922                                   | 0x03_9A00 |  |  |

| First available user data space (page aligned)  |      |     |       |                        |                                       |           |  |  |

| 1 40 0 /                                        |      |     | 1,023 | 0x07_FE00              | 1,023                                 | 0x03_FF00 |  |  |

| 2nd MultiBoot Bitstream, or                     | 4    |     | 1,024 | 0x08_0000              | 1,024                                 | 0x04_0000 |  |  |

| available for user data                         |      |     | •••   |                        |                                       |           |  |  |

| space                                           | 7    |     | 1,917 | 0x0E_FA00              | 1,945                                 | 0x07_9900 |  |  |

|                                                 |      |     | 1,918 | 0x0E_FC00              | 1,946                                 | 0x07_9A00 |  |  |

| Second available user data space (page aligned) | 7    |     |       |                        |                                       |           |  |  |

| 1 40 0 /                                        |      |     | 2,047 | 0x0F_FE00              | 2,047                                 | 0x07_FF00 |  |  |

Table 2-6: XC3S700AN In-System Flash Memory Allocation

|                                                 | Sector |    | Defaul | t Addressing<br>Mode | Optional Power-of-<br>Addressing Mode |           |       |           |

|-------------------------------------------------|--------|----|--------|----------------------|---------------------------------------|-----------|-------|-----------|

| Allocation                                      |        |    | Sector |                      | Sector                                |           | Page  | Address   |

|                                                 | 0      | a  | 0      | 0x00_0000            | 0                                     | 0x00_0000 |       |           |

| Bitstream                                       | U      | b  |        | 0x00_1000            |                                       | 0x00_0800 |       |           |

| Ditstream                                       |        |    |        |                      |                                       |           |       |           |

|                                                 | 5      |    | 1,293  | 0x0A_1A00            | 1,334                                 | 0x05_3600 |       |           |

|                                                 |        |    | 1,294  | 0x0A_1C00            | 1,335                                 | 0x05_3700 |       |           |

| First available user data space (page aligned)  | 5      | !  |        | • • •                |                                       | • • •     |       |           |

| 1 400                                           |        |    | 1,535  | 0x0B_FE00            | 1,535                                 | 0x05_FF00 |       |           |

| 2nd MultiBoot Bitstream, or                     | 6      |    | 1,536  | 0x0C_0000            | 1,536                                 | 0x06_0000 |       |           |

| available for user data                         | •••    |    |        |                      |                                       | • • •     |       |           |

| space                                           | 11     |    | 2,829  | 0x16_1A00            | 2,890                                 | 0x0B_4A00 |       |           |

|                                                 |        |    |        |                      | 2,830                                 | 0x16_1C00 | 2,871 | 0x0B_4B00 |

| Second available user data space (page aligned) | 11     |    |        |                      |                                       |           |       |           |

|                                                 |        |    | 3,071  | 0x17_FE00            | 3,071                                 | 0x0B_FF00 |       |           |

|                                                 |        |    |        |                      | 3,072                                 | 0x18_0000 | 3,072 | 0x0C_0000 |

|                                                 | 12     | 12 |        | • • •                |                                       | • • •     |       |           |

|                                                 |        |    | 3,327  | 0x19_FE00            | 3,327                                 | 0x0C_FF00 |       |           |

|                                                 |        |    | 3,328  | 0x1A_0000            | 3,328                                 | 0x0D_0000 |       |           |

|                                                 | 13     | 3  |        |                      |                                       | • • •     |       |           |

| User data space (sector                         |        |    | 3,583  | 0x1B_FE00            | 3,583                                 | 0x0D_FF00 |       |           |

| aligned)                                        |        |    | 3,584  | 0x1C_0000            | 3,584                                 | 0x0E_0000 |       |           |

|                                                 | 14     | Ŀ  |        |                      |                                       | • • •     |       |           |

|                                                 |        |    | 3,839  | 0x1D_FE00            | 3,839                                 | 0x0E_FF00 |       |           |

|                                                 |        |    | 3,840  | 0x1E_0000            | 3,840                                 | 0x0F_0000 |       |           |

|                                                 | 15     | 5  |        |                      |                                       | • • •     |       |           |

|                                                 |        |    | 4,095  | 0x1F_FE00            | 4,095                                 | 0x0F_FF00 |       |           |

Table 2-7: XC3S1400AN In-System Flash Memory Allocation

|                                                 | Sector |          | Defaul | t Addressing<br>Mode | Optional Power-of-2<br>Addressing Mode |           |       |           |

|-------------------------------------------------|--------|----------|--------|----------------------|----------------------------------------|-----------|-------|-----------|

| Allocation                                      |        |          | Page   | Address              | Page                                   | Address   |       |           |

|                                                 | 0      | a        | 0      | 0x00_0000            | 0                                      | 0x00_0000 |       |           |

| Bitstream                                       | U      | b        |        | 0x00_2000            |                                        | 0x00_1000 |       |           |

| Ditstream                                       | •••    |          |        |                      |                                        |           |       |           |

|                                                 | 4      |          | 1,125  | 0x11_9400            | 1,160                                  | 0x09_1000 |       |           |

|                                                 |        |          | 1,126  | 0x11_9800            | 1,161                                  | 0x09_1200 |       |           |

| First available user data space (page aligned)  | 4      |          | •••    |                      |                                        | • • •     |       |           |

| 1 40 0 7                                        |        |          | 1,279  | 0x13_FC00            | 1,279                                  | 0x09_FE00 |       |           |

| 2nd MultiBoot Bitstream, or                     | 5      |          | 1,280  | 0x14_0000            | 1,280                                  | 0x0A_0000 |       |           |

| available for user data                         |        |          |        | • • •                |                                        |           |       |           |

| space                                           | 9      |          | 2,405  | 0x25_9400            | 2,440                                  | 0x13_1000 |       |           |

|                                                 |        |          | 2,406  | 0x25_9800            | 2,441                                  | 0x13_1200 |       |           |

| Second available user data space (page aligned) | 9      |          |        | • • •                |                                        | • • •     |       |           |

| 1 (1 . 6 6 )                                    |        |          | 2,559  | 0x27_FC00            | 2,559                                  | 0x13_FE00 |       |           |

|                                                 |        |          | 2,560  | 0x28_0000            | 2,560                                  | 0x14_0000 |       |           |

|                                                 | 10     |          |        |                      |                                        |           |       |           |

|                                                 |        |          | 2,815  | 0x2B_FC00            | 2,815                                  | 0x15_FE00 |       |           |

|                                                 | 11     |          |        |                      | 2,816                                  | 0x2C_0000 | 2,816 | 0x16_0000 |

|                                                 |        |          | •••    |                      |                                        |           |       |           |

|                                                 |        |          | 3,071  | 0x2F_FC00            | 3,071                                  | 0x17_FE00 |       |           |

|                                                 |        |          | 3,072  | 0x30_0000            | 3,072                                  | 0x18_0000 |       |           |

|                                                 | 12     | 2        | •••    |                      |                                        |           |       |           |

| User data space (sector                         |        |          | 3,327  | 0x33_FC00            | 3,327                                  | 0x19_FE00 |       |           |

| aligned)                                        |        |          | 3,328  | 0x34_0000            | 3,328                                  | 0x1A_0000 |       |           |

|                                                 | 13     | 3        |        |                      |                                        |           |       |           |

|                                                 |        |          | 3,583  | 0x37_FC00            | 3,583                                  | 0x1B_FE00 |       |           |

|                                                 |        |          | 3,584  | 0x38_0000            | 3,584                                  | 0x1C_0000 |       |           |

|                                                 | 14     | <u> </u> |        |                      |                                        |           |       |           |

|                                                 |        |          | 3,839  | 0x3B_FC00            | 3,839                                  | 0x1D_FE00 |       |           |

|                                                 |        |          | 3,840  | 0x3C_0000            | 3,840                                  | 0x1E_0000 |       |           |

|                                                 | 15     | ;        |        |                      |                                        |           |       |           |

|                                                 |        |          | 4,095  | 0x3F_FC00            | 4,095                                  | 0x1F_FE00 |       |           |

## **MultiBoot Configuration Bitstream Guidelines**

The following guidelines are recommended when storing multiple configuration files in the In-System Flash (ISF) memory.

#### Align to Flash Sector Boundaries

Spartan-3AN FPGA MultiBoot addressing is flexible enough to allow a bitstream to begin at any byte boundary. However, ideally, a Spartan-3AN FPGA MultiBoot configuration image should be aligned to a sector boundary. This way, one FPGA bitstream can be updated without affecting others in the Flash. Aligning to an ISF sector boundary provides the additional advantage of allowing independent protection or lockdown of the bitstreams.

#### Additional Memory Space Required for DCM\_WAIT

Multiple configuration images should be spaced more than 5 ms apart so that the second configuration file does not interfere with a delayed start-up following programming with the first configuration file. Start-up can be delayed by waiting for lock from one or more Digital Clock Managers (DCMs), a slow or missing STARTUP user clock, or holding the DONE pin Low.

Each DCM provides an option setting that, during configuration, causes the FPGA to wait for the DCM to acquire and lock to its input clock frequency before the DCM allows the FPGA to finish the configuration process. The lock time, which is specified in the <a href="Spartan-3AN FPGA">Spartan-3AN FPGA</a> data sheet, depends on the DCM mode, and the input clock frequency.

Even if the FPGA is waiting for one or more DCMs to lock before completing configuration, the FPGA's configuration controller continues searching for the next synchronization word. If two adjacent MultiBoot images are placed one immediately following the other, and the first FPGA bitstream contains a DCM with the DCM\_WAIT option set, then potential configuration problems can occur. If the controller sees the synchronization word in the second FPGA bitstream before completing the current configuration, it starts interpreting data from the second bitstream. However, the FPGA's configuration logic may complete the current configuration even though the FPGA has read data from the second bitstream.

**Caution!** FPGA applications that use the DCM\_WAIT option on a DCM must ensure sufficient spacing between MultiBoot configuration images!

Spacing MultiBoot bitstreams sufficiently apart in memory prevents the FPGA from ever seeing the second synchronization word. For more details, see <a href="UG332: Spartan-3">UG332: Spartan-3</a>

Generation Configuration User Guide, Chapter 14, Reconfiguration and MultiBoot.

## **User Data Storage Guidelines**

The following guidelines are recommended when storing user data in the In-System Flash (ISF) memory.

- 1. Do not intermix user data with the last page of FPGA configuration bitstream data. Intermixing user data and configuration data makes updating the FPGA bitstream more difficult.

- 2. If using the Sector Protection or Sector Lockdown features, do not intermix user data in the sectors that contain the FPGA bitstream(s).

See the "Memory Allocation Tables," page 20 for specific locations for each Spartan-3AN FPGA and for both addressing modes.

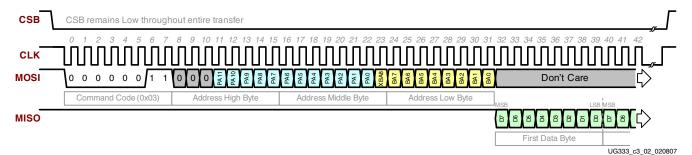

## Read Commands

The Spartan<sup>TM</sup>-3AN FPGA application reads In-System Flash (ISF) memory data either directly from the main Flash memory or from either one of the SRAM data buffers by issuing the appropriate command code. Table 3-1 summarizes and compares the various supported read commands. Some read commands offer multiple forms. One form is best for reading large blocks of contiguous data while the other form is better for reading single bytes from randomly-address locations. Typically, the commands with faster data transfer also have a longer initial latency and require one or more "don't care" bytes after sending the appropriate read command and 24-bit address.

Table 3-1: Summary of In-System Flash Memory Read Commands

| Read<br>Command                   | Best Application                                                                                          | Hex<br>Command<br>Code                   | Maximum<br>CLK<br>Frequency | Extra<br>Initial<br>Latency | Read<br>From           | Minimum<br>Read Size | Maximum<br>Read Size | Affects<br>SRAM<br>Page<br>Buffers |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------|-----------------------------|------------------------|----------------------|----------------------|------------------------------------|

| Fast Read                         | Reading a large block<br>of contiguous data, if<br>CLK frequency is<br>above 33 MHz                       | 0x0B                                     | 66                          | 8 cycles                    | Flash<br>array         | 1 byte               | Entire<br>array      | No                                 |

| Random<br>Read                    | Reading bytes from<br>randomly-addressed<br>locations, all read<br>operations at 33 MHz<br>or less        | 0x03                                     | 33                          | None                        | Flash<br>array         | 1 byte               | Entire<br>array      | No                                 |

| Page to<br>Buffer<br>Transfer     | Transfers the entire<br>contents of a selected<br>ISF memory page to<br>the specified SRAM<br>page buffer | Buffer 1<br>(0x53)<br>Buffer 2<br>(0x55) | 33                          | None                        | SRAM<br>page<br>buffer | One page             | One page             | Yes                                |

| <b>Buffer Read</b>                | Reading multiple<br>contiguous bytes from<br>the SRAM page buffer                                         | Buffer 1<br>(0xD4)<br>Buffer 2<br>(0xD6) | 66                          | 8 cycles                    | SRAM<br>page<br>buffer | 1 byte               | One page             | No                                 |

| Buffer Read<br>(Low<br>Frequency) | Randomly reading<br>bytes from the SRAM<br>page buffer                                                    | Buffer 1<br>(0xD1)<br>Buffer 2<br>(0xD3) | 33                          | None                        | SRAM<br>page<br>buffer | 1 byte               | One page             | No                                 |

#### Notes:

1. The Buffer 2 commands are not available in the XC3S50AN because it has only one SRAM page buffer.

#### **Fast Read**

The Fast Read command is best for longer, sequential read operations. This is the same command that the FPGA issues during configuration. This command is also best for code shadowing applications, where the FPGA application copies a large amount of code or data into external SRAM or DDR SDRAM for a MicroBlaze™ processor. Although it has longer initial latency than the Random Read command, the Fast Read command supports a CLK clock frequency up to 66 MHz.

The Fast Read command sequentially reads a continuous stream of data directly from Flash memory bypassing the SRAM page buffers, as shown in Figure 3-1. The command specifies an initial starting byte address in the ISF memory. The ISF memory incorporates an internal address pointer that automatically increments on every clock cycle, allowing one continuous read operation without requiring additional address sequences.

Figure 3-1: Fast Read and Random Read Commands

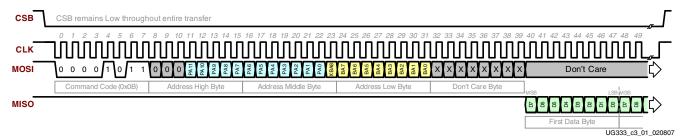

To perform a Fast Read command, summarized in Table 2-2, page 19 and shown in detail in Figure 3-2, the FPGA application must perform the following actions.

- Drive CSB Low while CLK is High or on the rising edge of CLK.

- On the falling edge of CLK, serially clock in the Fast Read command code, 0x0B, most-significant bit first.

Table 3-2: Fast Read (0x0B) Command Summary

|      | 24-bit Starting Page and Byte Address |                                                                                                                  |        |        | Don't Care | ISF Memory Data Bytes        |     |              |  |

|------|---------------------------------------|------------------------------------------------------------------------------------------------------------------|--------|--------|------------|------------------------------|-----|--------------|--|

|      | Command                               | High Address                                                                                                     |        |        |            | (most-significant bit first) |     |              |  |

| Pin  | Byte 1                                | Byte 2                                                                                                           | Byte 3 | Byte 4 | Byte 5     | Byte 6                       | ••• | Byte n+6     |  |

| MOSI | 0x0B                                  | <b>Default Addressing:</b> See Table 2-2, page 19 <b>Optional Power-of-2 Addressing:</b> See Table 10-3, page 89 |        |        | XX         | XX                           |     | XX           |  |