# Virtex-4 RocketIO Bit-Error Rate Tester

Author: Vinod Kumar Venkatavaradan

# **Summary**

This application note describes the implementation of a Virtex<sup>™</sup>-4 RocketIO<sup>™</sup> bit-error rate tester (XBERT) reference design. The XBERT reference design generates and verifies nonencoded or 8B/10B-encoded high-speed serial data on one or multiple point-to-point links between Virtex-4 RocketIO Multi-Gigabit Transceiver (MGT) ports embedded within a single Virtex-4 FPGA. This high-speed serial data is constructed in FPGA fabric using a pseudorandom bit sequence (PRBS) pattern, a clock pattern, or a user-defined pattern. The reference design provides access to the Dynamic Reconfiguration Port (DRP) on the Virtex-4 RocketIO<sup>™</sup> MGT, which enables real-time control of PMA features, such as the TX output swing, TX preemphasis, and RX equalization. The software performs dynamic switching of the PMA clocking modes to support various data rates and brute-force scanning of the PMA parameters to find the best settings.

The embedded PPC405 processor transfers control and status to the XBERT module through the General-Purpose Input/Output (GPIO) interface. The UART interfaces to the processor through an OPB interface and enables a user interface through an external RS-232 serial port. XBERT finds application in performing either synchronous MGT tests through a backplane or asynchronous tests with an external device. The reference design is built using the Embedded Development Kit (EDK) [Ref 7], and it can be easily modified or extended.

# Introduction

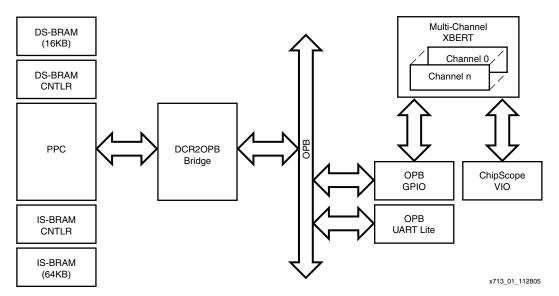

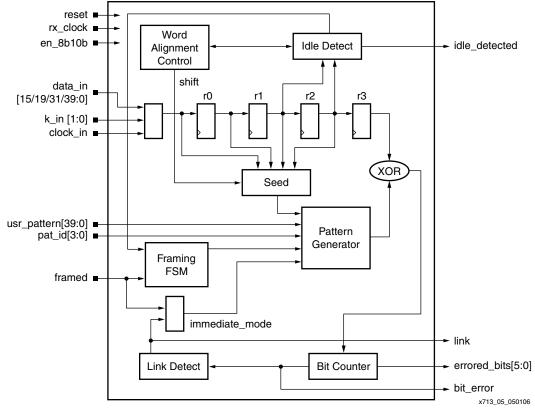

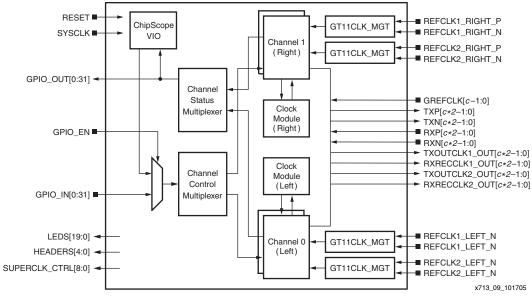

The hardware portion of the XBERT reference design includes a data plane and a control plane. Figure 1 shows the block diagram of the hardware design.

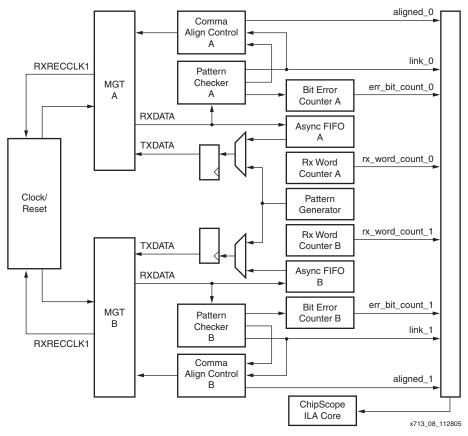

The data plane of the reference design consists of a configurable multi-channel XBERT module that generates and checks high-speed serial data transmitted and received by the MGTs. Each channel in the XBERT module consists of two MGTs (MGTA and MGTB), which physically occupy one MGT tile in the Virtex-4 FPGA. Each MGT has its own pattern checker, but both MGTs in a channel share the same pattern generator. Each channel can load a different pattern. The MGT serial rate depends on the reference clock frequency and the internal PMA divider settings. The reference design can be scaled anywhere from one channel (two MGTs) to twelve channels (twenty-four MGTs).

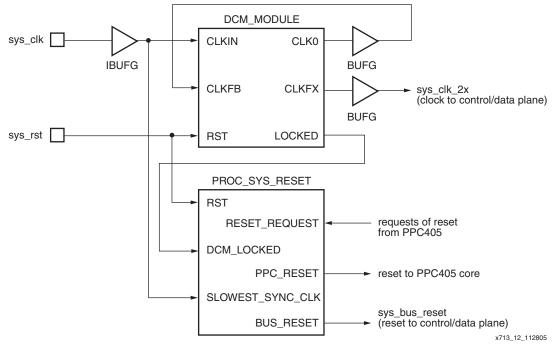

The control plane of the reference design consists of the embedded PPC405 processor core, a DCR-to-OPB bridge, a data-side block RAM controller (DS-BRAM-CNTLR), 16 Kbyte data-side block RAMs (DS-BRAM), an instruction-side block RAM controller (IS-BRAM-CNTLR), and 64 Kbyte instruction-side block RAMs (IS-BRAM). The control plane also includes an OPB bus that connects the OPB UART Lite and the OPB GPIO cores. The processor reads the status and statistical values from the XBERT module and sends control to the XBERT module via the 32-bit GPIO. The UART provides an interactive user interface for the reference design. The ChipScope<sup>™</sup> VIO is attached to the XBERT module to provide an alternative user interface.

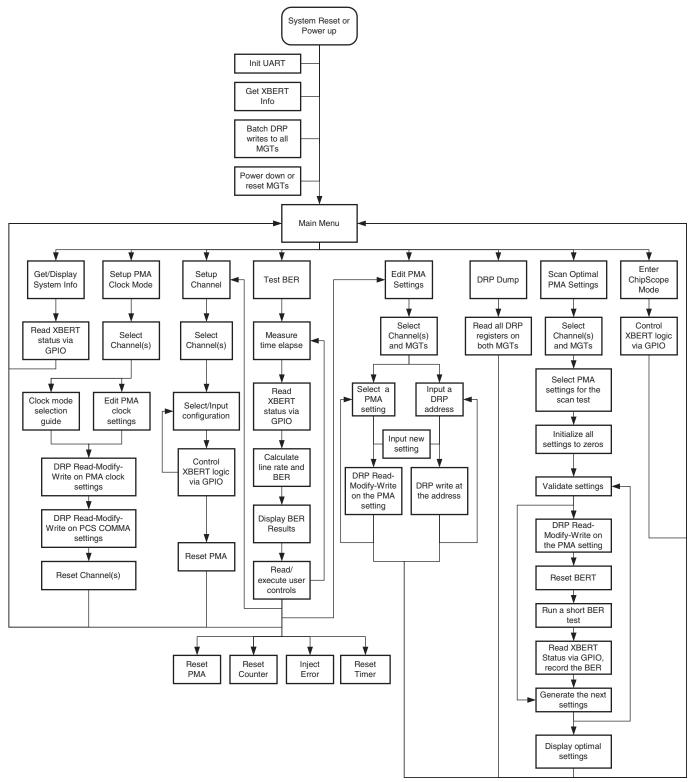

The software portion of the reference design implements functions such as GPIO drivers, UART drivers, user menu display and input parsing, line rate calculation and timer function, XBERT control and statistics, MGT DRP data structure and read-modify-write routines, decision routine on PMA clocking mode settings, and brute-force scanning on PMA analog settings.

© 2007 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and further disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>. PowerPC is a trademark of IBM Inc. All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice. NOTICE OF DISCLAIMER: Xilinx is providing this design, code, or information "as is." By providing the design, code, or information as one possible implementation of this feature, application, or standard, Xilinx makes no representation that this implementation is free from any claims of infringement. You are responsible for obtaining any rights you may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of the implementation, including but not limited to any warranties or representations that this implement and any implied warranties of merchantability or fitness for a particular purpose.

Figure 1: Hardware Block Diagram of the XBERT Reference Design

# **Features**

The key features of the Virtex-4 XBERT reference design are summarized below:

- Modular design scales from 2 to 12 channels that enable up to 24 MGTs in Virtex-4 FPGA.

- Supports all devices except for XC4VFX12 in the Virtex-4 FX family.

- Supports any valid Virtex-4 MGT serial rate.

- Supports dynamic configuration of MGTs through the Dynamic Reconfiguration Port (DRP). Supports changing the serial rate and/or clocking mode on the fly.

- Supports 16, 20, 32, and 40-bit wide MGT fabric interface.

- Support streaming or framed transmission. Frame length and inter-frame gap is configurable.

- Supports 8B/10B encoded or non-encoded patterns, including eight ITU-T standard PRBS patterns (2<sup>7</sup>-1, 2<sup>9</sup>-1, 2<sup>11</sup>-1, 2<sup>15</sup>-1, 2<sup>20</sup>-1, 2<sup>23</sup>-1, 2<sup>29</sup>-1, 2<sup>31</sup>-1), a configurable user pattern, an IDLE pattern, and a counter pattern. Each channel can load a different pattern.

- Generates three clock patterns with frequency equal to <sup>1</sup>/<sub>2</sub>, <sup>1</sup>/<sub>10</sub>, or <sup>1</sup>/<sub>20</sub> of the MGT serial rate.

- Supports BER test in both synchronous and asynchronous systems. Supports point-topoint BER test between any two MGTs on the same FPGA or on different FPGAs.

- MGTs in the left and right columns can operate fully asynchronously using different REFCLK sources.

- Supports MGT serial loopback mode. Implements a fabric loopback mode to reflect received data back to the transmission port through the FPGA fabric.

- Implements a self-synchronized pattern checker that automatically aligns and locks to an incoming pattern. Capable of testing with an external BER tester.

- Supports brute-force scanning for finding optimal PMA settings on each MGT.

- Supports 64-bit receive word and error counters for long test duration.

- Supports error injection on the transmit side to introduce a single bit error to the channel.

- Supports UART and ChipScope VIO user interfaces.

- Supports design resource reduction by removing unused patterns and/or features from the design.

# Data Plane Description

# MGT Use Model

To perform a successful bit-error rate (BER) test, some key features of the Virtex-4 MGT must be properly controlled. The XBERT reference design incorporates a subset of features provided by the Virtex-4 MGT, as listed in Table 1.

| Table 1: Deployment | of BocketIO MGT | Features in the | XBERT Reference | e Desian |

|---------------------|-----------------|-----------------|-----------------|----------|

| rable r. Deployment |                 |                 | VPELLI HOLOLOLO | c Design |

| Layer | Virtex-4 MGT Features                                                                                                | Deployment in the<br>Reference Design |

|-------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------|

|       | SERDES                                                                                                               | Yes                                   |

|       | Analog Clock and Data Recovery (CDR)                                                                                 | Yes and configurable                  |

|       | Digital oversampled receiver                                                                                         | Yes and configurable                  |

|       | Receiver signal detect, loss of signal indicator, and out-of-<br>band (OOB) support at both receiver and transmitter | No                                    |

| PMA   | Output swing adjustment and TX pre-emphasis                                                                          | Yes and configurable                  |

|       | RX continuous-time linear equalizer                                                                                  | Yes and configurable                  |

|       | On-chip AC coupling                                                                                                  | Yes and configurable                  |

|       | Use of TXOUTCLK/RXRECCLK and internal clock dividers                                                                 | Yes and configurable                  |

|       | Serial loopback and repeater mode                                                                                    | Yes and configurable                  |

|       | TX FIFO and RX Elastic Buffer                                                                                        | Yes                                   |

|       | Comma Detection and Alignment                                                                                        | Yes and configurable                  |

|       | 8B/10B Encoder/Decoder                                                                                               | Yes and configurable                  |

|       | 64B/66B Encoder/Decoder, Scrambler, Gearbox, and Block Sync                                                          | No                                    |

| PCS   | Clock Correction                                                                                                     | No                                    |

|       | Channel Bonding                                                                                                      | No                                    |

|       | Parallel loopback                                                                                                    | No                                    |

|       | CRC generation and checking                                                                                          | No                                    |

|       | Dynamic Reconfiguration Port (DRP)                                                                                   | Yes                                   |

To avoid using clock correction schemes between local and remote ports, all Virtex-4 MGTs instantiated in the reference design use the recovered clock (RXRECCLK1) to clock in the FPGA fabric on the receive side. This makes the reference design capable of performing both asynchronous and synchronous BER tests, either between two Virtex-4 MGTs or between an MGT and external BER test equipment.

The reference design supports 16, 20, 32, and 40-bit MGT fabric interfacing, as well as 32-bit and 40-bit MGT internal data width. It can transmit and receive non-encoded data or 8B/10B encoded data, depending on the choice of the MGT fabric interface and internal data width. Table 2 lists all these options.

| MGT Fabric Interface Width<br>(XBERT Data Width) | MGT Internal<br>Data Width | Encoding/<br>Decoding |

|--------------------------------------------------|----------------------------|-----------------------|

| 16                                               | 32                         | None                  |

| 16                                               | 40                         | 8B/10B                |

| 20                                               | 40                         | None                  |

| 32                                               | 32                         | None                  |

| 32                                               | 40                         | 8B/10B                |

| 40                                               | 40                         | None                  |

#### Table 2: MGT Data Width and Encoding Options in XBERT Reference Design

The reference design produces standard PRBS patterns in the serial data stream. In order to transmit and receive raw PRBS patterns, the 8B/10B or 64B/66B coding on a Virtex-4 MGT should be bypassed. Such raw PRBS patterns are considered to be most stressful to the MGT on both run length and DC balance aspects. When 8B/10B is enabled, the run length of transmission pattern is limited to a maximum 5 bits. The 8B/10B encoder and decoder also require the use of comma detection and alignment in the MGT.

Depending on the target line rate, the reference design supports using the analog CDR or the digital oversampled receiver in the MGT.

# **MGT Clocking Scheme**

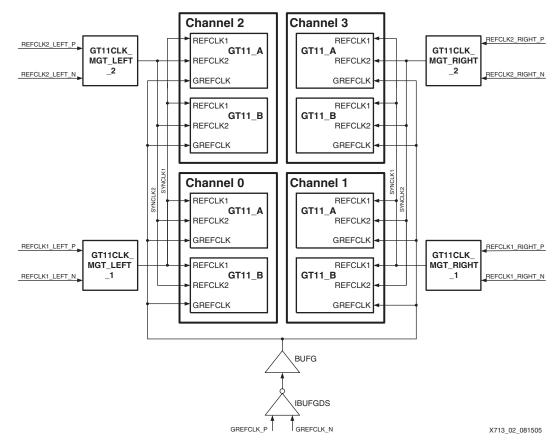

Figure 2 shows the distribution of MGT reference clocks in Virtex-4 FPGA for a typical 4-channel XBERT implementation.

Figure 2: MGT Reference Clock Distribution in XBERT Reference Design

The MGT clock distribution in Virtex-4 supports the column-based structure. A column consists of multiple MGT tiles, which contain two MGTs each. Two low-jitter reference clock trees (SYNCLK1 and SYNCLK2) driven by the GT11CLK\_MGT modules run the entire length of the column. In a tile, each PLL can select its own RX reference clock and a shared TX reference clock. There are three reference inputs to choose from: the two SYNCLKs in each column that drive the REFCLK1 and REFCLK2 inputs of the MGTs, and the global GREFCLK (for applications below 1 Gb/s).

There are two GT11CLK\_MGT inputs bonded out per column. All four GT11CLK\_MGT modules are instantiated in the XBERT reference design, named as GT11CLK\_MGT\_LEFT\_1, GT11CLK\_MGT\_LEFT\_2, GT11CLK\_MGT\_RIGHT\_1, and GT11CLK\_MGT\_RIGHT\_2. The following attributes are set on the GT11CLK\_MGT\_LEFT\_1 and GT11CLK\_MGT\_RIGHT\_1 modules so that they drive SYNCLK1 for the entire column:

SYNCLK1OUTEN = ENABLE SYNCLK2OUTEN = DISABLE

Similarly, the following attributes are set on the GT11CLK\_MGT\_LEFT\_2 and GT11CLK\_MGT\_RIGHT\_2 modules so that they drive SYNCLK2 for the entire column:

SYNCLK1OUTEN = DISABLE SYNCLK2OUTEN = ENABLE

The GREFCLK global clock is driven by a single IBUFGDS followed by a BUFG. The XBERT reference design provides a hardware configuration parameter for removing implementation of GREFCLK, thus saving the cost of this BUFG in the design.

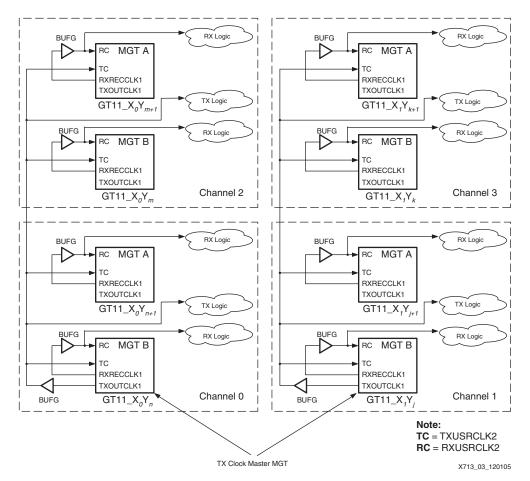

Figure 3 illustrates the MGT user clock distribution in a typical four-channel XBERT design.

Figure 3: MGT User Clock Distribution in XBERT Reference Design

RXRECCLK1 from each MGT is fed to a global clock buffer (BUFG) and is used to clock the receiving-side logic and the RXUSRCLK2 port of the same MGT. This allows asynchronous operation between TX and RX on each MGT without the need of clock correction.

TXOUTCLK1 from one MGTB in each column (called the TX Clock Master MGT) is fed to a BUFG and is used to clock the transmitting-side logic and the TXUSRCLK2 port of all MGTs in the same column. This TX clocking scheme reduces the number of BUFGs required in the design. However, it also creates the following implications:

- The MGTs in one column must operate at a single line rate, since all TXUSRCLK must have the same frequency.

- Two columns of MGTs in the FPGA can operate at two different line rates fully independently.

- The two TX Clock Master MGTs must be activated and operate properly. In particular, the TX PLL of these MGTs must lock properly to the local reference clock. Otherwise, all MGTs in the entire column could be affected.

Hardware configuration parameters allow the XBERT reference design to support the following options:

- The location of the TX Clock Master MGT can be moved to an MGTB in any channel in the same column.

- A dedicated TXOUTCLK1 can be used for each channel. This results in the TX Clock Master MGT arrangement being discarded, and allows all the channels to operate independently of each other.

- The same clock used to generate TXUSRCLK2 can drive the RXUSRCLK2. This results in the use of RXRECCLK1 being discarded and allows TX and RX to operate fully synchronously.

To reduce the number of DCMs required in the system, the reference design does not use a DCM to generate RXUSRCLK and TXUSRCLK. Instead, it uses internal PCS clock dividers to attain the proper ratio between USRCLK and USRCLK2. Note that the MGT parallel loopback option becomes invalid when internal clock dividers are used in the design. Refer to UG076, *Virtex-4 RocketIO MGT User Guide* [Ref 2] for details regarding the use of internal PCS clock dividers.

# PRBS Pattern Generation

Bit-error measurements are an important means of assessing the performance of digital transmission. It is necessary to specify reproducible test sequences that simulate real traffic as closely as possible. Reproducible test sequences are also a prerequisite to perform end-to-end measurement. Pseudo-random bit sequences (PRBS) with lengths of  $2^n - 1$  bits are the most common solution to this problem.

The PRBS pattern is produced using a linear-feedback shift register (LFSR) with appropriate feedback. If the LFSR has *n* stages, the maximum sequence length is  $2^n - 1$  bits. If the digital signal is taken directly from the output of the LFSR (non-inverted signal), the longest string of consecutive zeros is equal to n-1. If the signal is inverted, *n* consecutive zeros and n-1 consecutive ones are produced. In addition to strings of consecutive zeros and ones, the PRBS pattern contains any possible combination of zeros and ones within a string length depending on *n*.

For a given polynomial, there are two types of LFSR implementations that yields the equivalent result:

- Fibonacci (or Type-I) LFSR uses exclusive-OR (XOR) gates outside the shift register loop.

- Galois (or Type-II) LFSR uses XOR gates inside the shift register chain.

From a mathematical perspective, an implementation of multiple-stage LFSRs producing a PRBS pattern can be described by a polynomial. For example, the polynomial  $x^{15} + x^{14} + 1$  can

represent a Fibonacci LFSR implementation of a 15-stage shift register whose 14th and 15th stage outputs are added in a modulo-two addition stage, with the result fed back to the input of the first stage. The polynomial  $1 + x^{14} + x^{15}$  can represent the equivalent Galois LFSR implementation from the previous example. For LFSRs with only a few taps, the Fibonacci implementation generally achieves a faster clock speed than its Galois counterpart.

Although faster for a small number of taps, the Fibonacci implementation's performance degrades as the number of taps increases. The Galois implementation, however, sees hardly any performance loss with an increase in the number of taps. The PRBS pattern generator designed in the XBERT reference design deploys a Fibonacci (Type-I) LFSR by default, but can switch to Galois LFSR using a compilation option.

# Pattern Generator

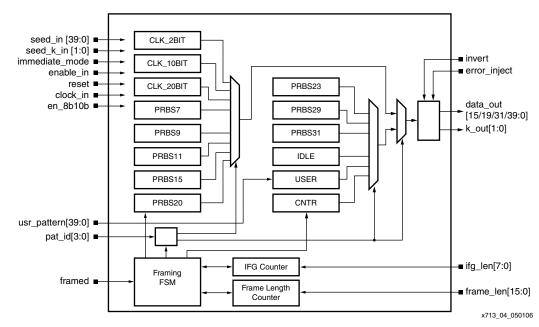

The pattern generator in the XBERT reference design generates either 16, 20, 32, or 40-bit patterns to work with a 16, 20, 32, or 40-bit MGT fabric interface. Figure 4 shows the block diagram of a pattern generator. The pattern generator contains 14 individual pattern generation blocks. The outputs of these blocks are multiplexed and registered, and they are provided as either 16, 20, 32, or 40-bit data outputs (data\_out).

Figure 4: Pattern Generator Block Diagram

Table 3 summarizes all the patterns and their respective polynomials implemented in the XBERT reference design. Note that user can remove one or more patterns from the design for resource reduction.

Table 3 summaries the use model of each pattern supported in the XBERT reference design.

The pattern generator implements seven different polynomials (PRBS9,11,15, 20, 23, 29, and 31) as specified in ITU-T Recommendation O.150 for PRBS pattern generation [Ref 8]. The International Telecommunication Union (ITU) is an international organization within the United Nations System, where governments and the private sector coordinate global telecom networks and services. ITU-T Recommendation O.150 contains general requirements applicable to instrumentation for performance measurements on digital transmission equipment. By alternating PRBS patterns, the reference design can produce different levels of line stress on the Virtex-4 RocketIO MGTs.

#### Table 3: Supported Patterns in the XBERT Reference Design

| Pat-<br>tern<br>ID | Pattern<br>Name             | Pattern/Polynomial                                             | Length of<br>Sequence<br>(bits) | Consecu-<br>tive Zeros | Notes                                                                                                                                                                                                                                                                                                             |

|--------------------|-----------------------------|----------------------------------------------------------------|---------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                  | 1/2X Clock                  | 101010                                                         | 2                               | 0                      | This pattern can be used as a clock pattern<br>whose frequency is equal to $1/2$ of the MGT<br>serial speed, generating up to a 5 GHz<br>differential clock on the transceiver serial<br>outputs. This pattern also can be used as a<br>high-frequency test pattern as defined in IEEE<br>Std 802.3-2002 [Ref 9]. |

| 1                  | 1/10X or<br>1/8X Clock      | 5 ones, 5 zeros<br><i>or</i><br>4 ones, 4 zeros                | 10 or 8                         | 5 or 4                 | This pattern can be used as a clock pattern whose frequency is equal to $1/_{10}$ or $1/_8$ of the MGT serial speed, generating up to a 1.3 GHz differential clock on the transceiver serial outputs. This pattern can also be used as a low- frequency test pattern as defined in IEEE Std 802.3-2002 [Ref 9].   |

| 2                  | 1/20X or<br>1/16X<br>Clock  | 10 ones, 10 zeros<br><i>or</i><br>8 ones, 8 zeros              | 20 or 16                        | 10 or 8                | This pattern can be used as a clock pattern whose frequency is equal to $1/_{20}$ or $1/_{16}$ of the MGT serial speed, generating up to a 645 MHz differential clock on the transceiver serial outputs.                                                                                                          |

| 3                  | 2 <sup>7</sup> – 1<br>PRBS  | x <sup>7</sup> + x <sup>6</sup> + 1<br>(non-inverted signal)   | 2 <sup>7</sup> – 1              | 7                      | Uses a proprietary polynomial that is not an ITU-T standard.                                                                                                                                                                                                                                                      |

| 4                  | 2 <sup>9</sup> – 1<br>PRBS  | x <sup>9</sup> + x <sup>5</sup> + 1<br>(non-inverted signal)   | 2 <sup>9</sup> – 1              | 8                      | ITU-T Recommendation O.150, Section 5.1 [Ref 8].                                                                                                                                                                                                                                                                  |

| 5                  | 2 <sup>11</sup> – 1<br>PRBS | x <sup>11</sup> + x <sup>9</sup> + 1<br>(non-inverted signal)  | 2 <sup>11</sup> – 1             | 10                     | ITU-T Recommendation O.150, Section 5.2 [Ref 8].                                                                                                                                                                                                                                                                  |

| 6                  | 2 <sup>15</sup> – 1<br>PRBS | x <sup>15</sup> + x <sup>14</sup> + 1<br>(non-inverted signal) | 2 <sup>15</sup> – 1             | 15                     | ITU-T Recommendation O.150, Section 5.3<br>[Ref 8]. This is one of the recommended test<br>patterns in the SONET specification.                                                                                                                                                                                   |

| 7                  | 2 <sup>20</sup> – 1<br>PRBS | $x^{20} + x^3 + 1$<br>(non-inverted signal)                    | 2 <sup>20</sup> – 1             | 19                     | ITU-T Recommendation O.150, Section 5.4<br>[Ref 8]. This is one of the recommended test<br>patterns in the SONET specification.                                                                                                                                                                                   |

| 8                  | 2 <sup>23</sup> – 1<br>PRBS | $x^{23} + x^{18} + 1$ (inverted signal)                        | 2 <sup>23</sup> – 1             | 23                     | ITU-T Recommendation O.150, Section 5.6<br>[Ref 8]. This is one of the recommended test<br>patterns in the SONET specification.                                                                                                                                                                                   |

| 9                  | 2 <sup>29</sup> – 1<br>PRBS | $x^{29} + x^{27} + 1$ (inverted signal)                        | 2 <sup>29</sup> – 1             | 29                     | ITU-T Recommendation O.150, Section 5.7 [Ref 8].                                                                                                                                                                                                                                                                  |

| 10                 | 2 <sup>31</sup> – 1<br>PRBS | $x^{31} + x^{28} + 1$ (inverted signal)                        | 2 <sup>31</sup> – 1             | 31                     | ITU-T Recommendation O.150, Section 5.8<br>[Ref 8]. This is a recommended PRBS test<br>pattern for 10 Gigabit Ethernet. See IEEE Std<br>802.3ae-2002 [Ref 10].                                                                                                                                                    |

| 11                 | Reserved                    |                                                                |                                 |                        |                                                                                                                                                                                                                                                                                                                   |

## Table 3: Supported Patterns in the XBERT Reference Design (Continued)

| Pat-<br>tern<br>ID | Pattern<br>Name    | Pattern/Polynomial                                                                                                                                                                                                                                                                                                                    | Length of<br>Sequence<br>(bits)                                               | Consecu-<br>tive Zeros | Notes                                                                                                                                                               |

|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12                 | Idle<br>Pattern    | K28.5+, K28.5-, K28.5+,<br>(if 8B/10B bypassed and XBERT<br>data width is 20 or 40 bits)<br>or<br>K28.5, D16.2, K28.5, D16.2,<br>(if 8B/10B enabled)<br>or<br>A1A1A1A1A2A21A2A2<br>( $0xF6F6F6F628282828$ )<br>(if 8B/10B bypassed and XBERT<br>data width is 16 or 32 bits)                                                          | 20 or 64                                                                      | 5                      |                                                                                                                                                                     |

| 13                 | User<br>Pattern    | Contains a repeated 16, 20, 32,<br>or 40-bit configurable pattern.<br>If 8B/10B is enabled, this pattern<br>can be configured as a<br>combination of a K-character<br>and/or a data character.<br>If 8B/10B is bypassed, the user<br>can specify any 16, 20, 32, or<br>40-bit pattern, depending on the<br>XBERT data width selected. | 1 to 40                                                                       | 0 to 39                | See Table 5 for a bit-mapping of the user<br>pattern.<br>This pattern cannot be all zeros or all ones<br>producing invalid data with an out-of-range run<br>length. |

| 14                 | Reserved           |                                                                                                                                                                                                                                                                                                                                       |                                                                               |                        |                                                                                                                                                                     |

| 15                 | Counter<br>Pattern | 0000000000,<br>111111111,<br><br>(40-bit XBERT)<br>or<br>00000000,<br>11111111,<br><br>(32-bit XBERT)<br>or<br>00000,<br>11111,<br><br>(20-bit XBERT)<br>or<br>0000,<br>1111,<br><br>(16-bit XBERT)                                                                                                                                   | Approximately<br>from 320 (in<br>20-bit XBERT)<br>to 640 (in<br>40-bit XBERT) | 16 to 40               |                                                                                                                                                                     |

| Pattern Type    | Pattern ID         | 8B/10B | Framed<br>Transmission | Comma<br>Alignment |  |

|-----------------|--------------------|--------|------------------------|--------------------|--|

| Clock patterns  | 0 to 2             | Off    | Off                    | Off                |  |

| PRBS patterns   | 2 to 10            | Off    | Off                    | Off                |  |

| r nbo patterns  | 3 to 10            | On     | On                     | On                 |  |

| Idle pattern    | 10                 | Off    | Off                    | On                 |  |

| Idle pattern    | ern 12             | On     | Oli                    |                    |  |

| Lloor pottorp   | 12                 | Off    | Off                    | Off                |  |

| User pattern 13 |                    | On     | On                     | On                 |  |

|                 | 15                 | Off Or | On                     | On                 |  |

|                 | Counter pattern 15 |        |                        | Un                 |  |

| Table 4: Use Model of Supported Patterns in the XBERT Reference Design |

|------------------------------------------------------------------------|

|------------------------------------------------------------------------|

The idle pattern (IDLE) can be any one of the following patterns depending on the data width and encoding scheme selected. An idle pattern is composed of 2-byte or 8-byte idle word. The idle word is also used to fill-in inter-frame gap in framed transmission, which requires word alignment using the comma detection and alignment circuits inside the MGT.

- 8B/10B is bypassed. The XBERT data width is 20-bit or 40-bit. The idle pattern consists of interleaving K28.5 + (0b0011111010) and K28.5 (0b1100000101) symbols. The comma pattern is configured as the K28.5 + character in this case so that the MGT data output can be 2-byte aligned.

- 8B/10B is bypassed. The XBERT data width is 16-bit or 32-bit. The idle pattern consists of the A1A1A1A1A2A2A2A2 comma pattern (0xF6F6F6F628282828) typically used in SONET applications. The MGT data output can be 4-byte aligned.

- 8B/10B is enabled. The idle pattern consists of K28.5 and D16.2. The K28.5 character is configured as the MGT comma pattern. The MGT data output can be 2-byte aligned.

The counter pattern (CNTR) consists of 16, 20, 32, or 40-bit incremental counter words and idle words, providing a traceable and predictable test pattern that differs from the PRBS pattern. The design concatenates 4-bit counter values to build up the counter word so it repeats every 16 user clock cycles. Since the framed transmission of a counter pattern requires completion of MGT comma detection and alignment, the counter pattern can be used to test comma detection and alignment functions provided by the MGTs.

The user pattern (USER) contains a repeated 16, 20, 32, or 40-bit configurable pattern. Table 5 lists the bit-mapping of the user pattern input (usr\_pattern[39:0]) to the pattern generator.

**Note:** It is advisable to choose a user pattern different from the idle pattern if transmitting an 8B/10Bencoded user pattern. Otherwise, misalignment of the MGT data output could occur.

### Table 5: User Pattern Bit Mapping

| ation<br>n[39:0]                  | Data Width<br>16 Bits                                                     |                                        |                                                                           |                                                                           | Data Width<br>20 Bits                   | Data Width<br>40 Bits                   |                                  |

|-----------------------------------|---------------------------------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------|----------------------------------|

| Bit Location<br>usr_pattern[39:0] | 8B/10B<br>ON                                                              | 8B/10B<br>OFF                          | 8B/10B<br>ON                                                              | 8B/10B<br>OFF                                                             | 8B/10B<br>OFF                           | 8B/10B<br>OFF                           |                                  |

| [0:2]                             | 8-bit 8B/10B<br>character<br>transmitted<br>second                        | 8-bit pattern<br>transmitted<br>second | 8-bit 8B/10B<br>character<br>transmitted last                             | 8-bit pattern<br>transmitted last                                         |                                         |                                         |                                  |

| [8]                               | 1 : bit[7:0] is a<br>K-character<br>0 : bit[7:0] is a<br>data character   | (Not Used)                             | 1 : bit[7:0] is a<br>K-character<br>0 : bit[7:0] is a<br>data character   | (Not Used)                                                                | 10-bit pattern<br>transmitted<br>second | 10-bit pattern transmitted last         |                                  |

| [6]                               | (Not Used)                                                                | (101 0004)                             | (Not Used)                                                                |                                                                           |                                         |                                         |                                  |

| [17:10]                           | 8-bit 8B/10B<br>character<br>transmitted first                            | 8-bit pattern<br>transmitted first     | 8-bit 8B/10B<br>character<br>transmitted third                            | 8-bit pattern<br>transmitted third                                        |                                         |                                         |                                  |

| [18]                              | 1 : bit[17:0] is a<br>K-character<br>0 : bit[17:0] is a<br>data character |                                        | 1 : bit[17:0] is a<br>K-character<br>0 : bit[17:0] is a<br>data character | (Not Used)                                                                | 10-bit pattern<br>transmitted first     | 10-bit pattern transmitted third        |                                  |

| [19]                              |                                                                           |                                        | (Not Used)                                                                |                                                                           |                                         |                                         |                                  |

| [27:20]                           |                                                                           |                                        | 8-bit 8B/10B<br>character<br>transmitted<br>second                        | 8-bit pattern<br>transmitted<br>second                                    |                                         |                                         |                                  |

| [28]                              |                                                                           | (Not Used)                             | 1 : bit[27:0] is a<br>K-character<br>0 : bit[27:0] is a<br>data character | (Not Used)                                                                |                                         | 10-bit pattern<br>transmitted<br>second |                                  |

| [29]                              | (Not Used)                                                                |                                        | (Not Used)                                                                |                                                                           | (Not Used)                              |                                         |                                  |

| [37:30]                           |                                                                           |                                        | 8-bit 8B/10B<br>character<br>transmitted first                            | 8-bit pattern<br>transmitted first                                        |                                         |                                         |                                  |

| [38]                              |                                                                           |                                        | K-characte<br>0 : bit[37:0] is                                            | 1 : bit[37:0] is a<br>K-character<br>0 : bit[37:0] is a<br>data character | (Not Used)                              |                                         | 10-bit pattern transmitted first |

| [39]                              |                                                                           |                                        | (Not Used)                                                                | (                                                                         |                                         |                                         |                                  |

```

XAPP713 (v1.1) April 18, 2007 www.BDThexiliperform/XILINX

```

The pattern generator contains a *finite state machine* (FSM) to delimit the output pattern by periodically inserting idle words. A word is either a 16, 20, 32, or 40-bit vector determined by the data width of the MGT fabric interface. Idle words — K28.5 +/– symbols, K28.5 and D16.2 characters, or A1A1A1A1A2A2A2A2 comma patterns — are used to fill *inter-frame gaps* (IFGs). The frame length and the IFG are configurable through the *frame length input* (frame\_len) and the *IFG length input* (ifg\_len) ports.

The pattern generator works in either *immediate mode* (immediate\_mode = 1) or *self-advance mode* (immediate\_mode = 0). In immediate mode, the pattern generator takes the 40-bit seed value (seed\_in) to calculate and output the pattern in three clock cycles. The output pattern is a direct-computed result of the seed value and the internal polynomial. In self-advance mode, the pattern generator calculates and updates the output pattern every clock cycle. The output pattern is an accumulated result of the initial seed value and the internal polynomial.

The pattern generator can inject a single error into the output pattern through the *error injection control port* (error\_inject). When this port is asserted High, bit 0 on the output is flipped to introduce a single bit error into the transmission. This function is implemented to self-check the integrity of the pattern generator and checker in the reference design.

The pattern generator can invert the output pattern controlled by the invert port. PRBS  $2^{15}-1$ ,  $2^{23}-1$ ,  $2^{29}-1$ , and  $2^{31}-1$  are specified as inverted patterns by default in ITU-T Recommendation 0.150. ITU-T considers the inverted patterns as being more stressful than non-inverted patterns when testing the clock recovery circuit in the network terminating devices. The pattern generator inverts these patterns by default, but allows the user to invert the patterns back in order to link up with a non-standard external BER tester.

The PRBS  $2^7 - 1$  pattern implemented in the reference design uses a proprietary polynomial because ITU-T does not provide a recommendation for this type of PRBS. The XBERT cannot link up with an external BER tester using this PRBS  $2^7 - 1$  pattern unless it uses the same polynomial.

The pattern generator contains heavy combinatorial logic (for example, a 40-bit carry chain) for parallel PRBS pattern generation that must meet the 163 MHz timing target in order to support a 6.5 Gb/s data rate.

# **Pattern Checker**

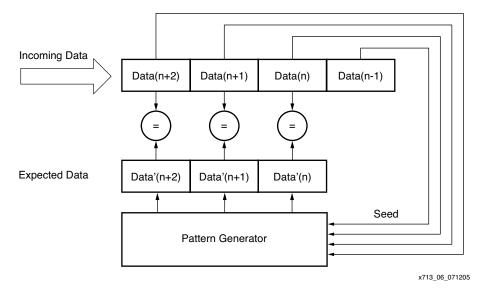

The pattern checker in the XBERT reference design can verify either 16, 20, 32, or 40-bit incoming data from a 16, 20, 32, or 40-bit MGT fabric interface. Figure 5 shows a block diagram of a pattern checker. The pattern checker contains another instance of the pattern generator that is identical to the one on the transmission side. This pattern generator generates an expected pattern to compare with the incoming data. Depending on the comparison result, the link detection and bit-error measurement are conducted at every clock cycle.

Figure 5: Pattern Checker Block Diagram

When the pattern checker receives framed data, it needs to recover the frame boundary by detecting the idle words within the incoming data IFG. Since the idle word is a 16, 20, 32, or 40-bit value, searching the idle word in the incoming data stream requires completion of word alignment. Word alignment, handled in the pattern checker, works in conjunction with the comma alignment inside the MGT. The pattern checker contains a finite state machine (FSM) that delimits the received framed pattern and holds the embedded pattern generator during the IFG.

The pattern checker works in either immediate mode (immediate\_mode = 1) or self-advance mode (immediate\_mode = 0). The pattern checker always starts in immediate mode when the link is down or reset is asserted. As illustrated in Figure 6, the pattern checker in immediate mode uses the incoming data to generate the seed value for the embedded pattern generator. The pattern generator uses the seed value to generate an output pattern in three clock cycles. This output pattern is expected to match the next incoming data.

In actual practice, several pipeline stages are introduced on the incoming data path to compensate for the three-cycle delays in the pattern generator and to meet an optimal timing target for 6.5 Gb/s operation. Therefore, the pattern checker can automatically adapt the internal state of the incoming data's polynomial to generate the expected data. The pattern checker repeats this process for every cycle until the expected data is aligned and locked on a recognized pattern in the incoming data. The process of watching for and declaring pattern match (or *link-up*) is performed by the link detection logic.

As soon as link-up is declared, the pattern checker switches to the self-advance mode. In this state, the embedded pattern generator starts to independently calculate and update the expected pattern on every clock cycle. As long as the link is up and stable, any bit error on the incoming data cannot disturb the actual output of the pattern checker, guaranteeing proper pattern verification and BER result. This self-synchronization mechanism eliminates the need of transferring a special sequence during the initialization of a BER test, and makes the reference design capable of linking with an external BER tester.

Figure 6: Self Synchronized Pattern Checker

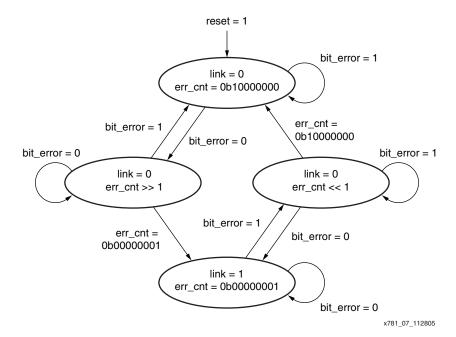

Figure 7 shows the state diagram of the link detection logic implemented in the pattern checker. The link detection logic monitors the number of bit errors in the received data at each cycle to report the link status. The logic declares a *link-up* whenever it sees error-free incoming data for seven or more consecutive clock cycles. It declares a *link-down* whenever it sees one or more bit errors at each cycle for seven or more consecutive clock cycles. The link status remains unchanged for all other conditions. The link detection logic filters out any scattered random bit errors occurring at a medium or low bit-error rate (BER) to keep the link relatively stable during a BER test.

Figure 7: Link Detection State Diagram

# Single-Channel XBERT Module

The single-channel XBERT is a self-contained module providing all necessary BER test functions, independent of the PPC405 subsystem. The single-channel XBERT module is a modular design that can be scaled to multiple channels in the FPGA fabric.

Figure 6 shows the block diagram of a single-channel XBERT module implemented in the XBERT reference design. A single-channel XBERT module consists of the following main components:

• An MGT tile containing two Virtex-4 RocketIO MGTs (MGTA and MGTB)

Both MGTs share the buffered TXUSRCLK2; therefore they must operate at the same TX data rate.

- Two pattern checkers connecting to two MGTs

- One pattern generator shared by two MGTs

- One clock/reset module generating two independent RXUSRCLK2 for two MGTs

This module contains two global clock buffers (BUFGs) for buffering RXRECCLK1 from each MGT and generating RXUSRCLK2. It also generates clock status outputs (dcm\_locked\_rx) by detecting RXRECCLK1.

• Two comma align control modules connecting to two MGTs

These modules are enabled when comma\_align\_enable is High. Each module attaches to one MGT for toggling the ENPCOMMAALIGN and ENMCOMMAALIGN ports. It indicates *aligned* and disables comma alignment on the MGT once the pattern checker indicates *link-up* and detects seven idles in the incoming data.

#### • Two bit error counters for two pattern checkers

Each counter aggregates the number of erroneous bits detected in the pattern checker into a 32-bit value. Each counter is updated at every clock cycle and can be cleared by a dedicated reset (ber\_cnt\_reset).

The XBERT reference design uses the DSP48 block in the Virtex-4 FPGA as the 32-bit counter in order to improve timing performance and save fabric resources. The user can remove the use of DSP48 by asserting a compile option.

#### • Two RX word counters for two MGTs

Each counter is a free-running 32-bit counter on the RXUSRCLK2 domain that produces a total number of received words. This counter only increases when the MGT RX PLL is locked. This number is necessary for calculating a BER. The user can issue a dedicated reset (ber\_cnt\_reset) to clear each counter.

#### • Two shallow asynchronous FIFOs for two MGTs

These FIFOs provide the fabric loopback function that reflects the incoming data back to the transmission. Each FIFO is a 16-deep asynchronous FIFO constructed using the dualport distributed RAM. The write port is clocked on RXUSRCLK2, and the read port is clocked on TXUSRCLK2. These buffers can handle phase differences (but not frequency differences) between two clocks. When fabric loopback is enabled, it requires that the incoming data be frequency-locked to the local reference clock, as in a synchronous operation.

#### Two Calibration Blocks for two MGTs

The calibration block is attached to each MGT to perform calibration and monitoring functions. The default calibration block used in this reference design is v1.4.1.

#### • One ChipScope Pro™ ILA core

This core is clocked on the RXUSRCLK2 signal of either MGTA or MGTB. Data from both MGTs and associated internal logic are multiplexed by the mgt\_sel input before being fed into the ILA core so that the selected MGT data can be displayed on ChipScope Pro Analyzer.

Figure 8: Single-Channel XBERT Module

# Multi-Channel XBERT Module

The multi-channel XBERT module contains multiple instances (channels) of the single-channel XBERT module, grouped into left and right channels using a default placement configuration. Figure 9 is a block diagram of the multi-channel XBERT module. In this example, MGTs are placed at opposite sides of the FPGA, where even channels instantiate MGTs at the left side of the FPGA, and odd channels instantiate MGTs at the right side of the FPGA.

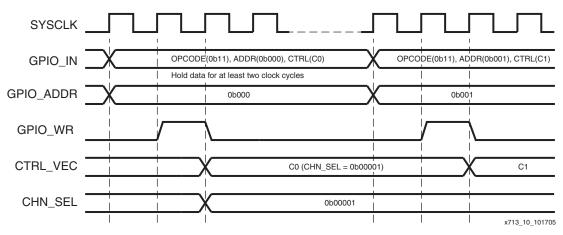

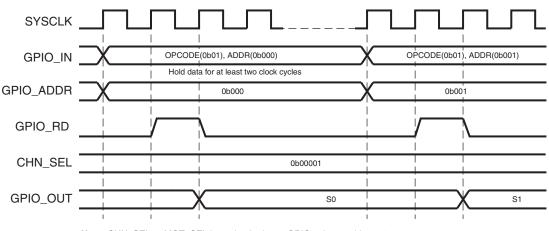

The multi-channel XBERT module provides a GPIO interface that can attach to a microprocessor (for example, PPC405 processor). The GPIO provides register-based control and status over 32 input pins and 32 output pins. To expand the number of control/status bits transferring from/to the microprocessor on the GPIO interface, multiple control/status vectors are memory mapped to the GPIO interface at different addresses.

Figure 9: Multi-Channel XBERT Module

The user-accessible ports on the multi-channel XBERT module are defined in Table 6. The GPIO interface signals (GPIO\_IN and GPIO\_OUT) use big-endian bit ordering while the remaining signals on the multi-channel XBERT module use little-endian bit ordering.

| Name                                                | Direction | Description                                                                                                                                                                                      |

|-----------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYSCLK                                              | Input     | System Clock. Typically 50Mhz.                                                                                                                                                                   |

| RESET                                               | Input     | System Reset.                                                                                                                                                                                    |

| GPIO_IN[0:31]                                       | Input     | 32-bit GPIO input from the microprocessor, synchronous to SYSCLK.                                                                                                                                |

| GPIO_OUT[0:31]                                      | Ouput     | 32-bit GPIO output to the microprocessor, synchronous to SYSCLK.                                                                                                                                 |

| GPIO_EN                                             | Input     | GPIO enable signal.                                                                                                                                                                              |

| REFCLK1_RIGHT_P,<br>REFCLK1_RIGHT_N                 | Input     | High-speed dedicated reference clock to the MGTs in the right column.                                                                                                                            |

| REFCLK2_RIGHT_P,<br>REFCLK2_RIGHT_N                 | Input     | Alternative high-speed dedicated reference clock to the MGTs in the right column.                                                                                                                |

| REFCLK1_LEFT_P,<br>REFCLK1_LEFT_N                   | Input     | High-speed dedicated reference clock to the MGTs in the left column.                                                                                                                             |

| REFCLK2_LEFT_P,<br>REFCLK2_LEFT_N                   | Input     | Alternative high-speed dedicated reference clock to the MGTs in the left column.                                                                                                                 |

| GREFCLK[ <i>c</i> -1:0] <sup>(1)</sup>              | Input     | Global reference clock to the MGT tiles used for low speed applications(<1 Gb/s).                                                                                                                |

| TXP[ <i>c</i> ∗2 − 1:0],<br>TXN[ <i>c</i> ∗2 − 1:0] | Output    | MGT differential ports that transmit serial<br>data. Each Channel outptuts two bits as<br>follows: Bit 0 is the output of MGTA in the<br>channel. Bit 1 is the output of MGTB in the<br>channel. |

| Name                                                  | Direction | Description                                                                                                                                                                                                                 |

|-------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXP[ <i>c</i> ∗ 2 – 1:0],<br>RXN[ <i>c</i> ∗ 2 – 1:0] | Input     | MGT differential ports that receive serial data.<br>Each Channel inputs two bits as follows: Bit 0<br>is the input of MGTA in the channel. Bit 1 is<br>the input of MGTB in the channel.                                    |

| TXOUTCLK1_OUT[ <i>c</i> *2 – 1:0]                     | Output    | Non-buffered TXOUTCLK1 outputs from<br>every MGTs implemented in the design. Each<br>channel outputs two bits as follows: Bit 0 is<br>the output of MGTA in the channel, and Bit 1<br>is the output of MGTB in the channel. |

| RXRECCLK1_OUT[ <i>c</i> *2 – 1:0]                     | Output    | Non-buffered RXRECCLK1 outputs from<br>every MGT implemented in the design. Each<br>channel outputs two bits as follows: Bit 0 is<br>the output of MGTA in the channel, and Bit 1<br>is the output of MGTB in the channel.  |

| TXOUTCLK2_OUT[ <i>c</i> *2 – 1:0]                     | Output    | Non-buffered TXOUTCLK2 outputs from<br>every MGTs implemented in the design. Each<br>channel outputs two bits as follows: Bit 0 is<br>the output of MGTA in the channel, and Bit 1<br>is the output of MGTB in the channel. |

| RXRECCLK2_OUT[ <i>c</i> *2 – 1:0]                     | Output    | Non-buffered RXRECCLK2 outputs from<br>every MGT implemented in the design. Each<br>channel outputs two bits as follows: Bit 0 is<br>the output of MGTA in the channel, and Bit 1<br>is the output of MGTB in the channel.  |

|                                                       | Qutout    | Bits 9 to 0 indicate the link status of all MGTs<br>implemented on the left side. Bits 1 and 0<br>correspond to the MGTB and MGTA within<br>channel 0. Bits 9 and 8 correspond to the<br>MGTB and MGTA within channel 8.    |

| LEDS[19:0]                                            | Output    | Bits 19 to 10 indicate the link status of all MGTs implemented on the right side. Bits 11 and 10 correspond to the MGTB and MGTA within channel 1. Bits 19 and 18 correspond to the MGTB and MGTA within channel 9.         |

| HEADERS[4:0]                                          | Output    | Bit 0 is the SYSCLK. Bit 1 is the GREFCLK[0].<br>Bits 2 to 4 are unused.                                                                                                                                                    |

| SUPERCLK_CTRL[8:0]                                    | Output    | Optional control outputs to the SuperClock module used in Xilinx ML42x platform.                                                                                                                                            |

#### Table 6: Interface Signals of the Multi-Channel XBERT Module (Continued)

#### Notes:

1. *c* is the number of channels implemented in the XBERT reference design.

Table 7 and Table 8 list the bit definitions of the 32-bit GPIO input (GPIO\_IN) and GPIO output (GPIO\_OUT) registers, respectively.

| Bit    | Vector Name  | Description                                                                                                                                                             |                                                                                                                                                              |  |

|--------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|        |              | Operation Code.                                                                                                                                                         |                                                                                                                                                              |  |

| [0,1]  |              | 0b11: GPIO write operation. GPIO_IN carries a control<br>vector (CTRL) at the current cycle. The address of this<br>control vector is set by ADDR at the current cycle. |                                                                                                                                                              |  |

| [0:1]  | [0:1] OPCODE | OPCODE                                                                                                                                                                  | 0b01: GPIO read operation. GPIO_OUT carries a status vector (STAT) at the next cycle. The address of this status vector is set by ADDR at the current cycle. |  |

|        |              | Others: Reserved                                                                                                                                                        |                                                                                                                                                              |  |

| [2:4]  | ADDR         | Address of the control or status vector.                                                                                                                                |                                                                                                                                                              |  |

| [5]    | N/A          | Reserved.                                                                                                                                                               |                                                                                                                                                              |  |

| [6:31] | CTRL         | 26-bit control vector transferred from the microprocessor to the data plane (the XBERT module). See Table 9 for bit definitions o this vector.                          |                                                                                                                                                              |  |

#### Table 7: Bit Definitions of the 32-bit GPIO Input (GPIO\_IN[0:31])

| Table 8: | Bit Definitions | of the 32-bit GPIO | Output (GPIO | OUT[0:31]) |

|----------|-----------------|--------------------|--------------|------------|

|          |                 |                    |              |            |

| Bit    | Vector Name | Description                                                                                    |

|--------|-------------|------------------------------------------------------------------------------------------------|

| [0:31] | STAT        | 32-bit status vector transferred from the data plane (the XBERT module) to the microprocessor. |

Table 9 defines the bits of the 26-bit control vector (CTRL) at various addresses. Table 10 defines the bits of the 32-bit status vector (STAT) at various addresses. Note that some of control and status vectors are dedicated to each MGT in a channel, while others are shared by both MGTs (MGTA and MGTB) in a channel.

| Address | Bit     | Name          | Description                                                                                                                                                                             |

|---------|---------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | [6:13]  | N/A           | Reserved                                                                                                                                                                                |

|         | [14]    | INVERT        | Sets the pattern inversion of the output pattern on<br>both MGTs in the selected channel.<br>1: Inverts the output pattern<br>0: Resumes regular output pattern                         |

|         | [15]    | BER_CNT_RESET | When asserted High, resets the counters<br>(RX_WORD_COUNT and ERR_BIT_COUNT) of<br>the selected MGT in the selected channel.                                                            |

|         | [16]    | ERROR_INJECT  | When asserted High, the rising edge of this signal triggers a single bit error being injected on both MGTs in the selected channel.                                                     |

|         |         |               | Sets the TX and/or RX polarity of the selected MGT within the selected channel.                                                                                                         |

|         | [17:18] | POLARITY      | 0b01: Reverses RXP/RXN polarity, and<br>resumes regular TXP/TXN polarity                                                                                                                |

|         |         |               | 0b10: Reverses TXP/TXN polarity, and<br>resumes regular RXP/RXN polarity                                                                                                                |

|         |         |               | 0b11: Reverses both RXP/RXN and TXP/TXN polarities                                                                                                                                      |

|         |         |               | 0b00: Resumes regular polarity on both<br>RXP/RXN and TXP/TXN                                                                                                                           |

| 0       |         | LOOPBACK      | Sets the loopback modes on both MGTs in the selected channel.                                                                                                                           |

|         | [19:21] |               | 0b000: Normal operation (no loopback)<br>0b001: Reserved                                                                                                                                |

|         | [13.21] |               | 0b010: Reserved                                                                                                                                                                         |

|         |         |               | 0b011: Activates serial loopback mode                                                                                                                                                   |

|         |         |               | 0b100: Activates the fabric loopback mode                                                                                                                                               |

|         | [22]    | POWER_DOWN    | When asserted High, deactivates fabric logic associated with the selected MGT, reducing overall power consumption.                                                                      |

|         | [23]    | PMA_RESET     | Resets the TX and RX PMA of the selected MGT within the selected channel.                                                                                                               |

|         | [24:25] | N/A           | Reserved                                                                                                                                                                                |

|         | [26:30] | CHN_SEL       | Selects the channel implemented in the multi-<br>channel XBERT module, allowing reads/writes of the<br>status/control vectors dedicated to this channel.                                |

|         | [31]    | MGT_SEL       | Selects one of the MGTs (MGTA and MGTB) in the<br>selected channel, allowing reads/writes of the<br>status/control vectors dedicated to this MGT.<br>0: Selects MGTA<br>1: Selects MGTB |

| Table | 9: | Definitions of | f the | 26-bit | Control | Vector | (GPIO | _IN[6:31]) |  |

|-------|----|----------------|-------|--------|---------|--------|-------|------------|--|

|-------|----|----------------|-------|--------|---------|--------|-------|------------|--|

| Address | Bit     | Name               | Description                                                                                                                                                                                      |

|---------|---------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | [6:21]  | DI                 | Data to write to the DRP bus on the selected MGT in the selected channel.                                                                                                                        |

|         | [22:29] | DADDR              | Sets the address for DRP read or write on the selected MGT in the selected channel.                                                                                                              |

| 1       | 30      | DWE                | Selects DRP write or read operation on the selected<br>MGT in the selected channel.<br>0: DRP read<br>1: DRP write                                                                               |

|         | 31      | DEN                | Rising edge of this signal enables DRP bus to perform a single read/write operation on the selected MGT in the selected channel.                                                                 |

|         | [6:7]   | N/A                | Reserved                                                                                                                                                                                         |

|         | [8:23]  | FRAME_LEN          | Sets the frame length of a delimited pattern in a framed transmission on both MGTs in the selected channel.                                                                                      |

|         |         |                    | The length of a frame begins from the first word following an inter-frame-gap (IFG) and ends at the last word prior to the next IFG. The length of a frame can be from one word to 65,535 words. |

|         | 24      | N/A                | Reserved                                                                                                                                                                                         |

|         | 25      | EN_8B10B           | Enable 8B/10B encoding/decoding on both MGTs in the selected channel.                                                                                                                            |

| 2       | [26:29] | PAT_ID             | Selects a pattern to generate on TX and verify on RX of both MGTs in the selected channel.                                                                                                       |

|         | [20:20] |                    | Refer to Table 3, page 8 for a list of supported patterns                                                                                                                                        |

|         | 30      | FRAMED             | Enable the framed transmission on both MGTs in the selected channel.                                                                                                                             |

|         |         |                    | This function delimits the output data with idle pattern.                                                                                                                                        |

|         | 31      | COMMA_ALIGN_ENABLE | Enable the comma alignment on both MGTs in the selected channel.                                                                                                                                 |

|         | 0.      |                    | This function requires the presence of idle pattern ir the received data.                                                                                                                        |

Table 9: Definitions of the 26-bit Control Vector (GPIO\_IN[6:31]) (Continued)

| Address | Bit     | Name              | Description                                                                                                                                                                                                                                                                                   |

|---------|---------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | [6:15]  | SUPERCLK_CTRL     | Control signals to the SuperClock module attached<br>to Xilinx ML42x platform.<br>Bit 6: Three-state control:<br>0: All signals to SuperClock<br>module are high-Z<br>1: All signals to SuperClock<br>module are enabled<br>Bit 7: MR<br>Bit 8, 9: SEL1, SEL0                                 |

|         |         |                   | Bit 10, 11, 12: M2, M1, M0<br>Bit 13, 14, 15: N2, N1, N0                                                                                                                                                                                                                                      |

|         | [16:19] | N/A               | Reserved                                                                                                                                                                                                                                                                                      |

| 3       | [20]    | CS_MGT_SEL        | Selects one of the MGTs (MGTA and MGTB) to<br>connect to ChipScope ILA.<br>0: Select MGTA<br>1: Select MGTB                                                                                                                                                                                   |

|         | [21:23] | CB_CTRL           | Control signals to the calibration block on both MGT<br>in a selected channel.<br>Bit 23: Disable the calibration block<br>Bit 22: Reserved<br>Bit 21: Reset he calibration block                                                                                                             |

|         | [24:31] | IFG_LEN           | Sets the length of the inter-frame gap (IFG) in a<br>framed transmission on both MGTs in the selected<br>channel.<br>The length of an IFG counts from the start word of a<br>IFG, and ends at the last word within the same IFG<br>The length of an IFG can be from one word to 255<br>words. |

|         | [6:11]  | N/A               | Reserved                                                                                                                                                                                                                                                                                      |

| 4       | [12:31] | USR_PATTERN_LOWER | Specify the lower 20 bits of the 40-bit user pattern o both MGTs in the selected channel                                                                                                                                                                                                      |

| 5       | [6:7]   | N/A               | Reserved                                                                                                                                                                                                                                                                                      |

| Э       | [8:31]  | CB_CTRL_EXT       | Extended calibration block control signals.                                                                                                                                                                                                                                                   |

|         | [6:11]  | N/A               | Reserved                                                                                                                                                                                                                                                                                      |

| 6       | [12:31] | USR_PATTERN_UPPER | Specify the upper 20 bits of the 40-bit user pattern of both MGTs in the selected channel                                                                                                                                                                                                     |

Table 9: Definitions of the 26-bit Control Vector (GPIO\_IN[6:31]) (Continued)

| Address | Bit     | Name          | Description                                                                                                                                                                                                                                                                                                    |

|---------|---------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | [0:7]   | BITS_PER_WORD | Indicates the XBERT data width as the number of bits<br>in a word that transmits or receives on the multi-<br>channel XBERT module. Each word can be 16, 20,<br>32, or 40 bits corresponding to the data width of the<br>MGT fabric interface.                                                                 |

|         | [8:10]  | N/A           | Reserved                                                                                                                                                                                                                                                                                                       |