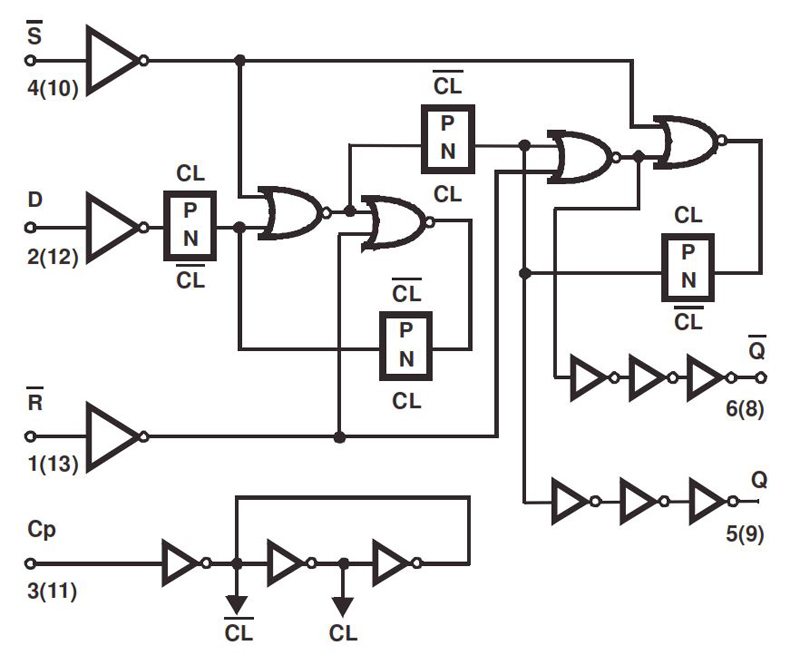

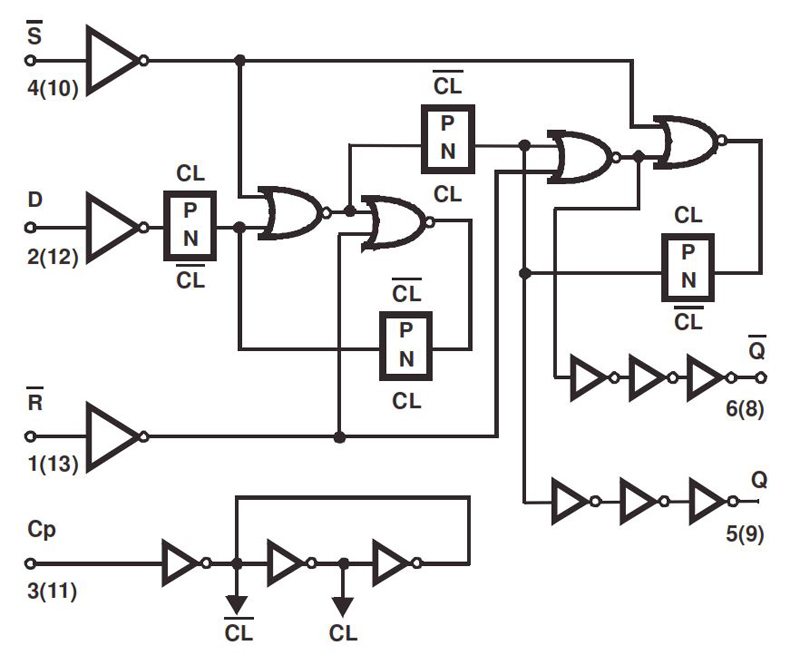

The Intersil ACTS74MS is a Radiation Hardened Dual D Flip Flop with Set(s) and Reset (R). The logic level at data input is transferred to the output during the positive transition of the clock. The Set and Reset are independent from the clock and accomplished by a low level on the appropriate input.

The ACTS74MS utilizes advanced CMOS/SOS technology to achieve high-speed operation. This device is a member of a radiation hardened, high-speed, CMOS/SOS Logic Family.

The ACTS74MS is supplied in a 14 lead Ceramic Flatpack (K suffix) or a 14 Lead Ceramic Dual-In-Line Package (D suffix).

Key Features

- Devices QML Qualified in Accordance with MIL-PRFF-38535

- Detailed Electrical and Screening Requirements are Contained in SMD# 5962-96713 and Intersil's QM Plan

- 1.25 Micron Radiation Hardened SOS CMOS

- Total Dose >300K RAD (Si)

- Single Event Upset (SEU) Immunity: <1 x 10-10 Errors/Bit/Day (Typ)

- SEU LET Threshold >100 MEV-cm2/mg

- Dose Rate Upset >1011 RAD (Si)/s, 20ns Pulse

- Dose Rate Survivability >1012 RAD (Si)/s, 20ns Pulse

- Latch-Up Free Under Any Conditions

- Military Temperature Range -55°C to +125°C

- Significant Power Reduction Compared to ALSTTL Logic

- DC Operating Voltage Range 4.5V to 5.5V

- Input Logic Levels

- VIL = 0.8V Max

- VIH = VCC/2 Min

- Input Current ≤ 1µA at VOL, VOH

- Fast Propagation Delay 20ns (Max), 13ns (Typ)

Order Information| Part Number | Package Type | Weight(g) | Pins | MSL Rating | Peak Temp (°C) | RoHS Status |

|---|

|

| ACTS74HMSR-02 | Not Applicable - Contact Us | | | N/A | | RoHS |

|

|