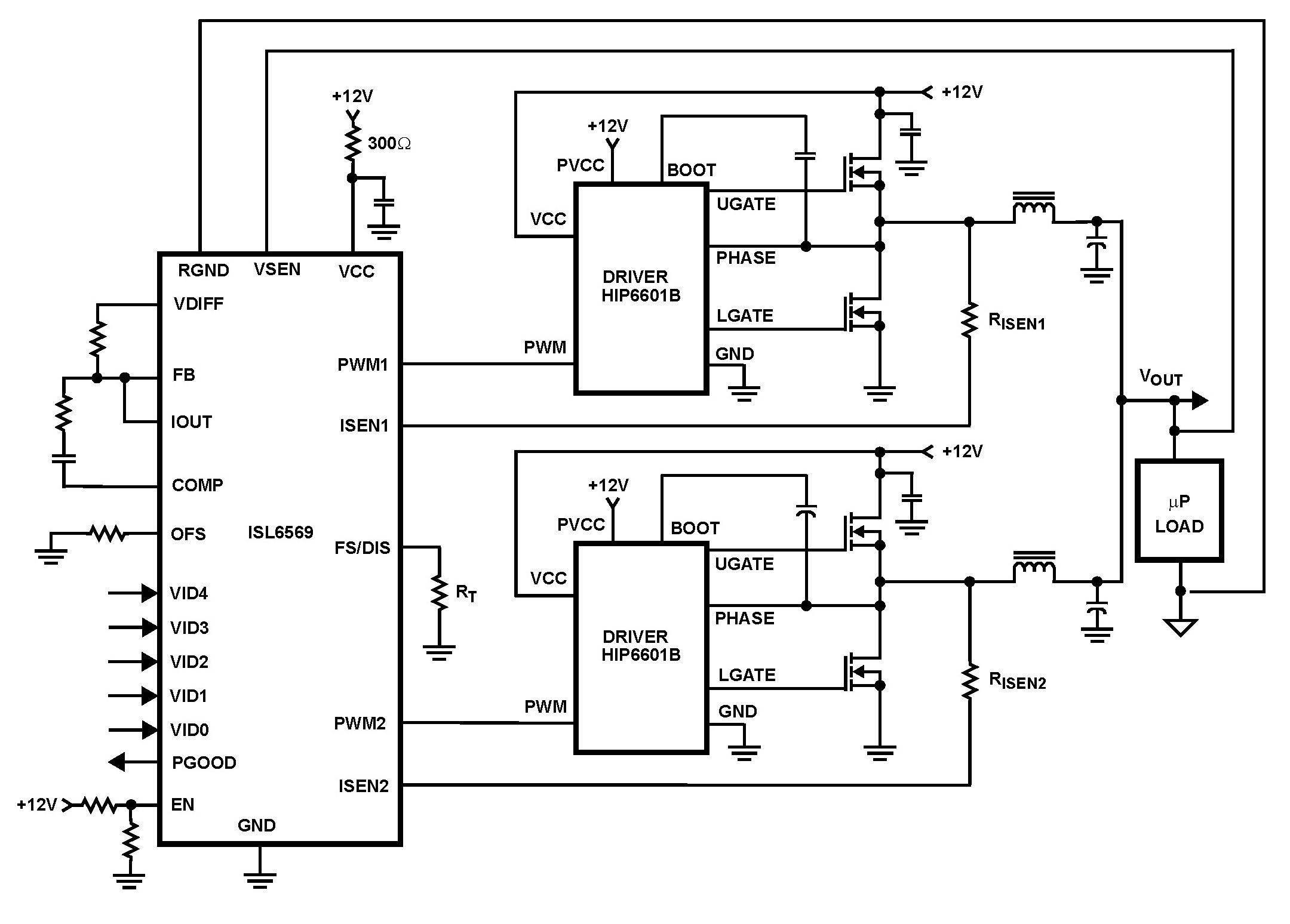

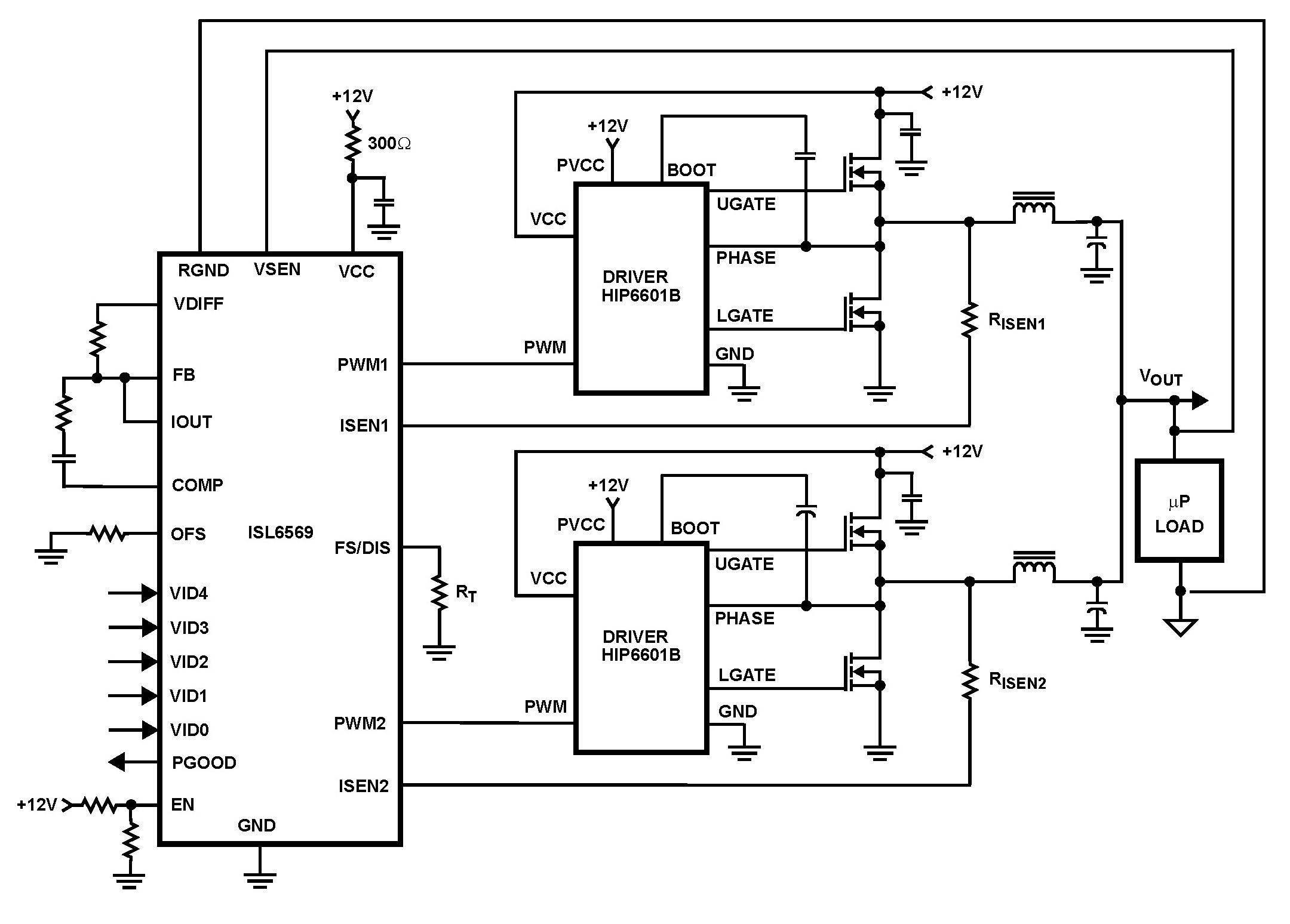

The ISL6569 provides core-voltage regulation by driving two interleaved synchronous-rectified buck-converter channels in parallel. Interleaving the channel timing results in increased ripple frequency which reduces input and output ripple currents. The reduction in ripple results in lower component cost, reduced dissipation, and a smaller implementation area.

The ISL6569 uses cost and space-saving rDS(ON) sensing for channel current balance, active voltage positioning, and over-current protection. Output voltage is monitored by an internal differential remote sense amplifier. A high-bandwidth error amplifier drives the output voltage to match the programmed 5-bit DAC reference voltage. The resulting compensation signal guides the creation of pulse width modulated (PWM) signals to control companion Intersil MOSFET drivers. The OFS pin allows direct offset of the DAC voltage from 0V to 50mV using a single external resistor. The reference and amplifiers are trimmed to ensure a system accuracy of ±1% over temperature.

Outstanding features of this controller IC include Dynamic VIDTM technology allowing seamless on-the-fly VID changing without the need of any external components. Output voltage "droop" or active voltage positioning is optional. When employed, it allows the reduction in size and cost of the output capacitors required to support load transients. A threshold-sensitive enable input allows the use of an external resistor divider for start-up coordination with Intersil MOSFET drivers or any other devices powered from a separate supply.

Superior over-voltage protection is achieved by gating on the lower MOSFET of all phases to crowbar the output voltage. An optional second crowbar on VIN, formed with an external MOSFET or SCR gated by the OVP pin, is triggered when an over-voltage condition is detected. Under-voltage conditions are detected, but PWM operation is not disrupted. Over-current conditions cause a hiccup-mode response as the controller repeatedly tries to restart. After a set number of failed startup attempts, the controller latches off. A power good logic signal indicates when the converter output is between the UV and OV thresholds.

Key Features

- Multiphase Power Conversion

- Active Channel Current Balancing

- Precision rDS(ON) Current Sharing

- Input Voltage: 12V or 5V Bias

- Precision CORE Voltage Regulation

- ±1% System Accuracy Over Temperature

- Differential Remote Output Voltage Sensing

- Programmable Reference Offset

- Microprocessor Voltage Identification Input

- 5-Bit VID Input

- 0.800V to 1.550V in 25mV Steps

- Dynamic VIDTM Technology

- Programmable Droop Voltage

- Fast Transient Recovery Time

- Over Current Protection

- Digital Soft Start

- Threshold Sensitive Enable Input

- High Ripple Frequency (160kHz to 2MHz)

- QFN Package:

- Compliant to JEDEC PUB95 MO-220 QFN - Quad Flat No Leads - Package Outline

- Near Chip Scale Package footprint, which improves PCB efficiency and has a thinner profile

- Pb-Free Available (RoHS Compliant)

Applications

- AMD Hammer Family Processor Voltage Regulator

- Low Output Voltage, High Current DC-DC Converters

- Voltage Regulator Modules

Order Information| Part Number | Package Type | Weight(g) | Pins | MSL Rating | Peak Temp (°C) | RoHS Status |

|---|

|

| ISL6569CB | 24 Ld SOIC | 0.64 | 24 | | 240 | |

|

|

| ISL6569CB-T | 24 Ld SOIC T+R | 0.64 | 24 | | 240 | |

|

|

| ISL6569CBZ | 24 Ld SOIC | 0.64 | 24 | 3 | 260 | RoHS |

|

|

| ISL6569CBZ-T | 24 Ld SOIC T+R | 0.64 | 24 | 3 | 260 | RoHS |

|

|

| ISL6569CR | 32 Ld QFN | 0.068 | 32 | | 240 | |

|

|

| ISL6569CR-T | 32 Ld QFN T+R | 0.068 | 32 | | 240 | |

|

|

| ISL6569CRZ | 32 Ld QFN | 0.068 | 32 | 3 | 260 | RoHS |

|

|

| ISL6569CRZ-T | 32 Ld QFN T+R | 0.068 | 32 | 3 | 260 | RoHS |

|

|