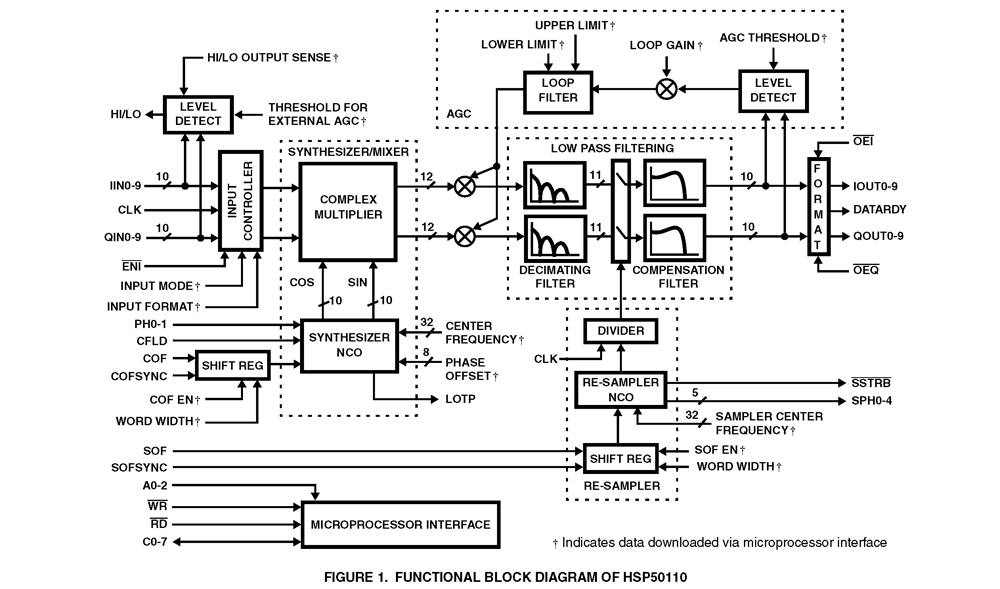

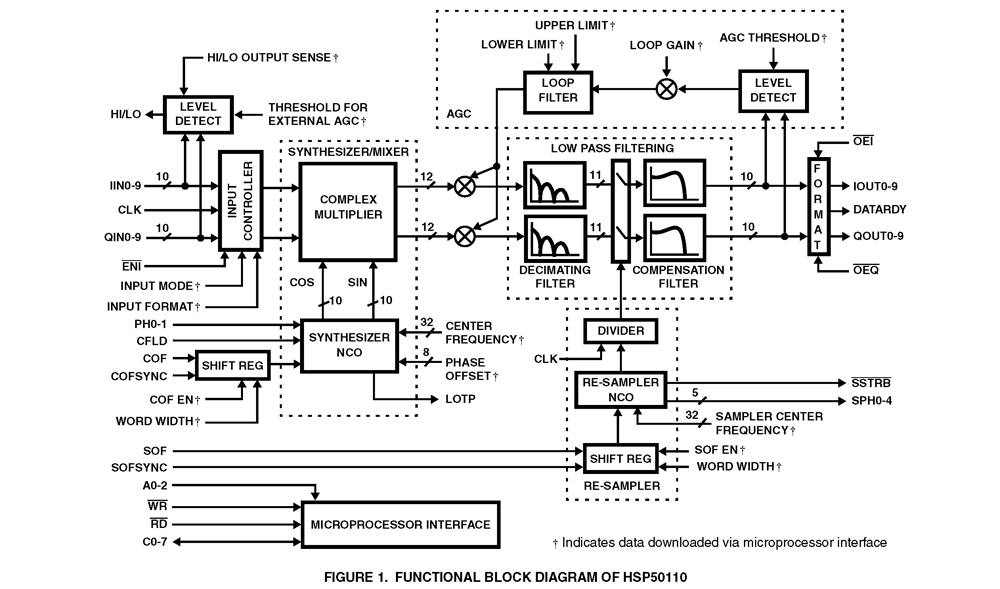

The Digital Quadrature Tuner (DQT) provides many of the functions required for digital demodulation. These functions include carrier LO generation and mixing, baseband sampling, programmable bandwidth filtering, baseband AGC, and IF AGC error detection. Serial control inputs are provided which can be used to interface with external symbol and carrier tracking loops. These elements make the DQT ideal for demodulator applications with multiple operational modes or data rates. The DQT may be used with HSP50210 Digital Costas Loop to function as a demodulator for BPSK, QPSK, 8-PSK OQPSK, FSK, FM, and AM signals.

The DQT processes a real or complex input digitized at rates up to 52 MSPS. The channel of interest is shifted to DC by a complex multiplication with the internal LO. The quadrature LO is generated by a numerically controlled oscillator (NCO) with a tuning resolution of 0.012Hz at a 52MHz sample rate. The output of the complex multiplier is gain corrected and fed into identical low pass FIR filters. Each filter is comprised of a decimating low pass filter followed by an optional compensation filter. The decimating low pass filter is a 3 stage Cascaded-Integrator-Comb (CIC) filter. The CIC filter can be configured as an integrate and dump filter or a third order CIC filter with a (sin(X)/X)3 response. Compensation filters are provided to flatten the (sin(X)/X)N response of the CIC. If none of the filtering options are desired, they may be bypassed. The filter bandwidth is set by the decimation rate of the CIC filter. The decimation rate may be fixed or adjusted dynamically by a symbol tracking loop to synchronize the output samples to symbol boundaries. The decimation rate may range from 1-4096. An internal AGC loop is provided to maintain the output magnitude at a desired level. Also, an input level detector can be used to supply error signal for an external IF AGC loop closed around the A/D.

The DQT output is provided in either serial or parallel formats to support interfacing with a variety DSP processors or digital filter components. This device is configurable over a general purpose 8-bit parallel bidirectional microprocessor control bus.

Key Features

- Input Sample Rates to 52MSPS

- Internal AGC Loop for Output Level Stability

- Parallel or Serial Output Data Formats

- 10-Bit Real or Complex Inputs

- Bidirectional 8-Bit Microprocessor Interface

- Frequency Selectivity <0.013Hz

- Low Pass Filter Configurable as Three Stage Cascaded- Integrator-Comb (CIC), Integrate and Dump, or Bypass

- Fixed Decimation from 1-4096, or Adjusted by NCO Synchronization with Baseband Waveforms

- Input Level Detection for External IF AGC Loop

- Designed to Operate with HSP50210 Digital Costas Loop

- 84 Lead PLCC

Applications

- Satellite Receivers and Modems

- Complex Upconversion/Modulation

- Tuner for Digital Demodulators

- Digital PLLs

- Related Products: HSP50210 Digital Costas Loop; A/D Products HI5703, HI5746, HI5766

- HSP50110/210EVAL Digital Demod Evaluation Board

Order Information| Part Number | Package Type | Weight(g) | Pins | MSL Rating | Peak Temp (°C) | RoHS Status |

|---|

|

| HSP50110JC-52 | 84 Ld PLCC | 7.1 | 84 | 4 | 225 | |

|

|

| HSP50110JC-52Z | 84 Ld PLCC | 7.1 | 84 | 4 | 245 | RoHS |

|

|

| HSP50110JI-52 | 84 Ld PLCC | 7.1 | 84 | 4 | 225 | |

|

|

| HSP50110JI-52Z | 84 Ld PLCC | 7.1 | 84 | 4 | 245 | RoHS |

|

|

|

|

| HSP50110/210EVAL | | | | N/A | | |

|

|