HMC1031MS8E Clock Generator with Integer-N PLL, 0.1 - 500 MHz

Together with an external loop filter and a VCXO, the HMC1031MS8E forms a complete clock generator solution targeted at low frequency jitter-cleaner and reference clock generation applications. The HMC1031MS8E features a low power integer-N divider supporting divide ratios of 1/5/10, that is controlled via external hardware pins and requires no serial port. The Integrated Phase Detector and Charge Pump are capable of operating up to 140 MHz, and a maximum VCXO input of 500 MHz ensure frequency compliance with a wide variety of system clocks and VCXOs. Additional features include Integrated Lock Detect Indicator available on a dedicated hardware pin, and a built-in Power Down Mode. The HMC1031MS8E is housed in a 8 lead MS8E SMT package.

技术特性

- Low Current Consumption:

<2 mA Typical

- High Phase Frequency

Detector Rate: 140 MHz

- Hardware Pin Programmable Clock

Multiplication Ratios: x1/ x5/ x10

- Lock Detect Indicator

- Power Down Mode (0.7 μA typical)

- 8 Lead MS8E Package: 4.8 mm x 3.0 mm

订购信息 Ordering Information

应用领域 APPLICATION

- Low Jitter Clock Generation

- Low Bandwidth Jitter Attenuation

- Low Frequency PLL

- Frequency Translation

- OCXO Frequency Multiplier

- Phase Lock clean high frequency

references to10MHz equipment

|

技术指标

| Freq. (MHz) |

Function |

Typical Phase Jitter (fsRMS) |

Phase Noise (dBc/Hz) |

Max. Ref. Freq. (MHz) |

Typical Power Consumption (W) |

Figure of Merit (Fract/Int) (dBc/Hz) |

Package |

| - / 500 |

Integer Mode PLL (x1, x5, x10) |

Defined by VCXO |

Defined by VCXO |

140 |

0.0064 |

- / -208 |

MS8 |

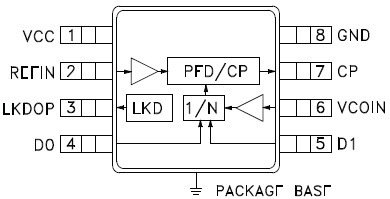

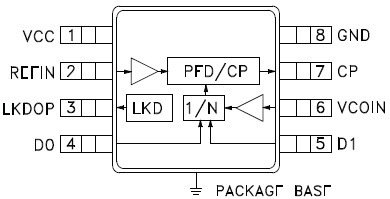

功能框图 Functional Block Diagram

|