HMC1033LP6GE High Performance, +3.3V Clock Generator, 25 - 550 MHz

The HMC1033LP6GE is a low-noise, wide-band 3.3 V clock generator IC with a fractional-N Phase Locked Loop (PLL) that features an integrated Voltage Controlled Oscillator (VCO). The device provides differential clock outputs between 25 MHz and 550 MHz range. The HMC1033LP6GE features a low noise Phase Detector (PD) and Delta- Sigma modulator, capable of operating at up to 100 MHz which permits wider loop-bandwidths and excellent spurious performance. The HMC1033LP6GE features industry leading phase noise and jitter performance, across the operating range, that enable it to improve link level jitter performance, Bit-Error-Rates (BER) and eye diagram metrics. The superior noise floor (<-162 dBc/Hz) makes the HMC1033LP6GE an ideal source for a variety of applications–such as clock references for high speed data converters, physical layer devices (PHY), serializer/deserializer (SER DES) circuits, FPGAs and processors. The HMC1033LP6GE can also be used as an LO for 10G/40G/100G optical modules and transponders, as well as primary reference clock for 10G/40G/100G line cards, and for jitter attenuation and frequency translation. The differential output of the HMC1033LP6GE can be set to either an LVPECL or LVDS compatible mode, with further ouput swing which makes the device flexible and compatible with a wide variety of signal level requirements. The output can be internally terminated to reduce component count and cost. The outputs could be terminated externally in LVPECL mode using standard methods such as resistors to ground. An Output Mute function allows the user to shut off the outputs, such as may be required for board testing or debugging. The LVPECL/LVDS, amplitude select and Output Mute function are all programmed SPI serial programming. The HMC1033LP6GE is designed to select between a Power Priority or a Performance Priority mode. The Power Priority setting reduces the current consumption of the part, whereas the Performance Priority setting improves the Jitter and Phase Noise performance. The 24 bit Delta-Sigma Modulator further enhances Hittite’s Exact Frequency Mode, which enables users to generate output frequencies with 0 Hz frequency error in many applications.

技术特性

- 3.3 V Only,

Single Supply Rail Operation

- Output Frequency Range:

25 MHz - 550 MHz

- Integer or Fractional-N mode

Frequency Translation

- Configurable LVDS-compatible or

LVPECL type Differential Outputs

- “Power Priority” and

“Performance Priority” modes

- <99 fs RMS Jitter Generation

(12 kHz-20 MHz, 350MHz, Typ)

- -163 dBc/Hz Phase Noise Floor

to Improve ADC/DAC SNR

(maximum output swing levels)

- Adjustable PLL Loop BW via

External Filter

- Output Disable/Mute Control

- Lock Detect Signal

- Exact Frequency Mode to achieve

reference frequency tuning, and

0 Hz frequency error

- 40 Lead 6x6mm SMT Package:

36mm²

应用领域 APPLICATION

- 10G/40G/100G Optical Modules,

Transponders, Line Cards

- OTN and SONET /SDH Applications

- Data Converters,

Sample Clock Generation

- Cellular/4G Infrastructure

- High Frequency Processor/FPGA Clocks

- Any Frequency Clock Rate Generation

- Low Jitter SAW Oscillator Replacement

- DDS Replacement

- Frequency Translation

- Frequency Margining

|

技术指标

| Freq. (MHz) |

Function |

Typical Phase Jitter (fsRMS) |

Phase Noise (dBc/Hz) |

Max. Ref. Freq. (MHz) |

Typical Power Consumption (W) |

Figure of Merit (Fract/Int) (dBc/Hz) |

Package |

| 25 - 550 |

High Performance, Clock Generator, +3.3V |

99 |

-163 |

350 |

0.64 |

-226 / -227 |

LP6G |

订购信息 Ordering Information

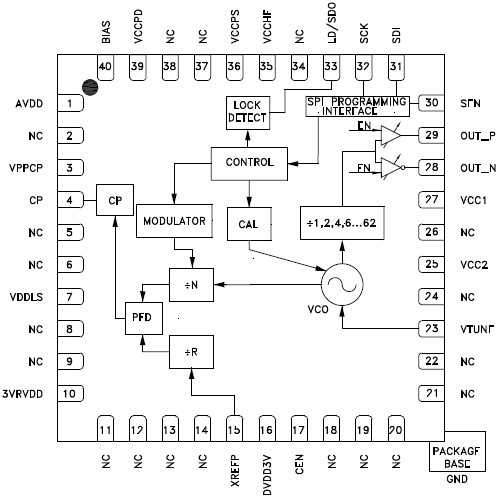

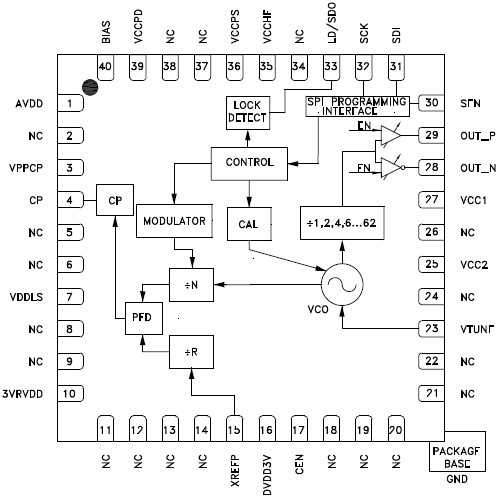

功能框图 Functional Block Diagram

|