HMC836LP6CE FRACTIONAL-N PLL WITH

INTEGRATED VCO, 3365 - 3705 MHz

The HMC836LP6CE is a fully functioned Fractional-N Phase-Locked-Loop (PLL ) with an Integrated Voltage Controlled Oscillator (VCO ). The PLL consists of an integrated low noise VCO with a tri-band output, an autocalibration subsystem for low voltage VCO tuning, a very low noise digital Phase Detector (PD), a precision controlled charge pump, a low noise reference path divider and a fractional divider. The fractional PLL features an advanced delta-sigma modulator design that allows both ultra-fine step sizes and low spurious products. The phase detector (PD) features cycle slip prevention (CS P) technology to allow faster frequency hopping times. Ultra low in-close phase noise and low spurious also allows wider loop bandwidths for faster frequency hopping and low micro-phonics.

技术特性

- RF Bandwidth: 1285 to 1415 MHz

- Ultra Low Phase Noise

-108 dBc/Hz in Band Typ.

- Figure of Merit (FOM) -227 dBc

- 24-bit Step Size, Resolution 3 Hz typ

应用领域 APPLICATION

- Cellular/4G Infrastructure

- Repeaters and Femtocells

- Communications Test Equipment

- CATV Equipment

- Phased Array Applications

- DDS Replacement

- Very High Data Rate Radios

订购信息 Ordering Information

|

技术指标

| Freq. (GHz) |

Function |

Max. PFD Freq. (MHz) |

Figure of Merit (Fract/Int) (dBc/Hz) |

Freq. Res. (Hz) |

Bias Supply |

Package |

| 10 kHz - 8 GHz |

Fractional-N with Sweeper |

75 |

-221 / -227 |

3 |

+5V @ 37mA

+3.3V @ 90mA |

LP6C |

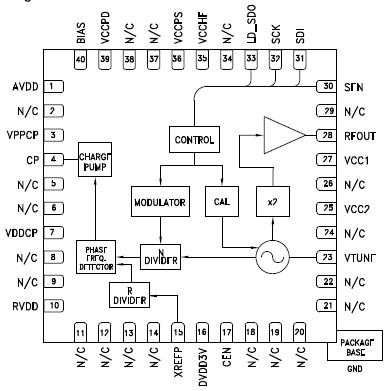

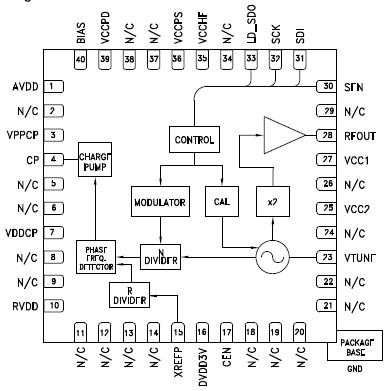

功能框图 Functional Block Diagram

|