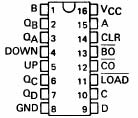

54LS192 / 74LS192 LSTTL 型递增/递减十进制计数器(双时钟)

- 内部有级联电路

- 同步操作

- 每触发器有单独的预置端

- 完全独立的清零输入端

- 典型参数:f工作频率=32MHz Pd=95mW

54LS192/74LS192说明:

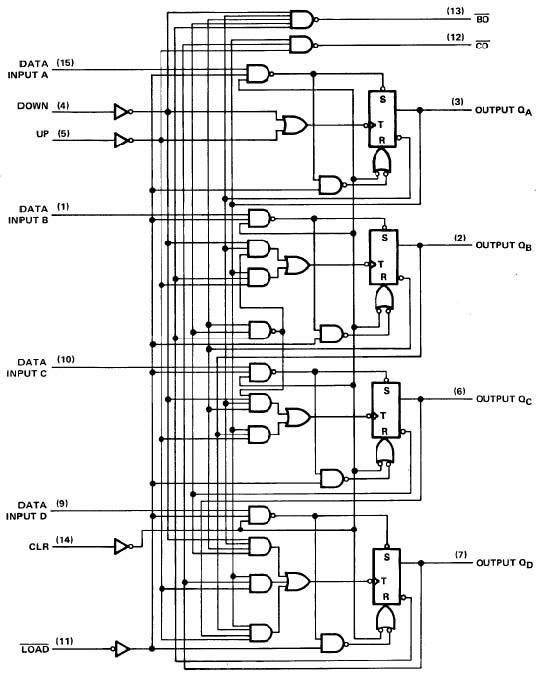

本电路复杂程度为 55个等效门,是同步可逆递增/递减 BCD计数器。本电路通过同时触发所有触发器而提供同步操作,以便在使用控制逻辑结构时,输出端的变化可相互重合。本工作方式避免了一般用异步(行波时钟)计数器所带来的

计数输出的尖峰脉冲。 四个主从触发器的输出端,由两计数(时钟)输入之一的“低”到“高”电平的过渡而被触发。计数方向在其它计数输入端为“高”时,由脉冲的计数输入

端所定。 本电路为全可编程的,当置数输入为“低”时,把所希望的数据送入数据输入端上,来把每个输出端预置到两电平之一。输出将符合独立于计数脉冲的数

据输入的改变。该特点可使电路以预置输入而简单地更改计数长度,用作 N模数分频器(除法器)。 清零输入在加高电平时,迫使所有输出端为低电平。清零功能独立于计数

输入和置数输入。清零、计数和置数等输入端都是缓冲过的,它降低了驱动的要求,这就可减少为长字所要求的时钟驱动器数等等。 本电路都设计成可被直接级联而勿需外接电路。借位和进位两输出端可级

联递增计数和递减计数两功能。借位输出在计数器下谥时,产生宽度等于递减计数输入的脉冲;同样,进位输出在计数器上谥时, 产生宽度等于递加计数输入的脉冲。因而电路可进行反馈,而很容易的被级联。即把借位输出端和进位输出端

分别反馈到后级计数器的减计数输入端和加计数输入端上即可。

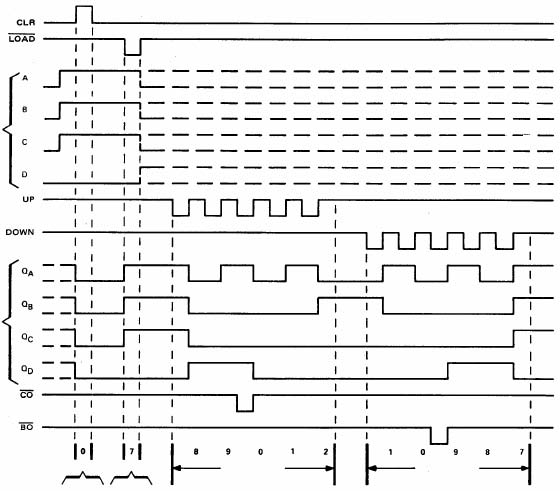

逻辑图 典型清除、计数时序

清除置数

数据

加计数减计数

输出

进位输出借位输出

时序说明:清除预置加计数减计数

功能表

| 输入 | 工作模式 | |||

| 清除 | 置数 | 加计数 | 减计数 | |

| CLR | LOAD | UP | DOWN | |

| H | × | × | × | 清除 |

| L | L | × | × | 预置 |

| L | H | H | H | 保持 |

| L | H | ↑ | H | 加计数 |

| L | H | H | ↑ | 减计数 |

H=高电平 L=低电平 ×=不定(高或低电平) ↑=由“低”→“高”电平的跃变

推荐工作条件

| 符号 | 参数名称 | 74LS192 | 54LS192 | 单位 | ||||

|---|---|---|---|---|---|---|---|---|

| 最小 | 典型 | 最大 | 最小 | 典型 | 最大 | |||

| Vcc | 电源电压 | 4.75 | 5 | 5.25 | 4.5 | 5 | 5.5 | V |

| VIH | 输入高电平电压 | 2.0 | 2.0 | V | ||||

| VIL | 输入低电平电压 | 0.8 | 0.7 | V | ||||

| IOH | 输出高电平电流 | -400 | -400 | μA | ||||

| IOL | 输出低电平电流 | 8 | 4 | mA | ||||

| fCK | 时钟频率 | 0 | 25 | 0 | 25 | MHz | ||

| tW | 脉冲宽度 | 20 | 20 | ns | ||||

| tsu | 数据建立时间 | 20 | 20 | ns | ||||

| th | 数据保持时间 | 0 | 0 | ns | ||||

| tsn | 清除无效态上升时间 | 40 | 40 | ns | ||||

| TA | 工作环境温度 | -40 | 85 | -55 | 125 | ℃ | ||

电 性 能(除特别说明外,均为全温度范围)

| 符号 | 参数名称 | 测试条件 | 74LS192 | 54LS192 | 单位 | ||||

|---|---|---|---|---|---|---|---|---|---|

| 最小 | 典型 | 最大 | 最小 | 典型 | 最大 | ||||

| VIK | 输入钳位电压 | Vcc=最小 II=-18mA | -1.5 | -1.5 | V | ||||

| VOH | 输出高电平电压 | Vcc=最小 VIL=最大 VIH=2V IOH =最大 | 2.7 | 2.5 | 3.4 | V | |||

| VOL | 输出低电平电压 | Vcc=最小 VIL =最大 VIH=2V IOL=最大 | 0.5 | 0.25 | 0.4 | V | |||

| II | 输入电流 (最大输入电压时 ) | Vcc=最大 VI=7V | 0.1 | 0.1 | mA | ||||

| IIH | 输入高电平电流 | Vcc=最大 VI=2.7V | 20 | 20 | μA | ||||

| IIL | 输入低电平电流 | Vcc=最大 VI=0.4V | -0.4 | -0.4 | mA | ||||

| IOS | 输出短路电流 | Vcc=最大 VO=0V | -20 | -100 | -20 | -100 | mA | ||

| ICC | 电源电流 | Vcc=最大(注) | 34 | 19 | 34 | mA | |||

注:测 Icc时,所有输出开路,清零和置数输入接地,所有其它输入接 4.5V。所有典型值均在 Vcc=5.0V, TA=25℃下测量得出。交流(开关)参数 (Vcc=5.0V, TA=25℃)

| 符号 | 参数名称 | 从(输入) | 到(输出) | 测试条件 | 参数值 | 单位 | ||

|---|---|---|---|---|---|---|---|---|

| 最小 | 典型 | 最大 | ||||||

| fmax | 最大时钟频率 | 25 | 32 | MHz | ||||

| tPLH | 传输延迟时间 | 加计数 | 进位输出 | 17 | 26 | ns | ||

| tPHL | 传输延迟时间 | (UP) | CO | 18 | 24 | |||

| tPLH | 传输延迟时间 | 减计数 | 借位输出 | 16 | 24 | ns | ||

| tPHL | 传输延迟时间 | (DOWN) | BO | 15 | 25 | |||

| tPLH | 传输延迟时间 | 任一计数 | Q | CL=15pF | 27 | 38 | ns | |

| tPHL | 传输延迟时间 | 30 | 47 | |||||

| tPLH | 传输延迟时间 | 置数 | Q | RL=2kΩ | 24 | 40 | ns | |

| tPHL | 传输延迟时间 | (L OAD) | 25 | 40 | ||||

| tPHL | 传输延迟时间 | 清零 CLR | Q | 23 | 35 | ns | ||