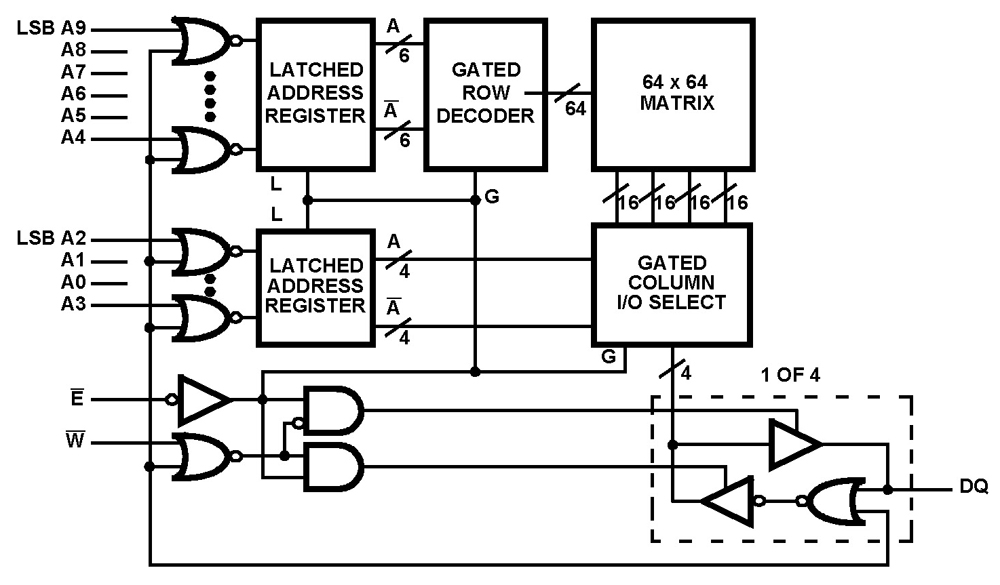

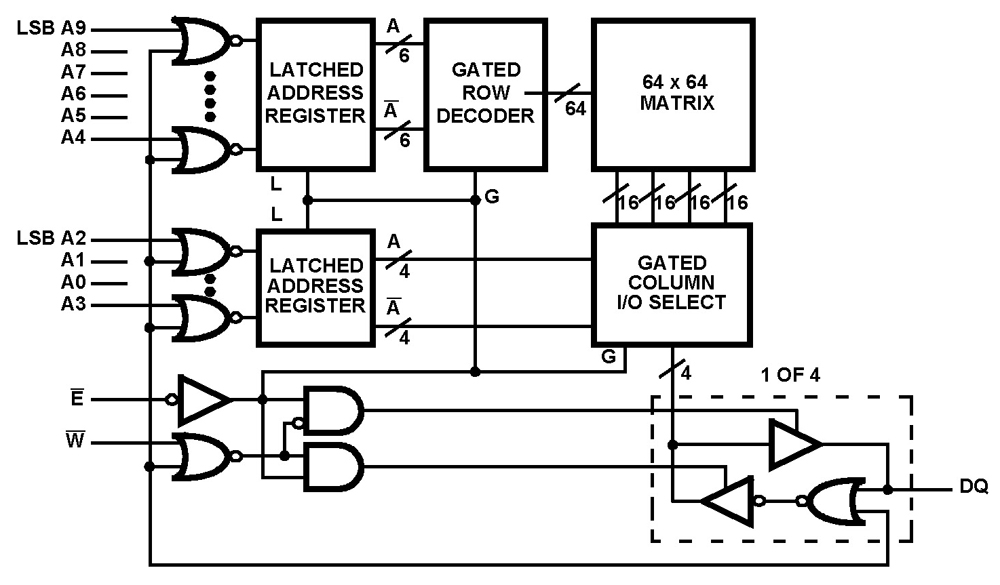

The HM-6514/883 is a 1024 x 4 static CMOS RAM fabricated using self-aligned silicon gate technology. The device utilizes synchronous circuitry to achieve high performance and low power operation. On chip latches are provided for addresses allowing efficient interfacing with microprocessor systems. The data output can be forced to a high impedance state for use in expanded memory arrays.

Gated inputs allow lower operating current and also eliminates the need for pull up or pull down resistors. The HM-6514/883 is fully static RAM and may be maintained in any state for an indefinite period of time. Data retention supply voltage and supply current are guaranteed over temperature.

Key Features

- This Circuit is Processed in Accordance to MIL-STD- 883 and is Fully Conformant Under the Provisions of Paragraph 1.2.1.

- Low Power Standby 125µW Max

- Low Power Operation 35mW/MHz Max

- Data Retention at 2.0V Min

- TTL Compatible Input/Output

- Common Data Input/Output

- Three-State Output

- Standard JEDEC Pinout

- Fast Access Time 120/200ns Max

- 18 Pin Package for High Density

- Gated Inputs - No Pull Up or Pull Down Resistors Required

- On-Chip Address Register

Order Information| Part Number | Package Type | Weight(g) | Pins | MSL Rating | Peak Temp (°C) | RoHS Status |

|---|

|

| 24502BVA | 18 Ld CERDIP | 2.6 | 18 | N/A | NA | |

|

|

| HM1-6514/883 | 18 Ld CERDIP | 2.6 | 18 | N/A | NA | |

|

|

| HM1-6514B/883 | 18 Ld CERDIP | 2.6 | 18 | N/A | NA | |

|

|