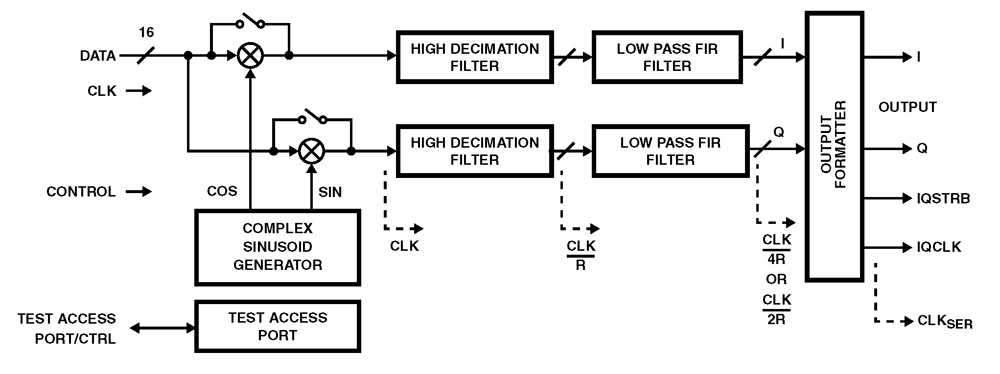

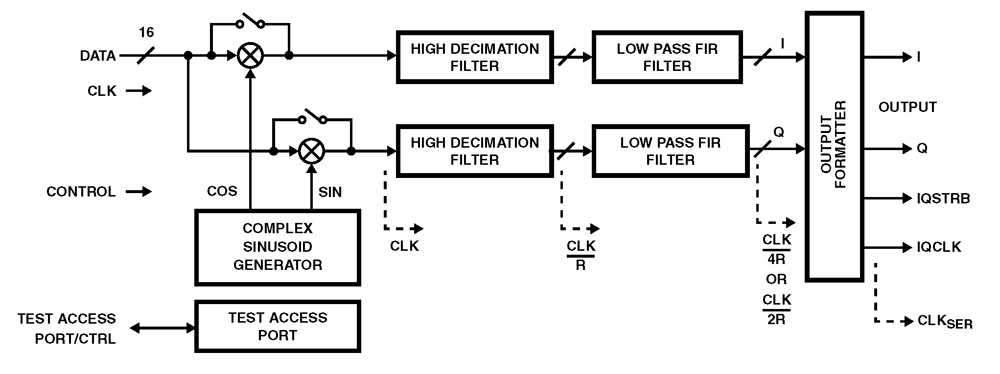

The Digital Down Converter (DDC) is a single chip synthesizer, quadrature mixer and lowpass filter. Its input data is a sampled data stream of up to 16 bits in width and up to a 75 MSPS data rate. The DDC performs down conversion, narrowband low pass filtering and decimation to produce a baseband signal. The internal synthesizer can produce a variety of signal formats. They are: CW, frequency hopped, linear FM up chirp, and linear FM down chirp. The complex result of the modulation process is lowpass filtered and decimated with identical real filters in the in-phase (I) and quadrature (Q) processing chains.

Lowpass filtering is accomplished via a High Decimation Filter (HDF) followed by a fixed Finite Impulse Response (FIR) filter. The combined response of the two stage filter results in a -3dB to -102dB shape factor of better than 1.5. The stopband attenuation is greater than 106dB. The composite passband ripple is less than 0.04dB. The synthesizer and mixer can be bypassed so that the chip operates as a single narrow band low pass filter. The chip receives forty bit serial commands as a control input. This interface is compatible with the serial I/O port available on most microprocessors.

The output data can be configured in fixed point or single precision floating point. The fixed point formats are 16, 24, 32, or 38-bit, two's complement, signed magnitude, or offset binary. The circuit provides an IEEE 1149.1 Test Access Port.

Key Features

- 75 MSPS Input Data Rate

- 16-Bit Data Input; Offset Binary or 2's Complement Format

- Spurious Free Dynamic Range Through Modulator >102dB

- Frequency Selectivity: <0.006Hz

- Identical Lowpass Filters for I and Q

- Passband Ripple: <0.04dB

- Stopband Attenuation: >104dB

- Filter -3dB to -102dB Shape Factor: <1.5

- Decimation Factors from 32 to 131,072

- IEEE 1149.1 Test Access Port

- HSP50016-EV Evaluation Board Available

Applications

- Cellular Base Stations

- Smart Antennas

- Channelized Receivers

- Spectrum Analysis

- Related Products: HI5703, HI5746, HI5766 A/Ds

Order Information| Part Number | Package Type | Weight(g) | Pins | MSL Rating | Peak Temp (°C) | RoHS Status |

|---|

|

| HSP50016-EV | Retired - Please contact us for package data | | | | | |

|

|

| HSP50016JC-52 | 44 Ld PLCC | 2.31 | 44 | 3 | 225 | |

|

|

| HSP50016JC-5296 | 44 Ld PLCC T+R | 2.31 | 44 | 4 | 225 | |

|

|

| HSP50016JC-75 | 44 Ld PLCC | 2.31 | 44 | 3 | 225 | |

|

|