LTC3831-1 - High Power Synchronous Switching Regulator Controller for DDR Memory Termination

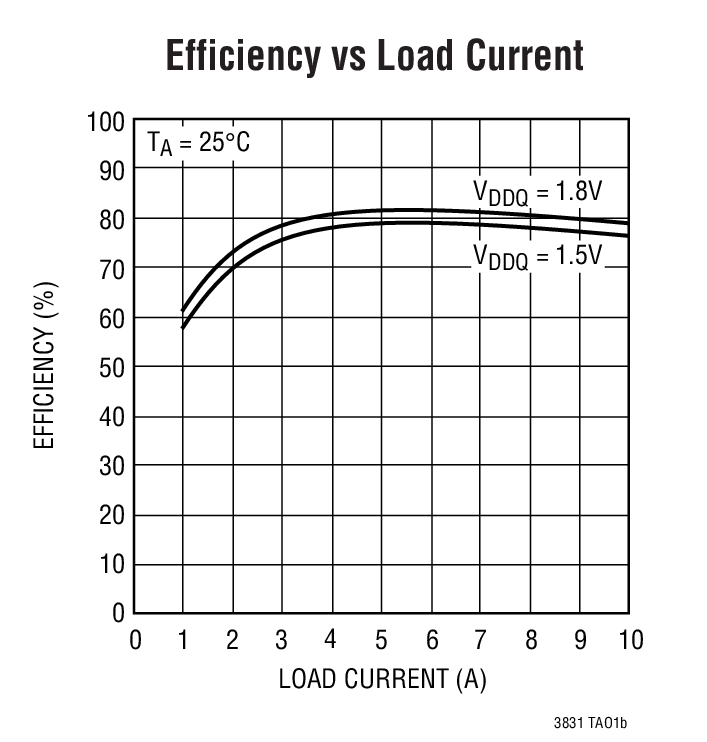

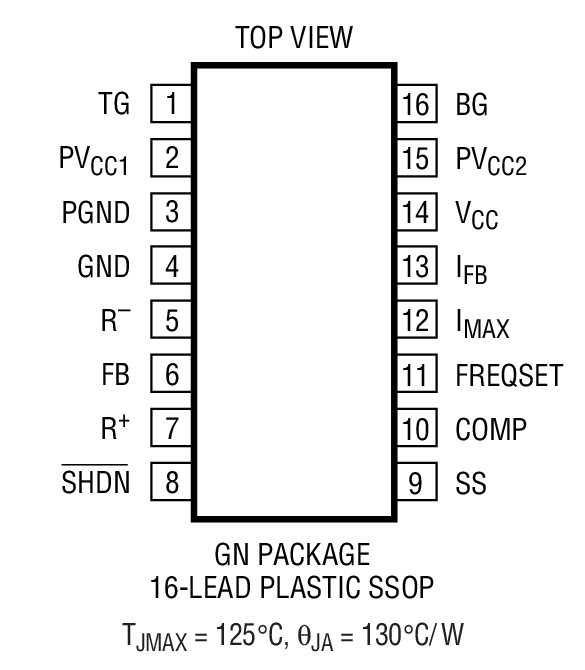

The LTC3831-1 is a high power, high efficiency switching regulator controller designed for DDR memory termination. The LTC3831-1 generates an output voltage equal to 1/2 of an external supply or reference voltage. The LTC3831-1 uses a synchronous switching architecture with N-channel MOSFETs. Additionally, the chip senses output current through the drain-source resistance of the upper N-channel FET, providing an adjustable current limit without a current sense resistor.

The LTC3831-1 operates with input supply voltage as low as 3V and with a maximum duty cycle of >91%. It includes a fixed frequency PWM oscillator for low output ripple operation. The 300kHz free-running clock frequency can be externally adjusted or synchronized with an external signal from 100kHz to above 500kHz. In shutdown mode, the LTC3831-1 supply current drops to <10µA.

Order Information

| Part Number | Package | Temp | Price(1-99) | Price (1k)* |

|---|---|---|---|---|

| LTC3831EGN-1#PBF | SSOP-16 | E | $4.29 | $2.90 |

| LTC3831EGN-1#TRPBF | SSOP-16 | E | $2.96 |