S3C2412 SAMSUNG 三星ARM微处理器

S3C2412 General Description The Samsung S3C2412 is optimized for embedded and mobile applications, featuring a 16/32-bit ARM926EJ-S core, on-chip peripherals that include a camera interface and low voltage supported by Samsung's low-power technology. This mobile processor gives designers of products such as portable GPS navigation devices, PDAs, and handheld POS a solution for reducing system cost while providing maximum flexibility.In terms of flexibility, the S3C2412 has an enhanced NAND controller that enables both small-and large-block transfers as well as 4-bit ECC support to interface with an array of NAND flash such as MLC and SLC. The Samsung processor supports a variety of memory types such as NOR, SRAM and low-power mobile SDRAM as well as removable storage like SD and MMC. The S3C2412 also supports and enhanced set of power modes to reduce power consumption.

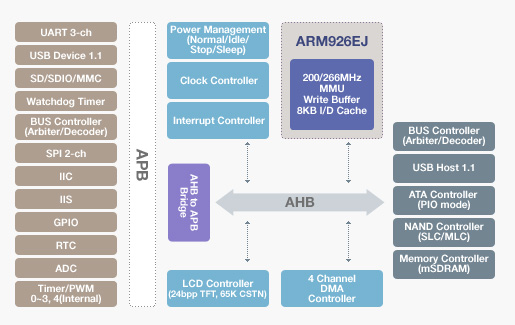

Displays are supported that range from 65K-color STN to 16M-color TFT-LCD in a variety of resolution, thus enhancing design flexibility. Samsung created the S3C2412 to power price-sensitive devices while still enabling broad features and performance. S3C2412 Block Diagram

S3C2412 Features

S3C2412 Features

- Architecture

- 16/32-bit RISC ARM926EJ-S core

- 64-way set-associative cache with I-cache (8KB) and D-cache (8KB)

- ARM's Jazelle Java technology enhanced ARM architecture

- AMBA 2.0, AHB/APB

- MMU to support WinCE, Symbian and Linux

- System Manager

- Address space : 128M bytes for each bank (total 1G bytes)

- Little/Big Endian support

- Eight memory banks :

- Six memory banks for SSMC, ROM, SRAM and others

- Two memory banks for SDRAM

- Supports a synchronous static memory-mapped devices including RAM, ROM, and flash (SLC/MLC)

- 100/133MHz address and command bus speed

- Nand Flash Bootloader

- Operating Conditions

- Internal : 1.2V

- External I/O : 3.3V

- Speed : 200MHz @ 1.2V, 266MHz @ 1.4V

- Memory : 1.8V/2.5V/3.0V memory

- On-chip Peripherals

- Power management : Normal, Idle, stop and sleep mode

- 2-port USB Host / 1- port USB Device

- SD Host interface version 1.0 & Multimedia card protocol version 2.11 compatible

- ATA Interface

- 1-ch multi-master IIC-BUS/1-ch IIS-BUS controller

- RTC with calendar function

- On-chip clock generator with PLL

- 16 bit Watch-dog timer

- 4-ch PWM timers & 1-ch internal timer

- 3-ch UART

- 2-ch SPI

- 115-bit general purpose I/O ports

- 24-ch external interrupt source

- LCD controller (up to 65K color STN and 16M color TFT) with 1-ch LCD-dedicated DMA

- 8-ch 10-bit ADC and touch screen interface

- Package

- 272-FBGA 14 x 14

Benefits

- High performance but low power consumption

- Built-in NAND Flash Bootloader

- Full set of on-chip peripherals

- Design flexibility

S3C2412 订购型号

- S3C2412R20-YO80 is Lead-free and RoHS-compliant。

- S3C2412R20-YO8D is Lead-free and RoHS-compliant。

- S3C2412R26-YO80 is Lead-free and RoHS-compliant。

- S3C2412R26-YO8D is Lead-free and RoHS-compliant。