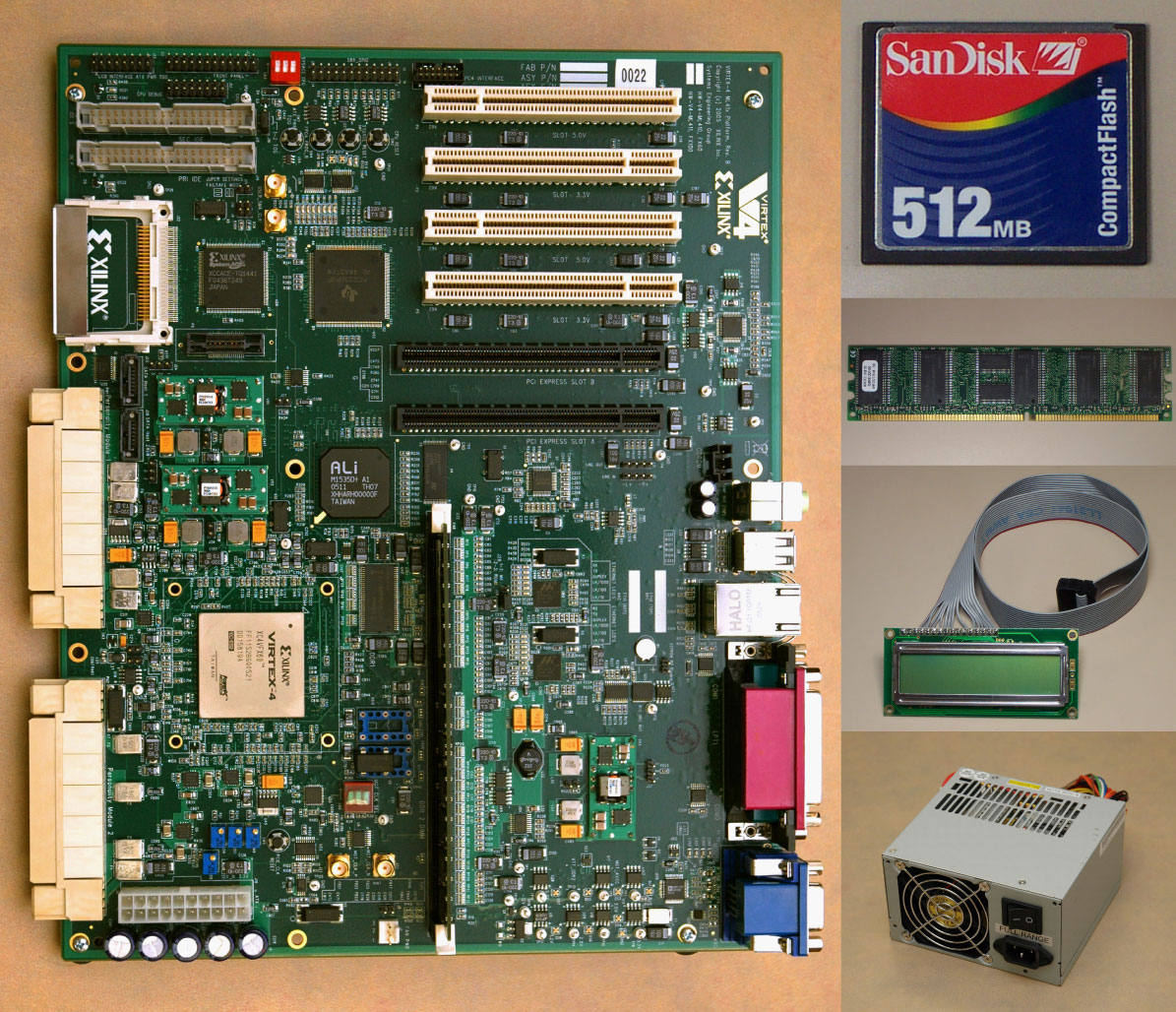

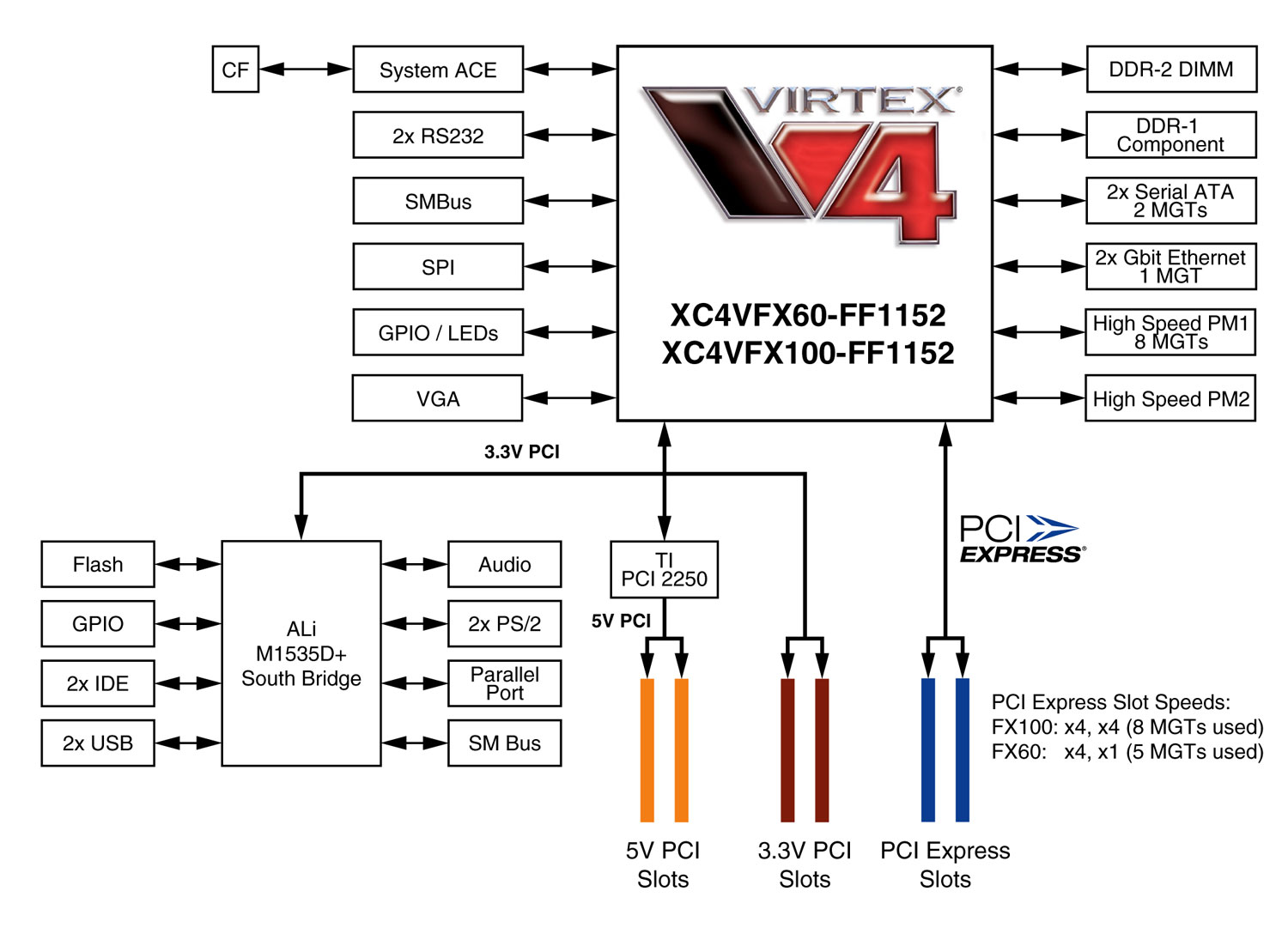

ML410

ML410 Documentation

- ML410 User Guide (PDF)

- Personality Module Interface Specification (PDF)

- ML410 Schematics (PDF)

- ML410 Gerber Plots (PDF)

PCB and Gerber Source Files

- ML410 Gerber Files (ZIP)

- ML410 PCB Files (Allegro 15.x) (ZIP)

- ML410 Schematic Files (Viewdraw) (ZIP)

| Platform Features | |

|

|

| Important Information to Read First | |

| ml410_customer_letter.pdf | Customer letter |

| ml410_pci_notice.pdf | Caution notice regarding Universal PCI add-in cards |

| ml410_readme.txt | Readme containing QuickStart information |

| QuickStarts | |

| ml410_vxworks_quickstart.pdf | Boot from CompactFlash card and begin using VxWorks Presents VxWorks functionality using a target shell |

| ml410_standalone_apps_quickstart.pdf | Boot the ACE-Loader Stand-Alone Application from the CompactFlash card |

| 8.2i Overview & Setup | |

| ml410_overview_setup.pdf | Gives an overview of the hardware and software and shows how to set up the ML410 and the equipment used in the QuickStarts. Networking, software tools, and terminal program setups are shown |

| EDK 8.2i SP1 Reference Designs and Tutorials BSB Designs | Dual Processor Designs |

||

| BSB Designs BSB 1: BSB | Stand-Alone | VxWorks 6.3 | VxWorks 5.5 | Linux 2.4 | RGMII BSB 2: DDR2 | VxWorks 6.3 | VxWorks 5.5 | SGMII | SGMII VxWorks 6.3 |

||

| ml410_bsb_design.zip | An EDK 8.2i SP1 hardware design generated with Base System Builder (BSB) | |

EDK IP:

|

|

|

| ml410_bsb_design_creation.pdf | Tutorial on how to use the EDK Base System Builder to create and use the ml410_bsb_design | |

| BSB 1: Stand-Alone | ||

| ml410_bsb_standalone_apps.zip | BSB Standalone Apps design, including BIT, ELF and ACE files. Contains the results of running the tutorial flow | |

| ml410_bsb_standalone_apps_overlay.zip | BSB Standalone Apps overlay source files, including BIT, ELF and ACE files | |

| ml410_bsb_standalone_apps_bit_elf_ace.zip | BIT, ELF, and ACE files for the stand-alone applications | |

| ml410_bsb_standalone_apps.pdf | Tutorial on how to compile and download the stand-alone applications to test board functionality | |

| BSB 1: Workbench 2.5/VxWorks 6.3 (EDK 8.2i SP2) | ||

| ml410_bsb_vxworks63.zip | BSB generated ML410 design with Workbench 2.5 VxWorks design files. Contains the results of running the tutorial flow | |

| ml410_bsb_vxworks63_overlay.zip | BSB generated ML410 overlay source files with VxWorks and updated XMP and MSS files | |

| ml410_bsb_vxworks63_bit_elf_ace.zip |

Contains EDK 8.2i SP2 VxWorks 6.3 ELF and ACE file, built with the existing EDK 8.2i SP1 bitstream | |

| ml410_bsb_vxworks63_bsp.zip |

Provides a pre-built Workbench 2.5 vxWorks BSP generated by EDK 8.2i SP2 | |

| ml410_bsb_vxworks63_proj.zip |

Provides the pre-built Workbench 2.5 vxWorks project used to create the VxWorks 6.3 system image | |

| ml410_bsb_vxworks63_bsp_proj_creation.pdf | Tutorial on how to start with an EDK hardware design and re-create the pre-built VxWorks BSP and project for the BSB design. Also covers VxWorks system image creation and using the Workbench tools | |

| BSB 1: Tornado 2.2/VxWorks 5.5 | ||

| ml410_bsb_vxworks.zip | BSB generated ML410 design with VxWorks design files. Contains the results of running the tutorial flow | |

| ml410_bsb_vxworks_overlay.zip | BSB generated ML410 overlay source files with VxWorks and updated XMP and MSS files | |

| ml410_bsb_vxworks_bit_elf_ace.zip |

Contains EDK 8.2i SP1 / ISE 8.2i SP2 bit and ACE files, along with a VxWorks 5.5 ELF file | |

| ml410_bsb_vxworks_bsp.zip |

Provides a pre-built Tornado 2.2.1 VxWorks BSP generated by EDK 8.2i SP1. (Place in $WIND_BASE\target\config) | |

| ml410_bsb_vxworks_proj.zip |

Provides the pre-built Tornado 2.2.1 VxWorks project used to create the VxWorks 5.5 system image. (Place in $WIND_BASE\target\proj) | |

| ml410_bsb_vxworks_bsp_proj_creation.pdf | Tutorial on how to start with an EDK hardware design and re-create the pre-built VxWorks BSP and project for the BSB design. Also covers VxWorks system image creation and using the Tornado 2.2.1 tools | |

| BSB 1: Linux 2.4 (EDK 8.2i SP2) | ||

| ml410_bsb_linux.zip | BSB generated ML410 design with Linux design files. Contains the results of running the tutorial flow. | |

| ml410_bsb_linux_overlay.zip | ML410 BSB Linux overlay source files with updated XMP and MSS files | |

| ml410_bsb_linux_bit_elf_ace.zip |

Contains EDK 8.2i SP2 Linux 2.4 ELF and ACE file, built with the existing EDK 8.2i SP1 bitstream | |

| ml410_bsb_linux_bsp.zip | Contains EDK 8.2i SP2 generated Linux BSP | |

| ml410_bsb_linux_bsp_proj_creation.pdf | Tutorial on how to start with an BSB hardware design and re-create the pre-built Linux BSP and project for the BSB design. Also covers Linux system image creation | |

| ml410_bsb_linux_kernel_config.zip | Generated configuration file that contains Linux kernel modifications | |

| BSB 1: RGMII | ||

| ml410_rgmii_plb_temac.zip | RGMII added to ML410 BSB 1 design | |

| ml410_rgmii_overlay.zip | RGMII overlay source files | |

| ml410_rgmii_bit_elf_ace.zip |

Contains EDK 8.2i SP1 / ISE 8.2i SP2 bit and ACE files, along with an ELF file | |

| ml410_bsb_rgmii_addition.pdf | Tutorial on how to add the RGMII PLB Core to the BSB 1 design | |

| BSB 2: DDR2 Design | ||

| ml410_bsb_ddr2_design.zip | An EDK 8.2i SP1 hardware design generated with Base System Builder (BSB) |

|

EDK IP:

|

|

|

| CPU: 300 MHz; PLB/OPB: 100 MHz DDR: 100 MHz, 32-bit PCI: N/A |

||

| ml410_bsb_ddr2_design_creation.pdf | Tutorial on how to use the EDK Base System Builder to create and use the ml410_bsb_ddr2_design | |

| BSB 2: DDR2 Workbench 2.5/VxWorks 6.3 (EDK 8.2i SP2) | ||

| ml410_bsb_ddr2_vxworks63.zip | BSB generated ML410 design (Networking, no PCI) with Workbench 2.5 VxWorks design files. Contains the results of running the tutorial flow | |

| ml410_bsb_ddr2_vxworks63_overlay.zip | BSB generated ML410 overlay source files (Networking, no PCI) with VxWorks and updated XMP and MSS files | |

| ml410_bsb_ddr2_vxworks63_bit_elf_ace.zip |

Contains EDK 8.2i SP2 VxWorks 6.3 ELF and ACE file, built with the existing EDK 8.2i SP1 bitstream | |

| ml410_bsb_ddr2_vxworks63_bsp.zip |

Provides a pre-built Workbench 2.5 vxWorks BSP generated by EDK 8.2i SP2 | |

| ml410_bsb_ddr2_vxworks63_proj.zip |

Provides the pre-built Workbench 2.5 vxWorks project used to create the VxWorks 6.3 system image | |

| ml410_bsb_ddr2_vxworks63_bsp_proj_creation.pdf | Tutorial on how to start with an EDK hardware design and re-create the pre-built VxWorks BSP and project for the BSB design. Also covers VxWorks system image creation and using the Workbench 2.5 tools | |

| BSB 2: DDR2 Tornado 2.2/VxWorks 5.5 | ||

| ml410_bsb_ddr2_vxworks.zip | BSB generated ML410 design (Networking, no PCI) with VxWorks design files. Contains the results of running the tutorial flow | |

| ml410_bsb_ddr2_vxworks_overlay.zip | BSB generated ML410 overlay source files (Networking, no PCI) with VxWorks and updated XMP and MSS files | |

| ml410_bsb_ddr2_vxworks_bit_elf_ace.zip |

Contains EDK 8.2i SP1 / ISE 8.2i SP2 bit and ACE files, along with a VxWorks 5.5 ELF file | |

| ml410_bsb_ddr2_vxworks_bsp.zip |

Provides a pre-built Tornado 2.2.1 VxWorks BSP generated by EDK 8.2i SP1. (Place in $WIND_BASE\target\config) | |

| ml410_bsb_ddr2_vxworks_proj.zip |

Provides the pre-built Tornado 2.2.1 VxWorks project used to create the VxWorks 5.5 system image. (Place in $WIND_BASE\target\proj) | |

| ml410_bsb_ddr2_vxworks_bsp_proj_creation.pdf |

Tutorial on how to start with an EDK hardware design and re-create the pre-built VxWorks BSP and project for the BSB design. Also covers VxWorks system image creation and using the Tornado 2.2.1 tools | |

| BSB 2: SGMII | ||

| ml410_sgmii_plb_temac.zip | SGMII added to ML410 BSB 2 design | |

| ml410_sgmii_overlay.zip | SGMII overlay source files | |

| ml410_sgmii_bit_elf_ace.zip | Contains EDK 8.2i SP1 / ISE 8.2i SP2 bit and ACE files, along with an ELF file | |

| ml410_bsb_sgmii_addition.pdf | Tutorial on how to add the SGMII PLB Core to the BSB 2 design | |

| BSB 2: SGMII Workbench 2.5/VxWorks 6.3 (EDK 8.2i SP2) | ||

| ml410_sgmii_vxworks63.zip | BSB generated ML410 design (Networking, no PCI) with Workbench 2.5 VxWorks design files. Contains the results of running the tutorial flow | |

| ml410_sgmii_vxworks63_overlay.zip | BSB generated ML410 overlay source files (Networking, no PCI) with VxWorks and updated XMP and MSS files | |

| ml410_sgmii_vxworks63_bit_elf_ace.zip |

Contains EDK 8.2i SP2 VxWorks 6.3 ELF and ACE file, built with the existing EDK 8.2i SP1 bitstream | |

| ml410_sgmii_vxworks63_bsp.zip |

Provides a pre-built Workbench 2.5 vxWorks BSP generated by EDK 8.2i SP2 | |

| ml410_sgmii_vxworks63_proj.zip |

Provides the pre-built Workbench 2.5 vxWorks project used to create the VxWorks 6.3 system image | |

| ml410_sgmii_vxworks63_bsp_proj_creation.pdf | Tutorial on how to start with an EDK hardware design and re-create the pre-built VxWorks BSP and project for the BSB design. Also covers VxWorks system image creation and using the Workbench tools | |

| EDK 8.2i SP1 Dual Processor Design (BSB 1 & BSB 2 Combined) Dual | VxWorks 6.3 | VxWorks 5.5 |

||

| ml410_dual_design.zip | An EDK 8.2i SP1 dual processor hardware design. | |

EDK IP:

|

|

|

EDK IP PPC405_1:

|

|

|

| ml410_dual_design.pdf | Tutorial on how to use the ml410_dual_design in EDK | |

| Dual Processor Design: Workbench 2.5/VxWorks 6.3 & Linux 2.4 (EDK 8.2i SP2) | ||

| ml410_dual_vxworks63.zip | Dual Processor ML410 design with VxWorks. Contains the results of running the tutorial flow | |

| ml410_dual_vxworks63_overlay.zip | Dual Processor ML410 overlay source files with VxWorks and updated XMP and MSS files | |

| ml410_dual_linux_vxworks63_overlay.zip | Updates the Dual processor design to run Linux on ppc405_0. See the appendix of the presentation below for details (Linux requires EDK 8.2i SP2) | |

| ml410_dual_vxworks63_bit_elf_ace.zip |

Contains EDK 8.2i SP2 VxWorks 6.3 ELF and ACE file, built with the existing EDK 8.2i SP1 bitstream | |

| ml410_dual_vxworks63_bsp.zip | Pre-built Workbench 2.5 VxWorks BSPs generated by EDK 8.2i SP1 for each processor in the dual processor design. (Place in $WIND_BASE\target\config) | |

| ml410_dual_vxworks63_proj.zip | Pre-built Workbench 2.5 VxWorks projects for both processors. Used to create the VxWorks 5.5 system image. (Place in $WIND_BASE\target\proj) | |

| ml410_dual_vxworks63_bsp_proj_creation.pdf |

Tutorial on how to start with an EDK hardware design and re-create the pre-built VxWorks BSP and project for the Dual design. Also covers VxWorks system image creation and using the Workbench 2.5 tools | |

| Dual Processor Design: Tornado 2.2/VxWorks 5.5 & Linux 2.4 | ||

| ml410_dual_vxworks.zip | Dual Processor ML410 design with VxWorks. Contains the results of running the tutorial flow | |

| ml410_dual_vxworks_overlay.zip | Dual Processor ML410 overlay source files with VxWorks and updated XMP and MSS files | |

| ml410_dual_linux_overlay.zip | Updates the Dual processor design to run Linux on ppc405_0. See the appendix of the presentation below for details (Linux requires EDK 8.2i SP2) | |

| ml410_dual_vxworks_bit_elf_ace.zip |

Contains EDK 8.2i SP1 / ISE 8.2i SP2 bit and ACE files, along with a VxWorks 5.5 ELF file | |

| ml410_dual_vxworks_bsp_0.zip ml410_dual_vxworks_bsp_1.zip |

Pre-built Tornado 2.2.1 VxWorks BSPs generated by EDK 8.2i SP1 for each processor in the dual processor design. (Place in $WIND_BASE\target\config) | |

| ml410_dual_vxworks_proj_0.zip ml410_dual_vxworks_proj_1.zip |

Pre-built Tornado 2.2.1 VxWorks projects for both processors. Used to create the VxWorks 5.5 system image. (Place in $WIND_BASE\target\proj) | |

| ml410_dual_vxworks_bsp_proj_creation.pdf |

Tutorial on how to start with an EDK hardware design and re-create the pre-built VxWorks BSP and project for the Dual design. Also covers VxWorks system image creation and using the Tornado 2.2.1 tools | |

| Board and Component Data | |

| ML410 Links | |

| ML410 Overview | ML410 Overview Page |

| ML410 User's Guide | |

| ug085.pdf | ML410 User's Guide |

| Schematics and Printed-Circuit Board | |

| Rev E | |

| ml410_revE.pdf | ML410 Schematics |

| 1203r03.zip | ML410 Viewdraw Schematics |

| ML410_REV_E_PCB.zip | ML410 Pads Database Files |

| 1499r04.pdf | ML410 Gerber Files |

| XILINX_ML410_REVE_ASSY.zip | ML410 Gerber Files |

| Bill of Materials | |

| ml410_toplevel_bom.xls | ML410 Top Level BOM Spreadsheet |

| 0431410-01_ROHS.xls | ML410 RevE BOM Spreadsheet |

| Personality Module Interface | |

| ug142.pdf | Personality Module Interface Specification |

| Data Sheets | |

| ML410 Data Sheets | PDF data sheets for components used in ML410 |

| CompactFlash Image | |

| 0570040r04_CF_FAT.zip | ACE files from the FAT Partition on the CompactFlash |

| 0570040r04.zip (158 MB) md5sum.txt |

Initial release CF image. Use the tools in the Utilities section below with this image. The ml410_readme.txt has important details on using the CompactFlash disk created from this image. |

| Utilities and Patches | |

| ml410_cf_reimage.pdf |

Instructions on how to image the CompactFlash Caution: Follow instructions carefully |

| cf_image_tools.zip | Cygwin Disk Tools for installing the image |

| xcsc.zip | Windows application used to compute CRC32 value of "dd" disk image files. XCSC is an small freeware utility for calculating the checksum values of files The supported algorithms include CRC32 (Cyclic Redundancy Code), MD5 (Message Digest number 5) and SHA-1 (Secure Hash Algorithm). For more info on XCSC, please visit http://www.irnis.net |

| mkdosfs.zip | Windows utility to format your CF with a DOS partition for use with System ACE CF Controller Use the following: mkdosfs -v -F 16 <your CF drive letter> More details about this utility can be found at http://www.mager.org/mkdosfs/ |

| XAPP732 | MGT: New DCM parameters for Virtex-4 |

| 。/TD> | MGT: Using a Null Tile PCore for MGTs |